1.CMOS门电路

nmos高电压导通,pmos低电压导通

PMOS的电路符号栅极处小圈圈,表示低电平有效的

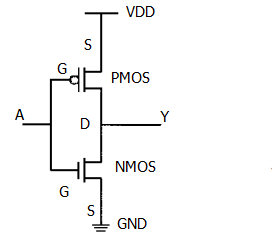

①CMOS非门

1)当输入信号A=1时,PMOS关断,NMOS打开,输出信号Y的电压相当于GND的电压,也就是Y=0;在这个过程中,从VDD到GND这一个供电回路都没有导通,因此理论不存在电流从VDD流到GND,因此功耗为0.

2)当输入信号A=0时,PMOS打开,而NMOS关闭,输出信号Y=VDD=1,但是从VDD到GND这一个供电回路也没有导通,因此理论上也不存在电流从VDD流到GND,因此功耗也为0。

3)因此可以得出,理论上反相器进行传输信号时,没有功耗(实际功耗极低),这就是为什么使用CMOS工艺的原因。

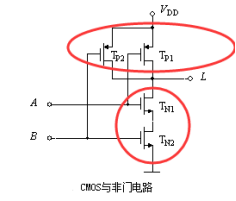

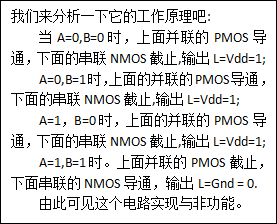

②(二输入)CMOS与非门(NAND):

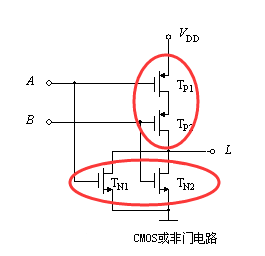

③(二输入)CMOS或非门(NOR)

2.CMOS的功耗表示

功耗是单位时间内消耗的能量,在数字系统中的功耗主要包括静态功耗和动态功耗,我们将从CMOS电路角度分析静态功耗和动态功耗。

CMOS的静态功耗:当CMOS不翻转/不工作时的功耗。在CMOS都不工作时,也就是晶体管都处于截止状态的时候,从VDD到GND并不是完全没有电流流过的,还是有些微电流从电源流到地,这个静态电流Idd称为电源和地之间的漏电流,跟器件有关(至于漏电流是怎么引起的,这里就不再阐述了)。初中的时候,我们就学过P=UI,静态功耗可以这样表示 :

Ps = IddVdd.

CMOS的动态功耗:是信号在0和1变化之间,电容充放电所消耗的功耗。我们知道,不仅仅CMOS器件有寄生电容,导线间也有电容。将电容C充电到电压Vdd所需要的能量CVdd^2。如果电容每秒变换f次(也就是电容的切换频率为f,在一秒内,电容充电f/2次,放电f/2次),由于放电不需要从电源那里获取功耗,因此动态功耗就可以这样表示:

Pd = 1/2 CVdd^2f 即:

PS:上面主要是列举了一些主要的功耗,比如动态功耗中除了翻转时电容消耗功耗外,还有在栅极信号翻转的时候PMOS和NMOS同时导通引起的短路功耗。