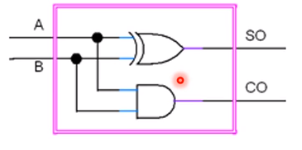

一、半加器

原理图:

代码实现:

//半加器,assign相当于连续赋值

module halfadder(a,b,SO,CO);

input a,b;

output SO,CO;

assign SO=a^b;

assign CO=a&b;

endmodule

仿真波形:

二、锁存器的原理图实现

逻辑表达式:Qn+1=CLK·D+CLK‘·Qn

电路原理图:

仿真波形:

三、8位加法器

逻辑表达式:

Ci+1=AiBi+Ai⊕Bi·Ci

Di+1=Ai⊕Bi⊕Ci

代码实现:

//8位加法器

module ADDER8(A,B,CIN,DOUT,COUT);

input [7:0]A,B;

input CIN;

output COUT;

output [7:0]DOUT;

wire [8:0]DATA;

//计算过程

//assgin {COUT,DOUT}=CIN+A+B;

assign DATA=CIN+A+B;

assign COUT=DATA[8];

assign DOUT=DATA[7:0];

endmodule

仿真波形:

四、Verilog语法重点:

数据流建模:用assign语句时

assign右边的参数一定要被定义成wire类型

行为级建模(过程语句):用initial/always语句

里面的参数一定要被定义成reg类型

顺序执行:begin end

并行执行:fork join

阻塞型赋值:=

非阻塞型赋值:<=