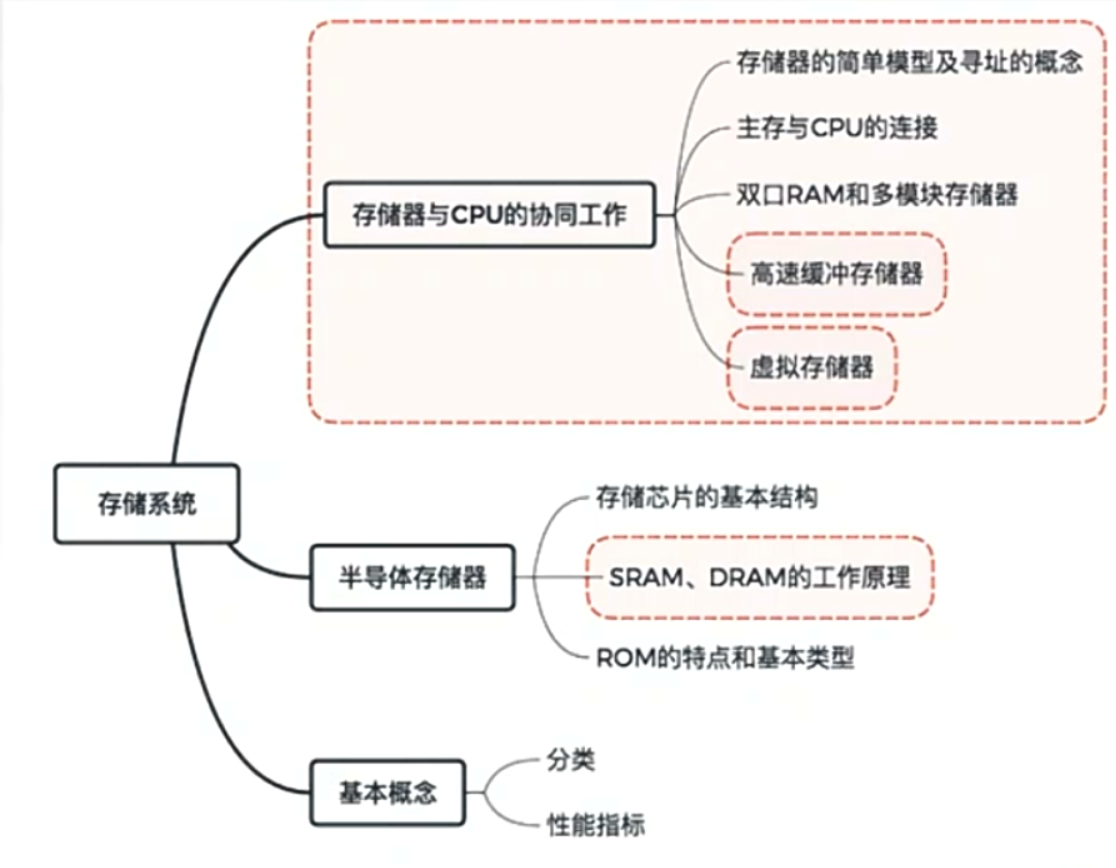

基本概念

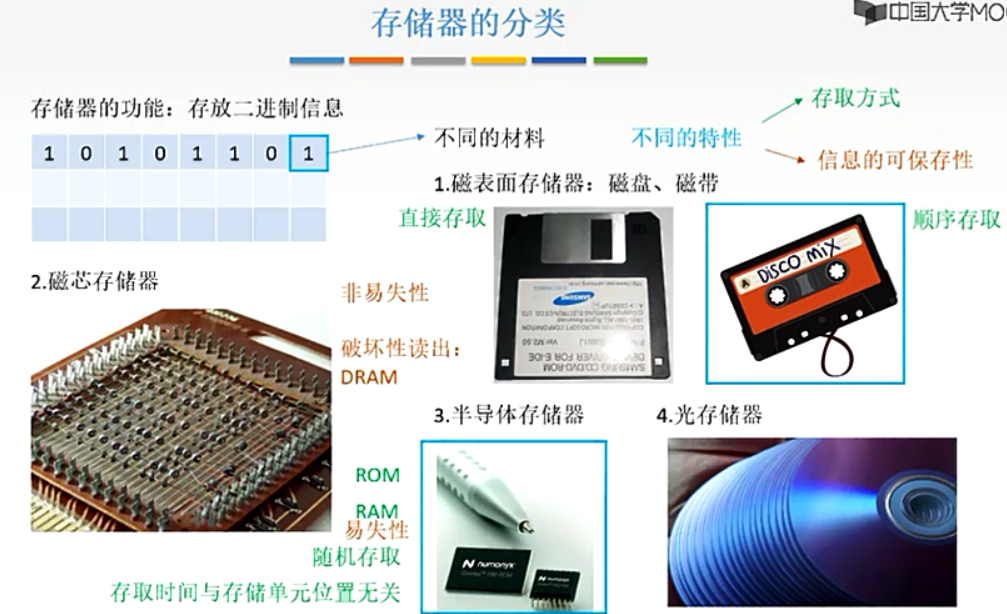

存储器功能:存放二进制信息

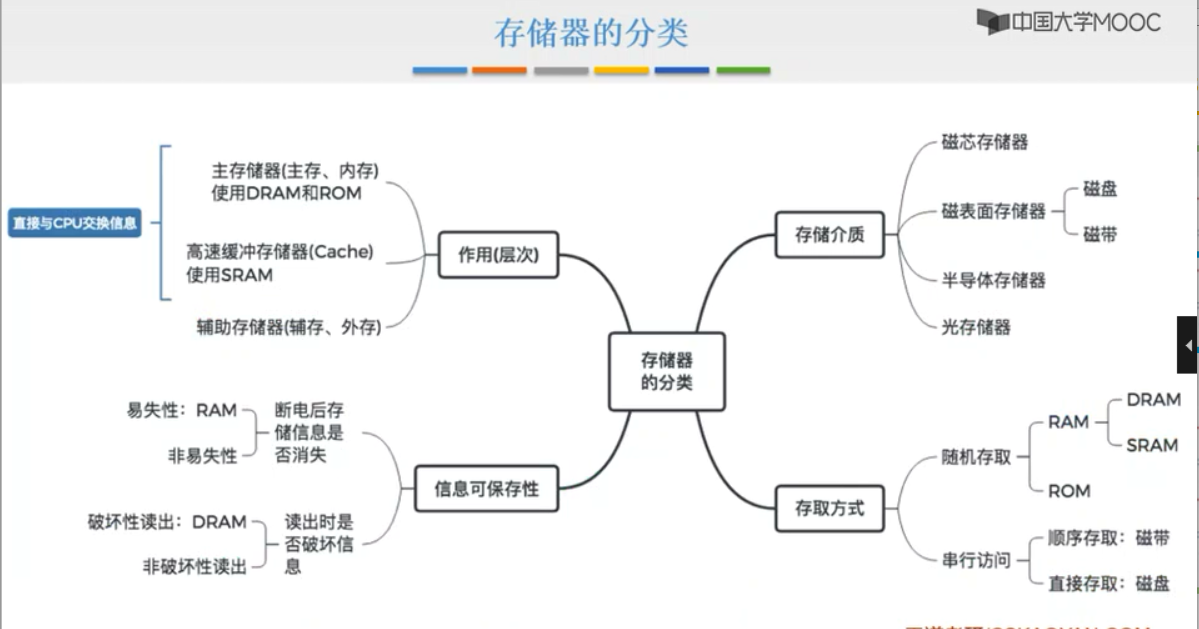

分类

根据作用(层次分类)

高速缓冲存储器(cache)

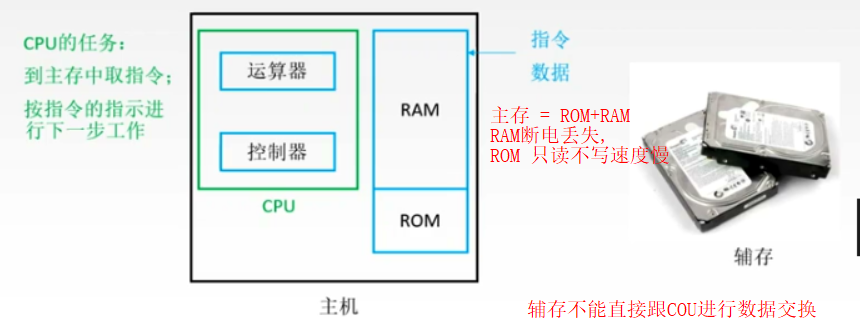

主存储器(主存,内存)

辅助存储器(辅存,外存)

根据材料分类

1.磁表面存储器 :磁盘磁带

2.磁芯存储器 :DRAM

3.半导体存储器 :ROM,RAM

4.光存储器 :光存储器

材料不同特性不同

存储方式

1.磁盘(直接存取) 磁带(顺序存取)

2.DRAM

3.ROM,RAM(随机存取)

4.光存储器

信息的可保存性

断电后是否容易消失:容易失去RAM

读出时是否破坏信息:破坏性读出DRAM

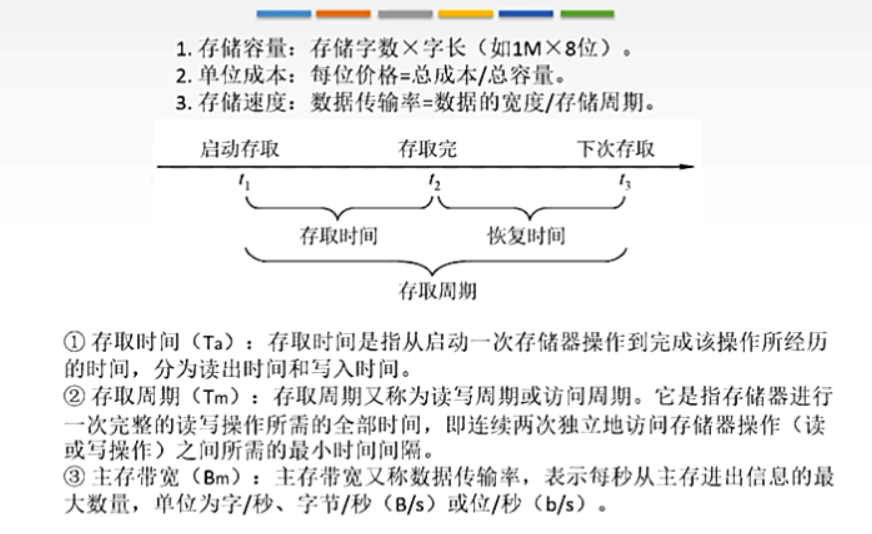

性能指标

存储容量

存储容量 = 存储单位的数量 × 字长

比如:1M × 8位(bit)

个人理解: 存储容量 = 地址总线数 × 数据总线数

单位成本

单位成本 = 总成本 / 总容量

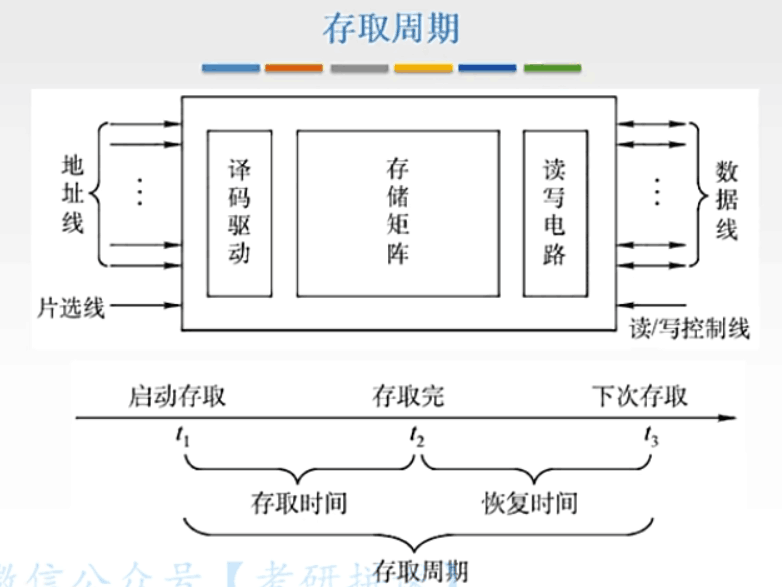

存储速度(存储时间Ta/存储周期Tm/主存带宽Bm)

存储时间Ta

存储时间:完成一次操作的时间

比如完成的一次读出 或 写入

存储周期Tm

存储周期 = 存储时间 + 恢复时间

理解:两次操作中之间的最小时间间隔

主存带宽Bm

主存带宽,又名存储数率

表示每秒从主存进出信息的最大数量

最大通路数,就像烤冷面一样,是由好多条好多条构成的一板

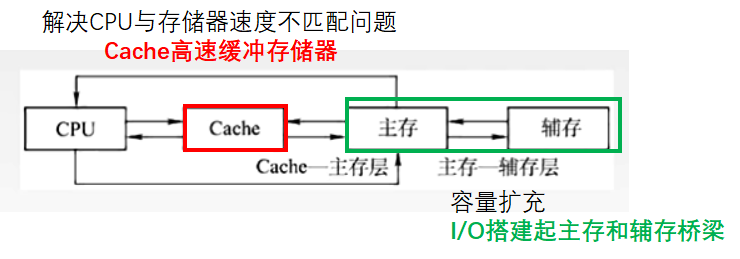

层次结构

分为两层 cache-主存一层 ,主存-辅存一层

半导体存储器

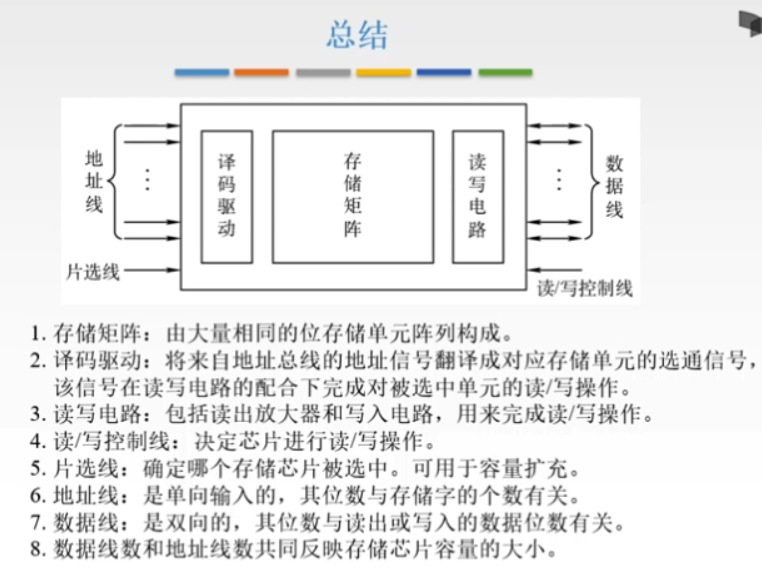

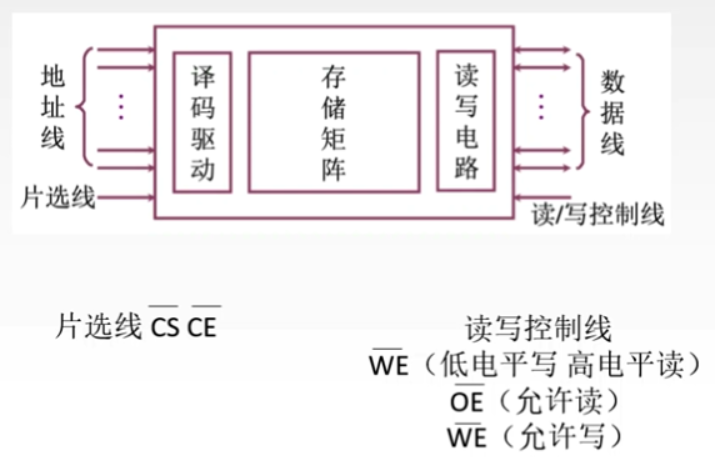

存储芯片的基本结构

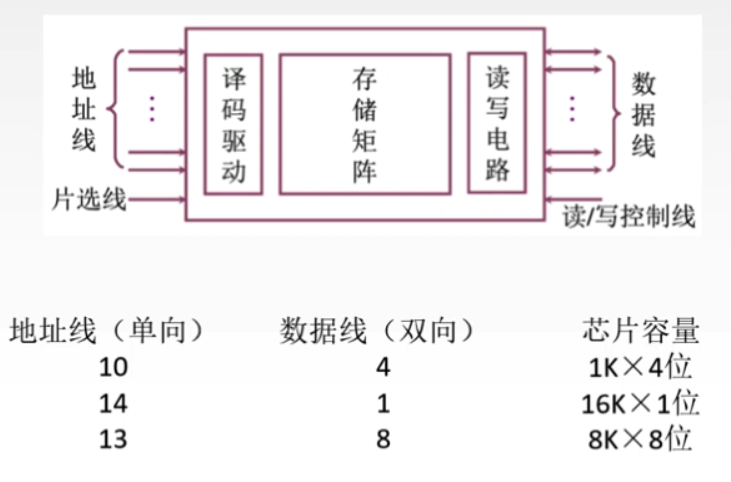

容量计算

2^10 = 1k

2 ^ 14 = 1k × 2^4 =16K

选择控制

选片 #CS #CE

控制读写 #WE /#OE#WE

单信号控制读写 #WE(低电平写,高电平读)

双信号控制读写 #OE(允许读) #WE(允许写)

RAM的分类

#SRAM,DRAM的工作原理

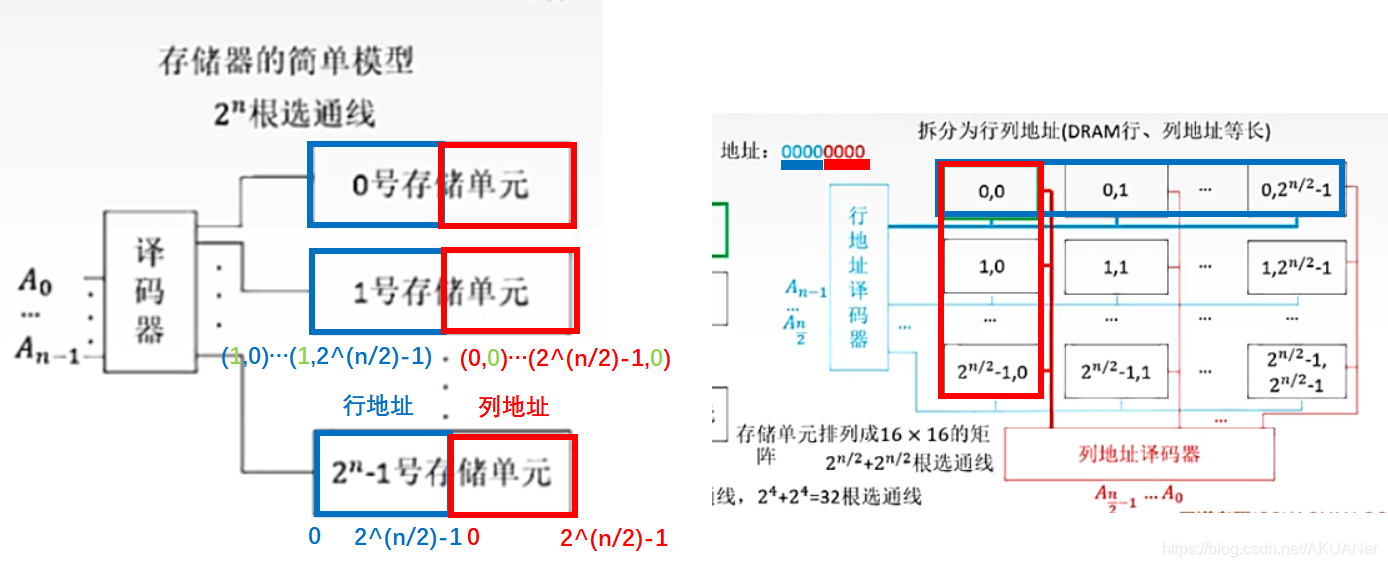

简单模型改进行列地址

DRAM的刷新

RAM的读写周期

22//后期补档

存储系统ROM

存储器与CPU协同工作

存储器的简单模型

存储器简单模型:

实际中MAR,MDR是在CPU里,理论上是在主存里

存储器地址连线 (A地址线,D数据线)

主存内存扩展

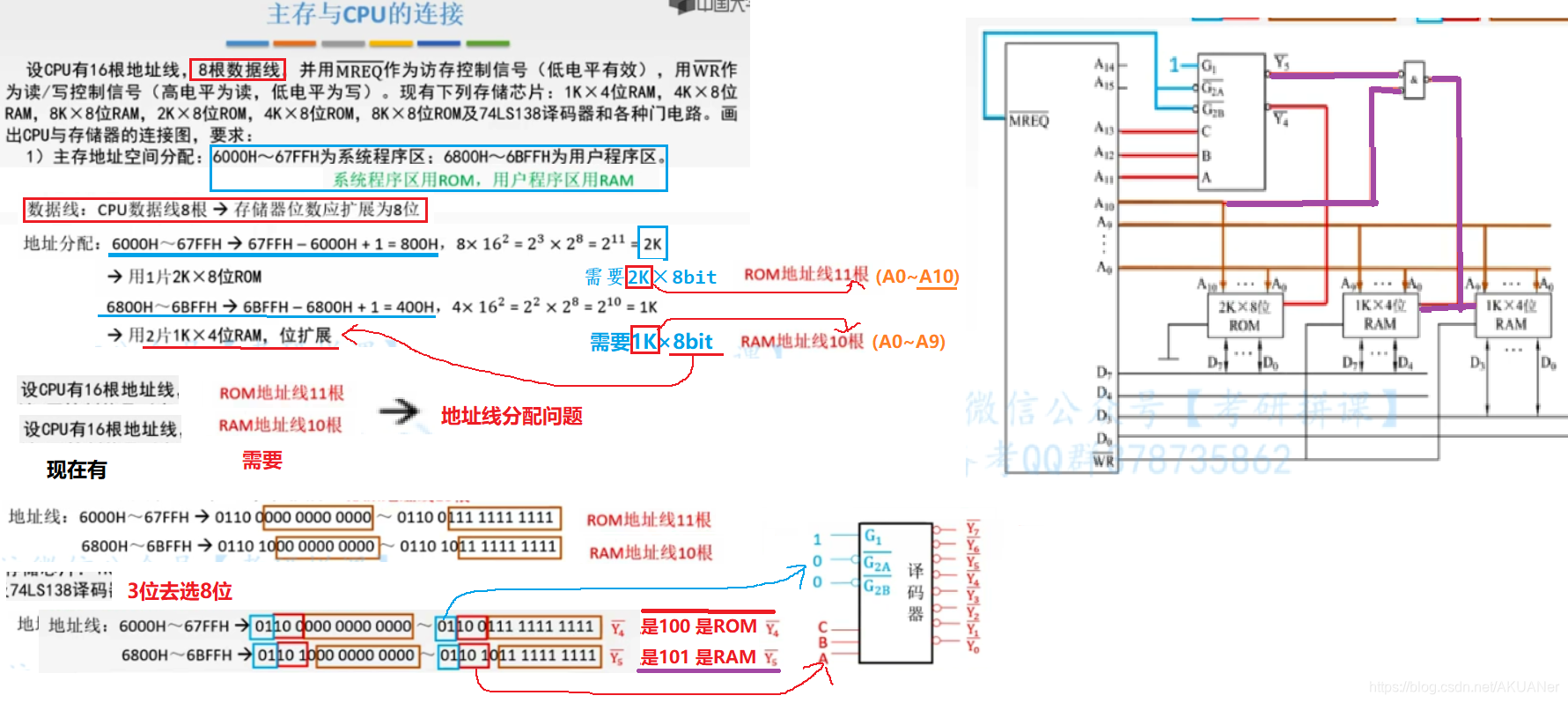

主存与CPU的连接

子扩展 / 位扩展 / 字位扩展

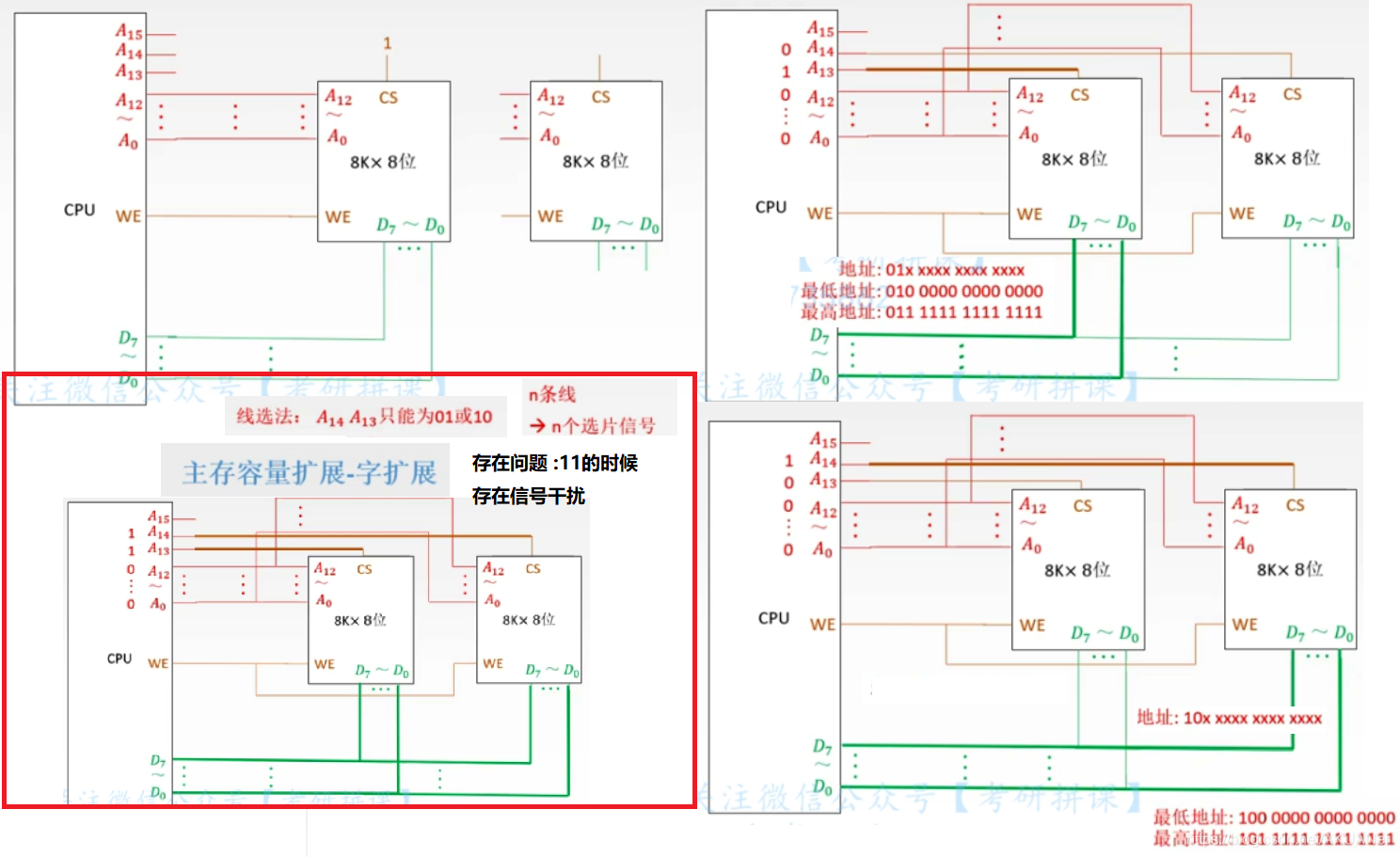

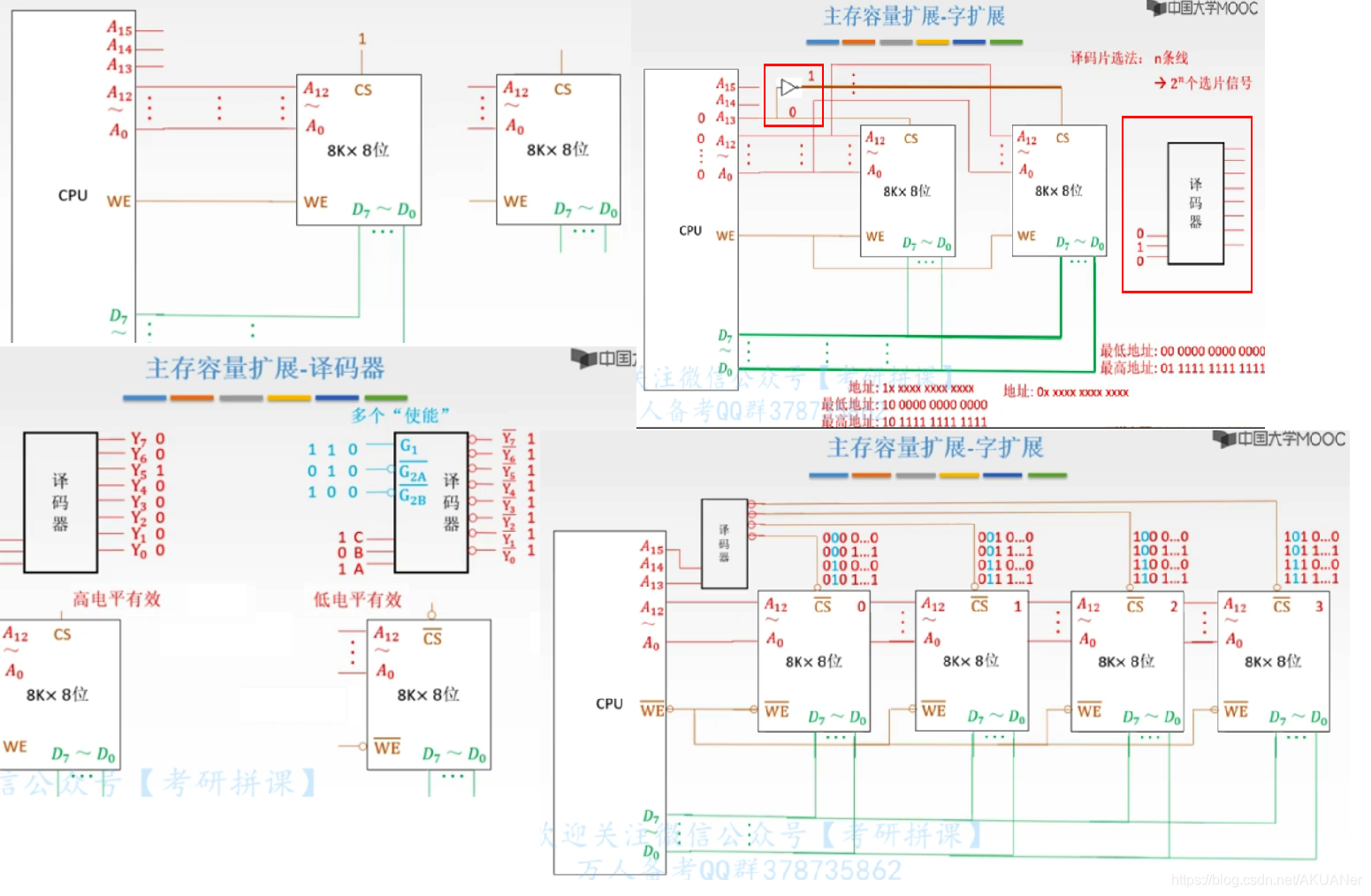

字扩展

线选法

译码片选法

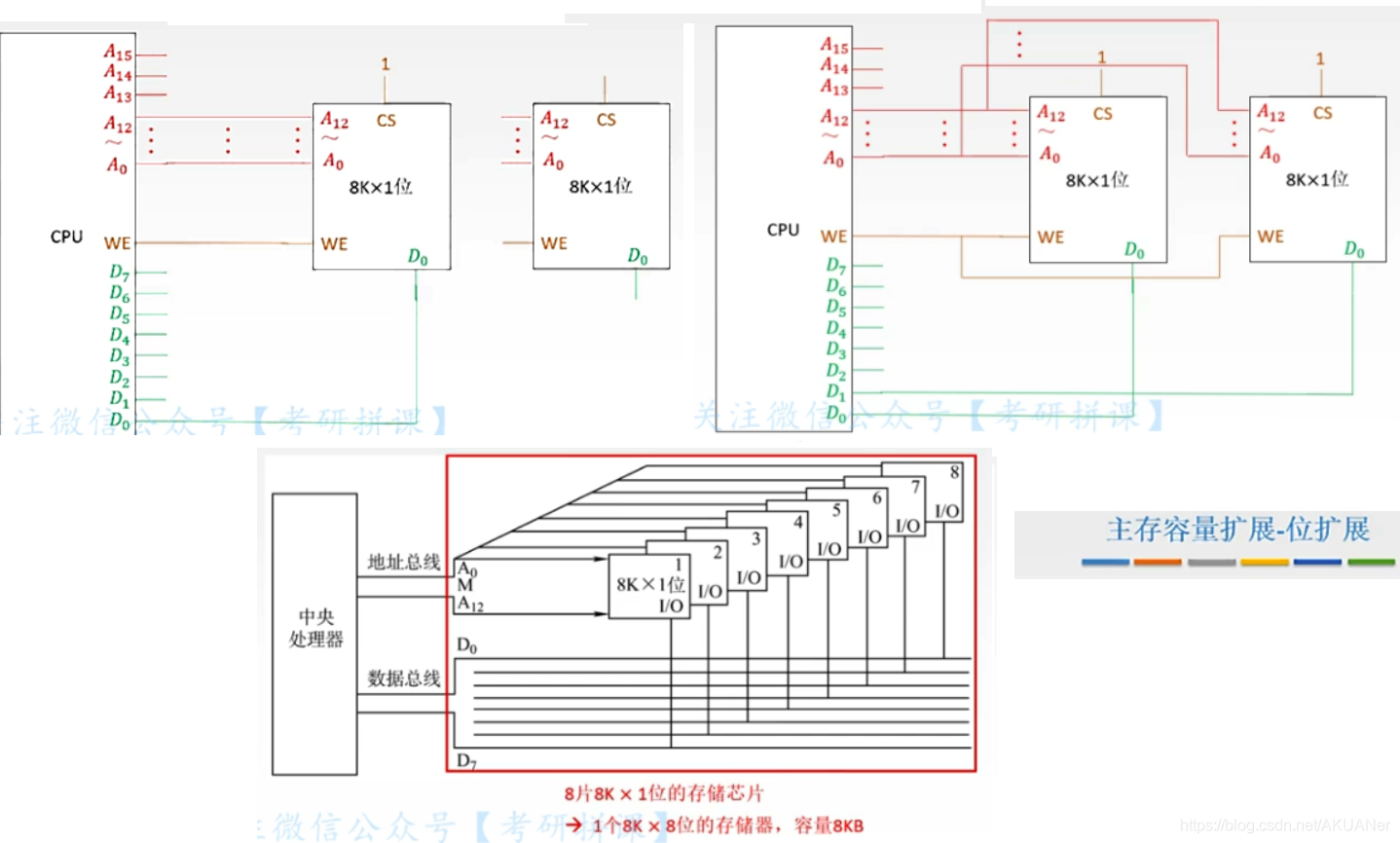

位扩展

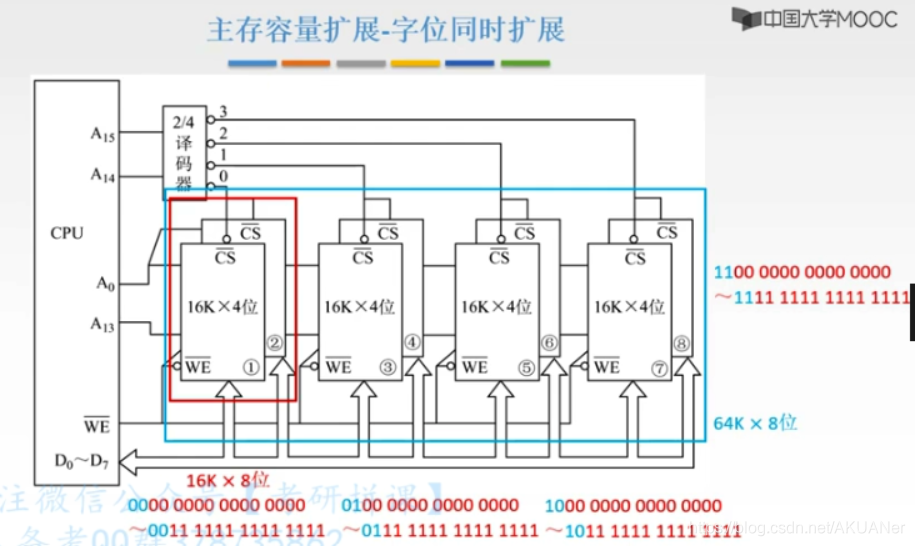

字位扩展

如何提高访问/存储的速度

存储周期

提高速度的办法引入: 双口RAM和多模块存储器

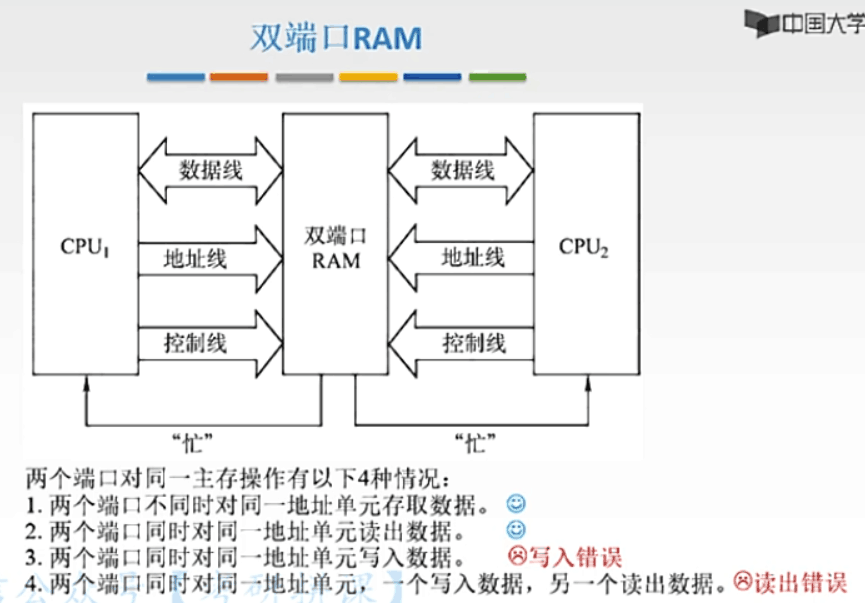

双端口 物理上的并行

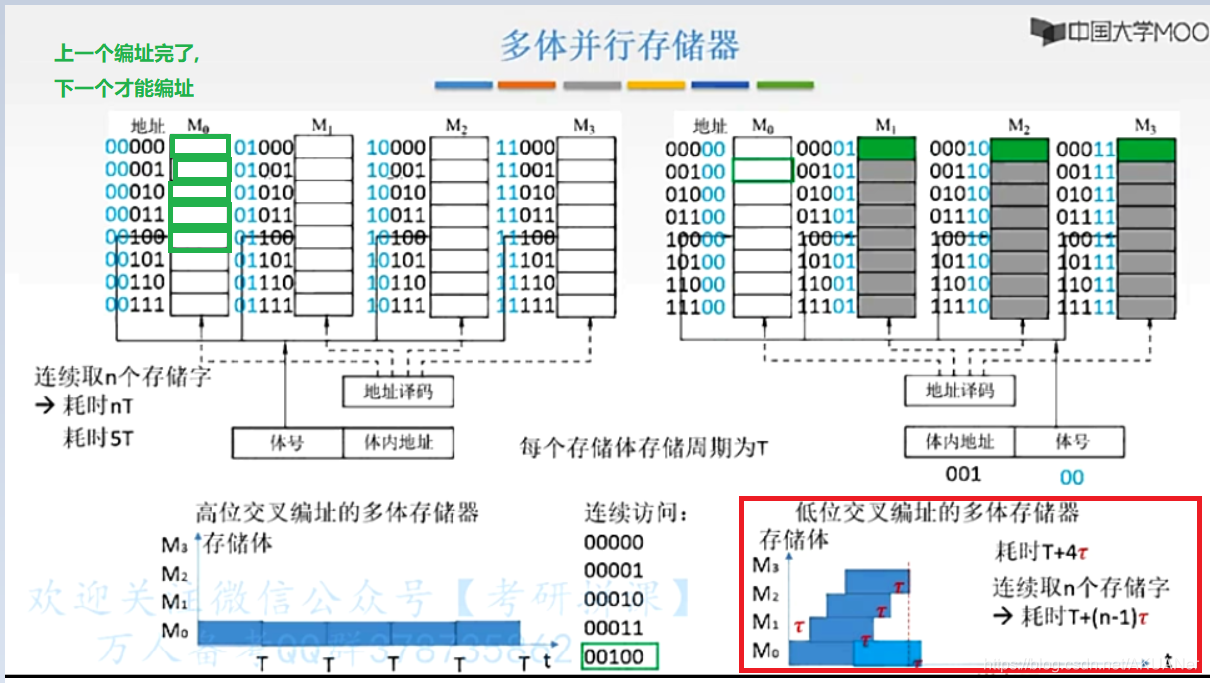

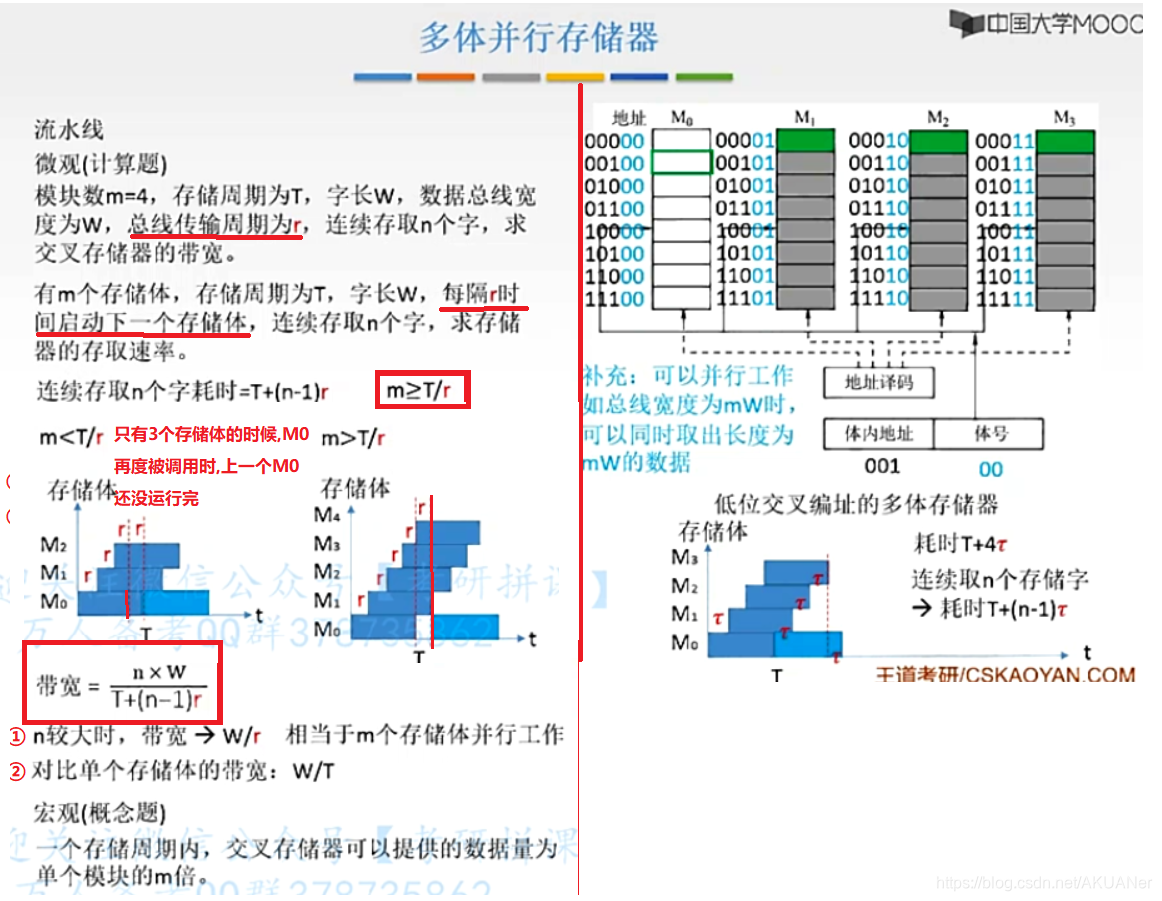

多模块 时间上的并行

双端口RAM

双端口会给两个CPU都有个"忙"的标记,防止出现同时写入之类的情况

多模块存储器

单体多字存储器 (略) 和 多体并行存储器

高速缓冲存储器⭐

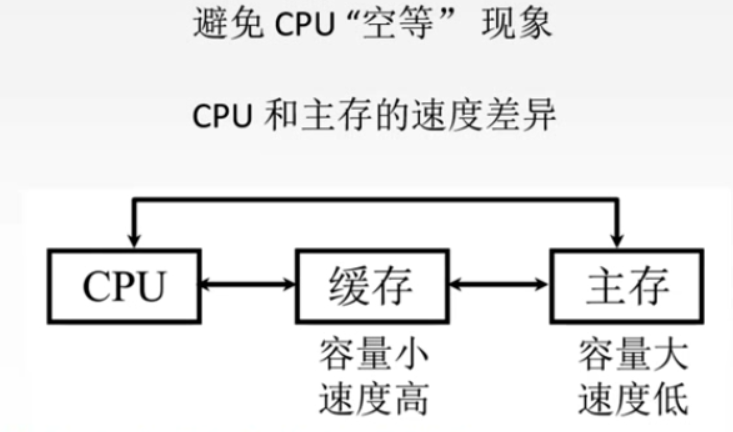

cache出现的原因: 避免速度差造成的拥堵

时间局部性:未来要用到的信息可能是我现在正在用的信息

空间局部性:未来要用的信息,从存储角度说,可能在我正在用的信息的附近

所以我把正在使用的信息,和附近的信息都放入cache

单位:块

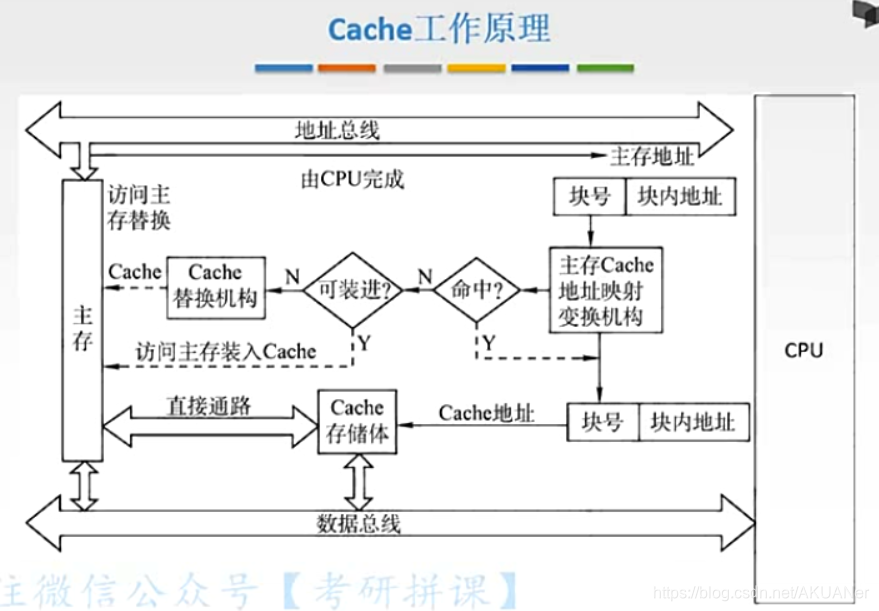

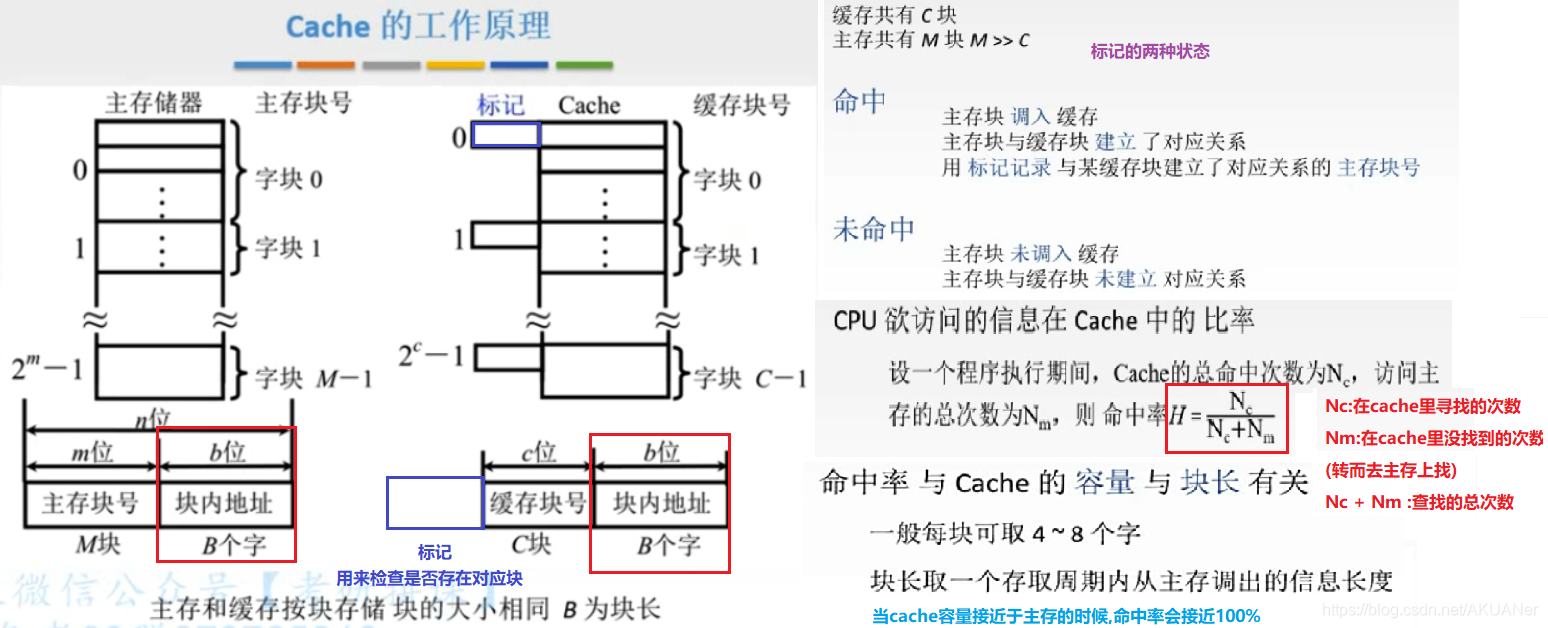

Cache 工作原理

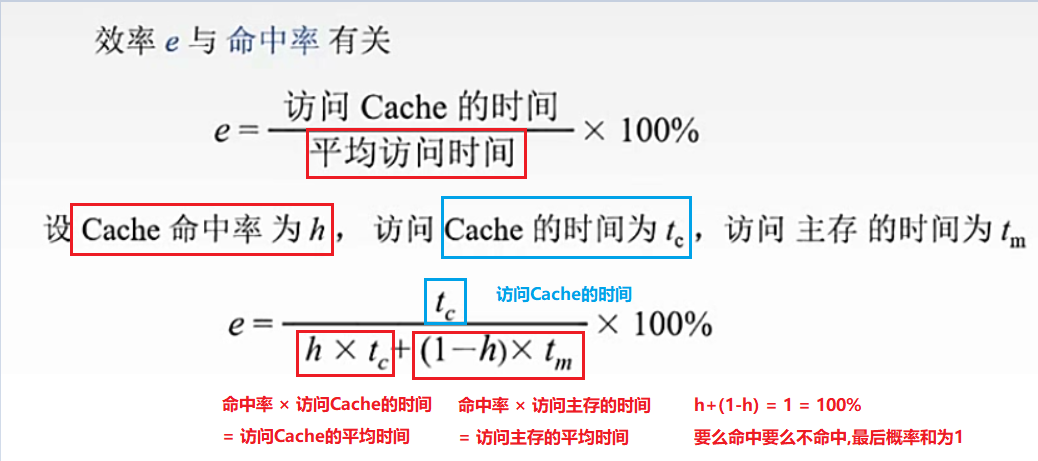

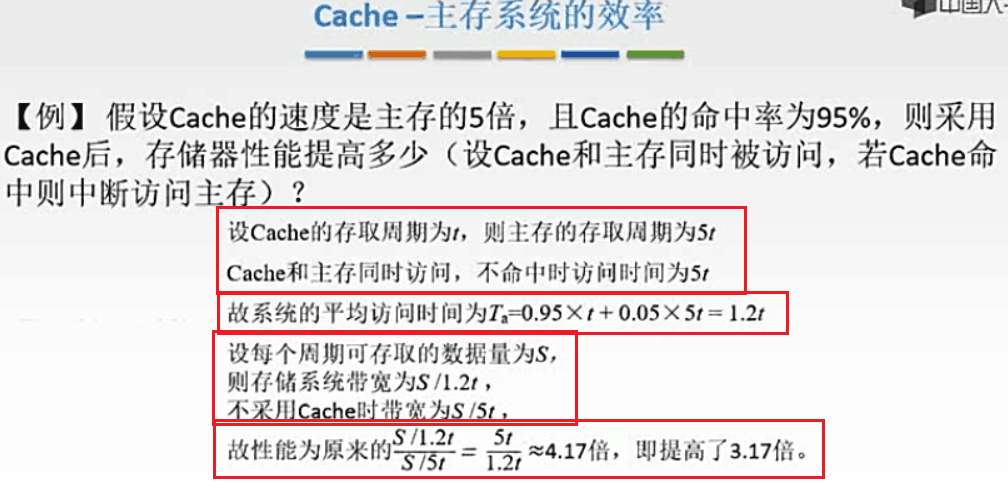

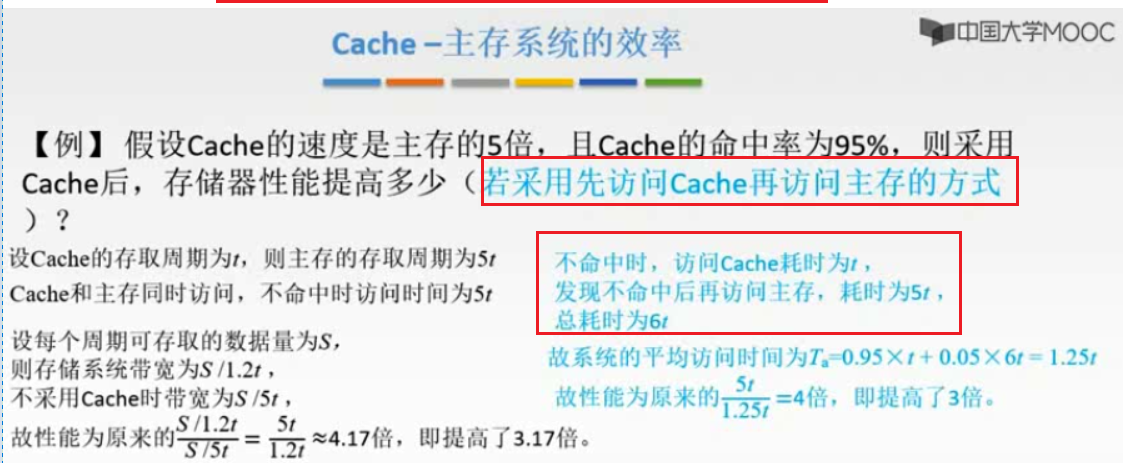

Cache性能分析

例题1: 同时访问Cache和主存

例题2: 先访问Cache再访问主存

Cache与内存的地址映射

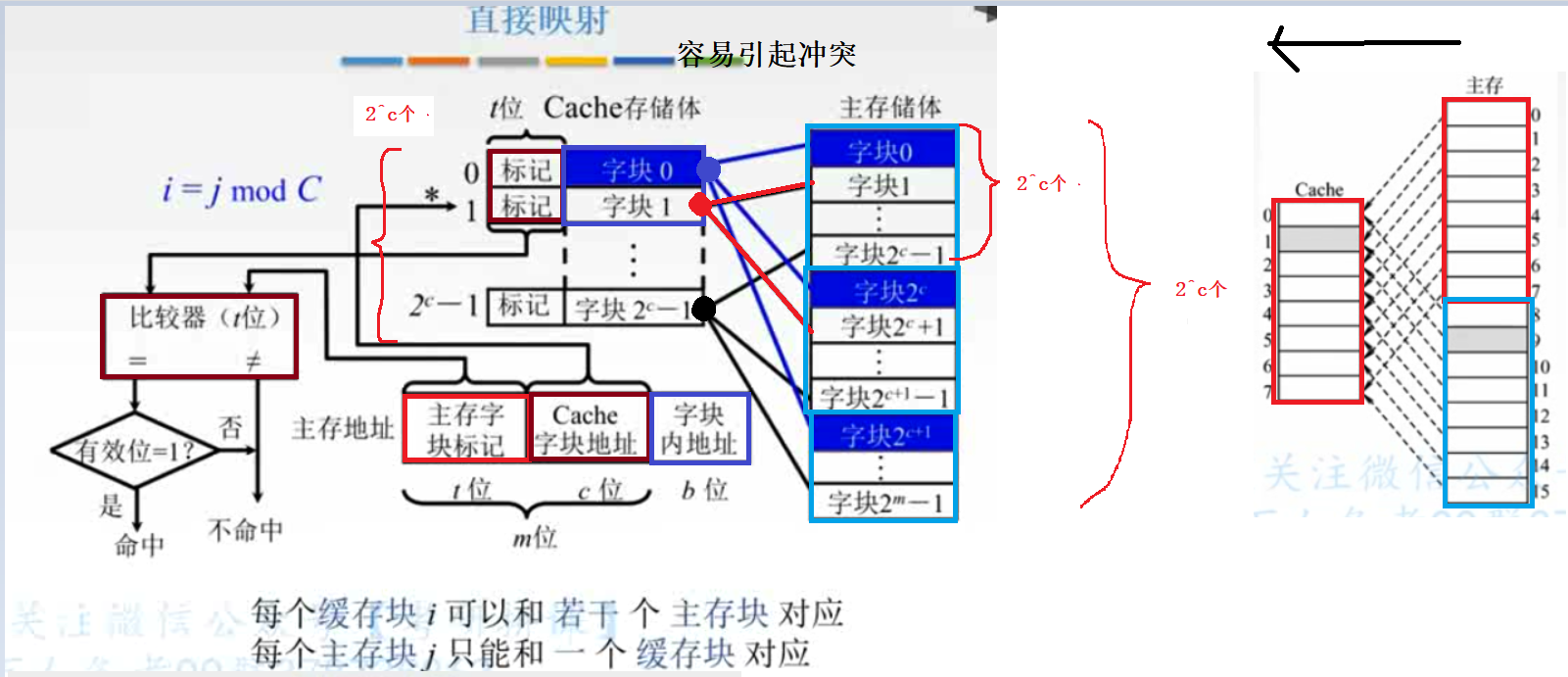

直接映射

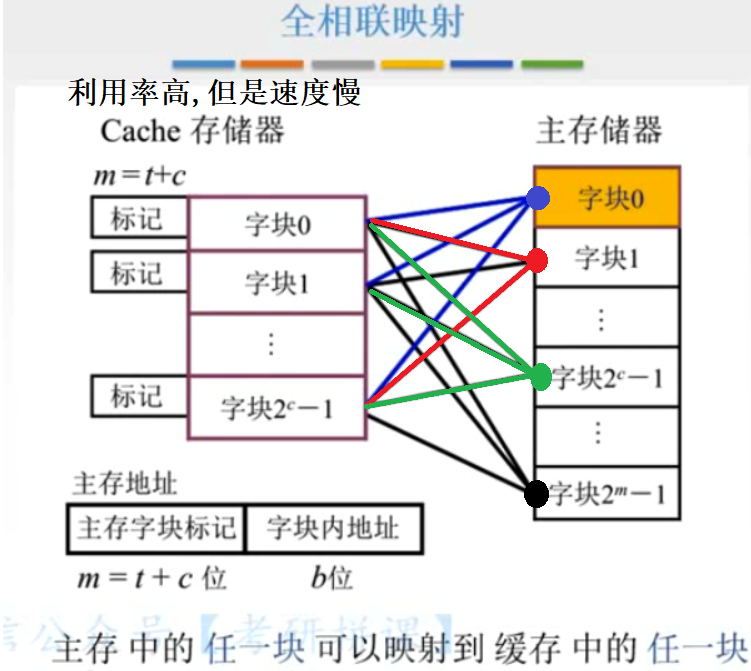

全相联映射

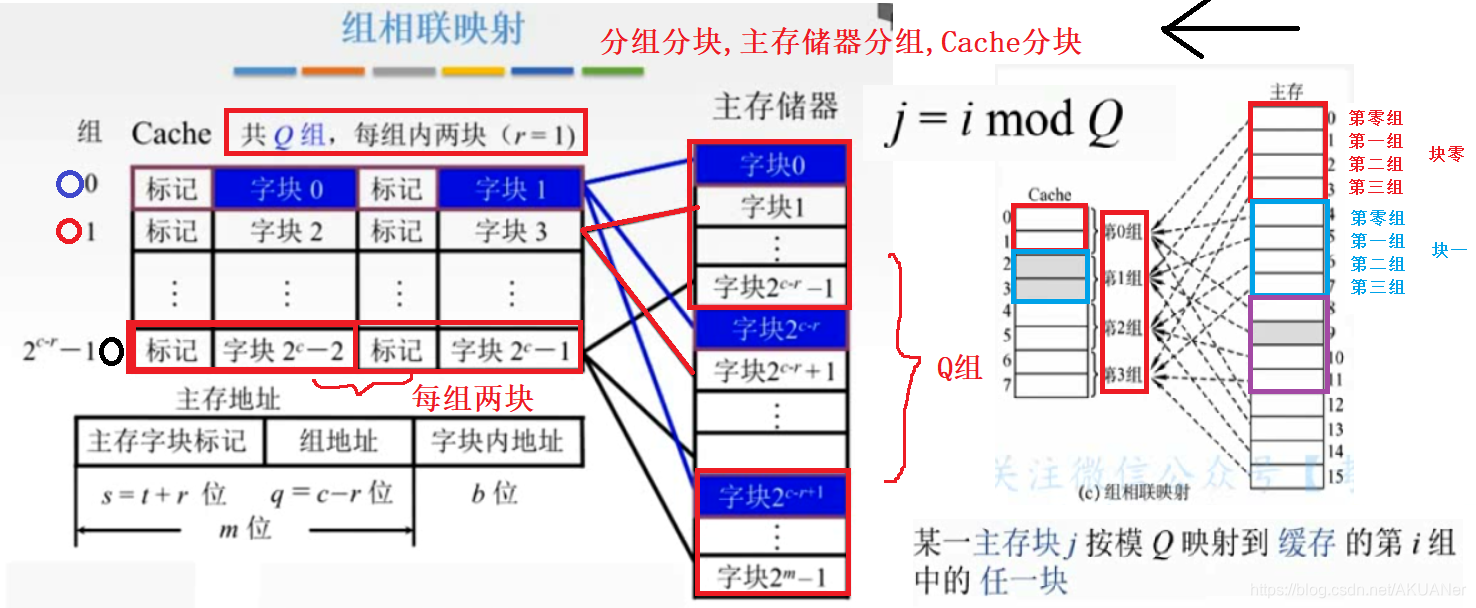

组相联映射