5 可综合的语法子集

其他

2020-04-21 15:33:47

阅读次数: 0

- 可综合的语法

- 硬件能够实现的一些语法,

- 这些语法能够被EDA工具支持

- 能通过编译最终生成用于烧录到FPGA器件中的配置数据流。

- 无论Verilog还是VHDL,可综合的子集都很小。

- 如何用好这些语法、什么样的代码风格更适合于硬件实现,

- 下面是常用的RTL级 Verilog语法及其简单用法描述。

- Verilog和C相似,但是笔者担心过多地混淆C语言和 Verilog会让初学者误入歧途,

- 两者在本质上很大差异,

- 设计思想和实现载体上存在着很大差异,

- 尽可能多去了解和比对相关语法最终实现的硬件电路,

- 尽快从软件式的顺序思维中解脱,更好理解硬件式的并行处理

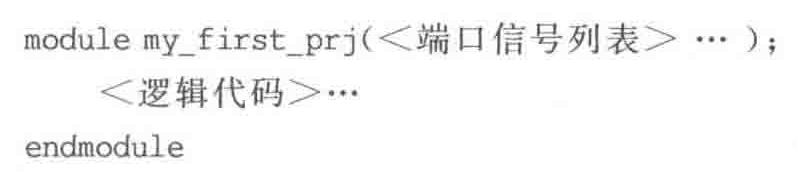

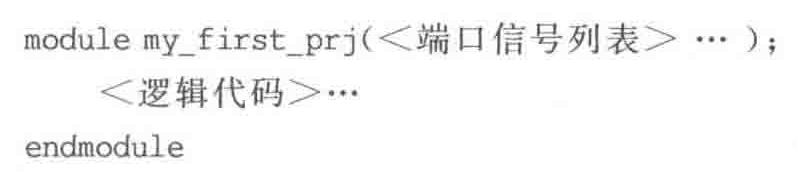

模块声明类语法: module… endmodule

- 每个verilog文件都出现模块声明类语法,它是一个固定的用法,所有的功能实现语法最终都应该包括在“…”中。

端口声明: input, output, inout

- 每个module都有输入/输出的信号用于和外部器件或其他module通信

- 这些信号归3类,即输入信号、输出、和双向

- 最常见的3种端口申明实例如下:

- 1 bit的名称为clk的输入信号

- wire类型的1 bit的名为rst_n的输入信号

- 8 bit的名称为data_in的输入信号

三:参数定义: parameter

- Parameter申明一些常量,便于模块的移植或升级时的修改。

- 一个基本的module通常一定包括 module… endmodule语法和任意两种端口申明(通常所设计的模块一定是有输入和输出的)

- parameter则不一定,但对一个可读性强代码也不可少

- 这样一个基本的 module如下:

四、信号类型:wire,reg等

- 图2.1,

- 定义两个寄存器(reg)锁存当前的输入din。

- 每个时钟clk上升沿到来时,reg都会锁存到最新的输入数据,

- wire就是这两个reg间直接的连线

- Input或 Inout只能是wire,

- output可wire或reg。

- 虽然在代码中可以定义信号为wire或reg,但实际的电路实现是否和预先的一致还要看综合工具的表现。

- reg信号常会被综合为一个寄存器,但前提是reg信号必须是在某个由特定信号边沿敏感触发的 always语句中被赋值

发布了597 篇原创文章 ·

获赞 301 ·

访问量 8万+

转载自blog.csdn.net/zhoutianzi12/article/details/105643325