- 触发器只是在锁存器上增加了一个触发信号输入端。

- 只有当触发信号到来时,触发器才能按照输入的置1、置0信号置换成相应的状态,并保持下去。将这个触发信号称为时钟信号(CLOCK),记作CLK。

- 当系统中的多个触发器需要同时工作时,就可用同一个时钟信号作为同步控制信号了。

- 触发器可分为 电平触发、边沿触发、脉冲触发。

【 1. 电路结构 】

即把与非门SR锁存器低电平有效的结构改为了高电平有效且又外加一个输入控制端。

【 2. 工作原理 】

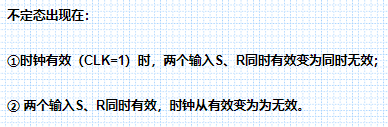

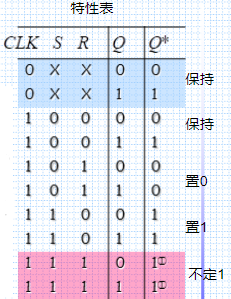

- CLK=1时,对电路无影响,表现为SR锁存器功能,

- CLK=0时,G3、G4的输出始终保持在1状态,S、R信号无效,电路处于“锁存状态”,锁存的是CLK变为0前瞬间Q、Q’的状态,令Q、Q’输出不变。

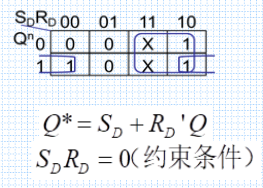

【 3. 功能描述 】

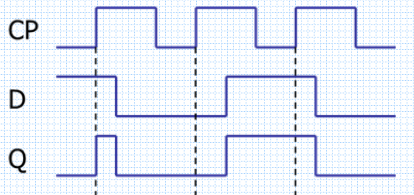

【 4. 时序图 】

初态Q=0

【 5. 带异步置位、复位端的SR电平触发器 】

异步: 不受时钟信号控制。

异步置位端(置1): S’D,低电平有效。S’D=0时,Q=1。

异步复位端(置0): R’D,低电平有效。R’D=0时,Q’=1。

(即若让时钟信号发挥作用,应使 S’D=R’D=1。)

无论CLK、S、R任何情况,令S’D、R’D置0即可单独地令Q或Q’置1。

若想让S’D、R’D无效(为1)后也一直保持设置前的状态,则应令CLK=0。

【 6. 电平D触发器 】

输出Q始终跟随输入D的变化,即Q=D

令CLK=0,即可“锁存”CLK变为0前瞬间Q的状态,令Q输出不变。