| 学习笔记总目录 |

|---|

| 专题一:工作两年再学习嵌入式系列文章-目录 |

| 专题二:直流无刷电机控制从0到1系列文章-目录 |

| 专题三:硬件从0到1从0到1系列文章-目录 |

| 专题四:从0到1写嵌入式操作系统系列文章-目录 |

2.1.概述

Cortex-M3内核是ARM公司开发的CPU内核,它是32位RISC处理器,哈佛结构,3级流水线,内嵌中断向量控制器和SysTick定时器。完整的MCU芯片集成了Cortex-M3内核以及其他组件。这些其他组件通常由IC制造商设计开发。

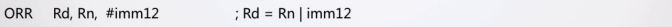

2.1.1.工作模式和权限级别

- 处理模式:执行中断服务程序等异常处理(一直具有特权)。

- 线程模式:在执行普通的应用程序代码时(特权和非特权都有可能,具体取决于CONTROL寄存器的设置)。

软件可以将处理器从特权线程模式切到非特权线程模式,但无法将自身从非特权切到特权模式,处理器必须借助异常机制才能这样切换。

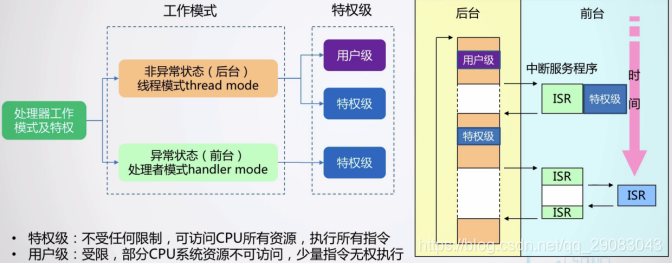

2.1.2.通用寄存器

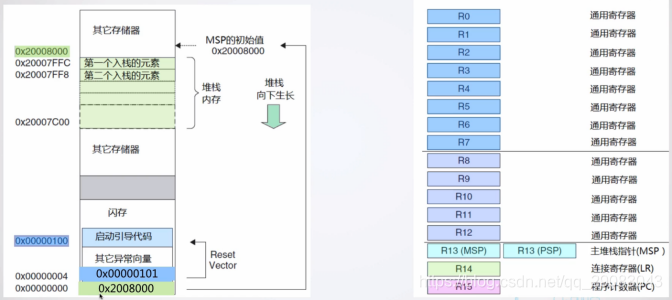

因为CPU有两个级别,所以有两个堆栈,物理上R13是两个寄存器(MSP和PSP)的代号,具体指哪个需要看当前CPU处于什么级别。

- 主栈指针(MSP),在复位后或处理器处于处理模式(处理模式指异常模式)时,处理器使用的都是这个栈。

- 进程栈指针(PSP),只应用在线程模式(线程模式就是执行普通的代码时所处的模式)。

大多数情况下,如果没有使用嵌入式OS,PSP也没有必要使用。绝大多数应用可以完全依赖于MSP。一般要用到OS时,才会使用到PSP;此时OS内核和应用任务的栈是相互独立的。PSP的初始值未定义,而MSP的初始值需要在复位流程中从存储器的第一个字中取出。

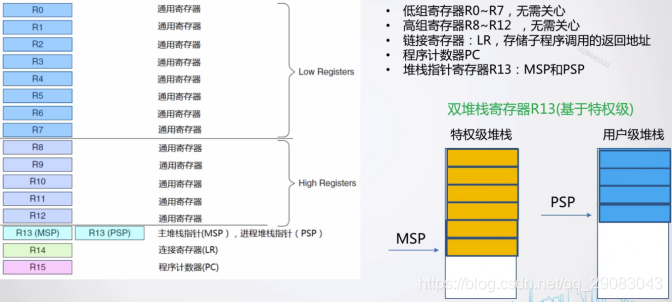

2.1.3.程序状态寄存器

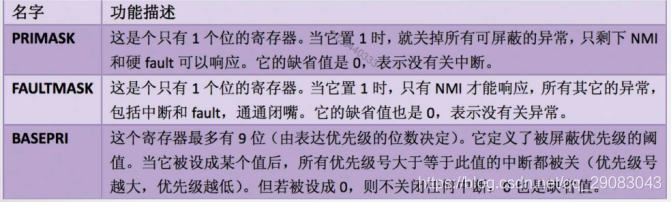

2.1.4.异常屏蔽寄存器

【经验1】·

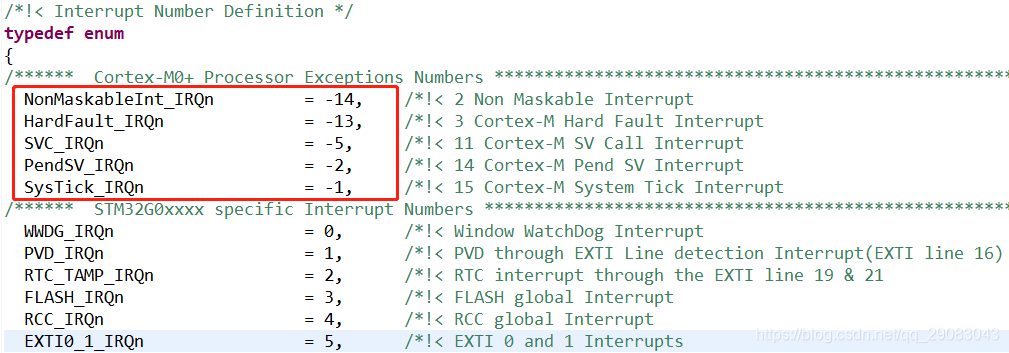

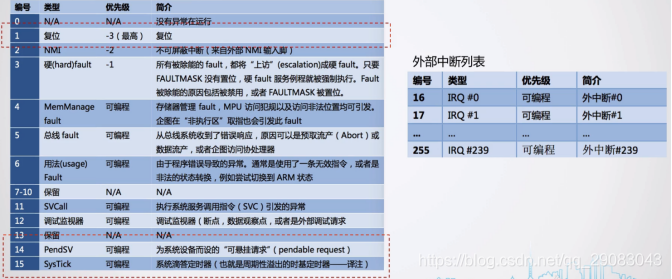

每一个异常源都有一个异常编号,编号1~15是系统中断,譬如SysTick中断。编号为负数的就是该芯片所支持的系统异常/中断。下图是STM32G071CBT6平台的中断截图:

系统中断不能通过HAL_NVIC_DisableIRQ(SysTick_IRQn)来关闭,可以通过以下两种方式关闭:

系统中断不能通过HAL_NVIC_DisableIRQ(SysTick_IRQn)来关闭,可以通过以下两种方式关闭:

- __disable_irq():关闭总中断。

- 直接操作ARM的内核寄存器关闭。

void vDisableIrq( void )

{

uint32_t value = 0;

value = SysTick->CTRL;

value = value & (~3);

SysTick->CTRL = value;

/*__disable_irq();*/

}

笔者在做IAP升级时,从bootloader跳转到app时出现以下情况:通过上位机下载app到flash,

然后再跳转,发现一跳转程序就跑飞;但当系统正常启动时,bootloader跳转到app确实成功的。

问题原因:

在跳转之前SysTick中断没有关闭,导致在跳转的过程中有可能发生SysTick中断,而此时的MSP已经被我修改了,所以程序跑飞。

跳转之前先关闭SysTick中断,iap跳转成功。

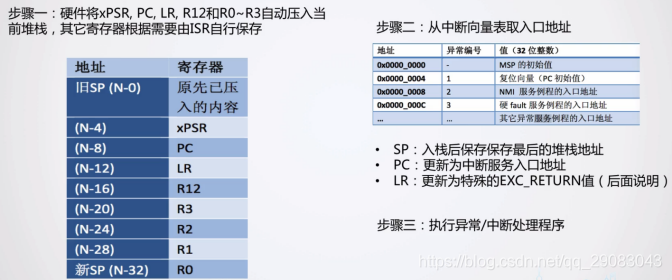

2.1.5.压栈和出栈

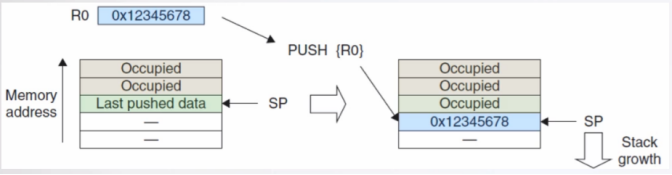

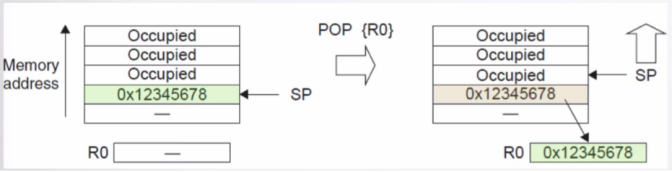

Cortex-M3使用的是“向下生长的满栈”模式(这也是为什么MSP的起始地址是20008000的原因)采用双堆栈机制。总之:栈寄存器存放的栈顶是高字节处的地址,当压栈时,栈地址从高字节逐渐递减(逐渐减4)。

① 压栈操作

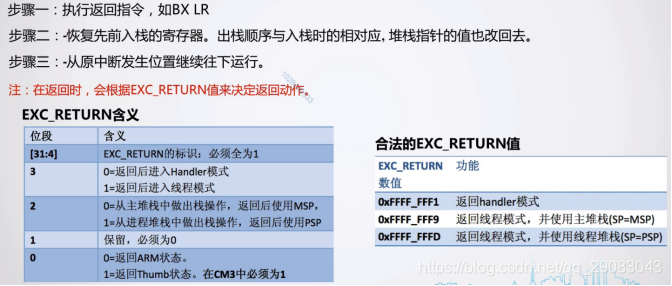

② 出栈操作

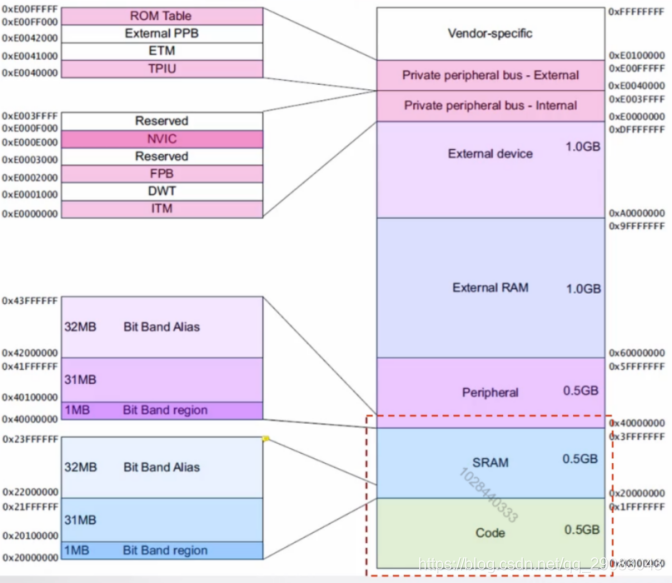

2.1.6.预定义的存储器映射

具体以芯片的数据手册为准。

- SRAM:片内RAM,用于存放堆栈、变量等数据。

- Code:用于存放可执行代码和常量。

STM32G071CBT67:

MEMORY

{

FLASH (rx) : ORIGIN = 0x8000000, LENGTH = 128K

RAM (rwx) : ORIGIN = 0x20000000, LENGTH = 36K

}

2.1.7.系统异常向量表

2.1.8.进入异常

2.1.9.退出异常

2.1.10.复位异常响应

2.1.11.PendSV异常

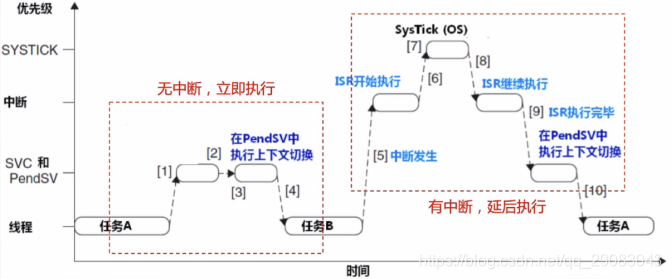

在PendSV中执行RTOS上下文切换,即不同任务间的切换;将这个异常配置为最低优先级,上下文切换的请求将自动延迟到其他ISR都完成后才处理,并且可以被其它异常或中断抢占。

2.2.汇编指令

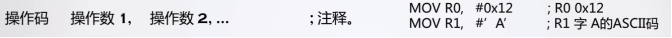

Cortex-M3使用的是Thumb-2指令集,长度可以是16bit或32bit;指令可以携带后缀。

2.2.1.典型写法

2.2.2.指令分类

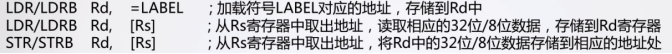

2.2.3.存储器访问

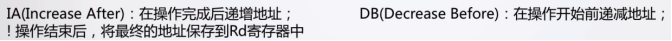

2.2.4.批量存储器访问

2.2.5.访问特殊功能寄存器

MRS和MSR用于访问xPSR、PSP、MSP等特殊功能寄存器。

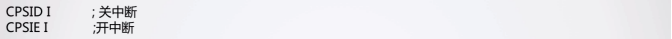

2.2.6.中断开关

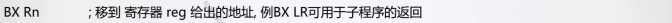

2.2.7.无条件跳转

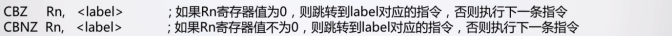

2.2.8.比较条件跳转

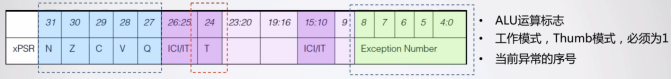

2.2.9.逻辑或操作