一件事,只要愿意去做并且认真去做,总会发现其中的趣味和意义。

1 简介

针对特殊系统中对于一些微弱信号的采集和监测设计了一种基于大规模现场可编程逻辑器件(FPGA),采用AD7768芯片,实现32位高速串行模数转换,为测量数据的实时性和准确性提供有力保障。整个软件的设计基于Vivado2019.1平台,使用System Verilog语言进行编程,并且本次设计遵循AD各项硬件指标。而现在多数是以单片机或CPU作为控制核心,尽管其编程简便,控制灵活,但是速度慢,控制周期长却成为影响系统高速性的重要因素,单片机的运行速度极大的限制了对AD高速性能的利用。

当前许多精密模数转换器(ADC)具有串行外设接口(SPI)或某种串行接口,用以与包括微控制器单元(MCU)、DSP和FPGA在内的控制器进行通信。AD7768支持外设接口(SPI)和PIN模式。本设计选择引脚模式,FPGA通过adc时钟引脚、数据引脚、数据准备引脚采集数据。

2 系统设计

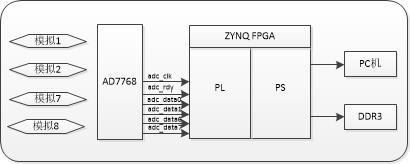

基于ZYNQ FPGA实现AD7768采集系统设计如图1所示。ADC7768输入8路查分模拟信号,输出8路转换后的数字信号,ZYNQFPGA PL端根据AD7768接口时序采集数据、跨时钟域处理、数据格式转换、数据封包管理和DMA传输;ZYNQ FPGA PS端进行数据DDR3写缓存和读显示和处理。

图1 系统设计

adc_clk:AD7768输出时钟,FPGA采样时钟。

adc_rdy: AD7768输出数据有效开始信号,FPGA采样开始信号,检测下降沿。

adc_data: AD7768输出数据信号,FPGA采样数据,8路串行数据。

3 关键技术

1)AD7768时序图

基于FPGA实现AD7768数据采集就是根据AD时序图完成硬件编码,时序图如图1所示。

基于FPGA实现ADC7768数据采集系统设计(8路)

猜你喜欢

转载自blog.csdn.net/m0_46498597/article/details/105841628

今日推荐

周排行