一、状态转移型的序列信号产生器的verilog HDL 设计

用一个不断循环的状态机,循环产生序列信号001011。过程过于简单,我就不画状态图了。

直接给出verilog HDL设计代码:

//有限状态机方式实现001011序列信号产生器

module sequence_signal_fsm(clk, rst_n, dout);

input clk, rst_n;

output dout;

reg dout;

reg [2:0] pre_state, next_state;

parameter s0 = 3'b000, s1 = 3'b001, s2 = 3'b010,

s3 = 3'b011, s4 = 3'b100, s5 = 3'b101;

always @(posedge clk or negedge rst_n)

begin

if(rst_n == 0)

pre_state <= s0;

else

pre_state <= next_state;

end

always @(pre_state)

begin

case(pre_state)

s0:

begin

dout = 1'b0;

next_state <= s1;

end

s1:

begin

dout = 1'b0;

next_state = s2;

end

s2:

begin

dout = 1'b1;

next_state = s3;

end

s3:

begin

dout = 1'b0;

next_state = s4;

end

s4:

begin

dout = 1'b1;

next_state = s5;

end

s5:

begin

dout = 1'b1;

next_state = s0;

end

default: next_state = s0;

endcase

end

endmodule

测试文件为:

`timescale 1ns/1ps module sequence_signal_fsm_tb; reg clk, rst_n; wire dout; always #10 clk = ~clk; initial begin clk = 1'b0; rst_n = 1'b1; #10 rst_n = 1'b0; #10 rst_n = 1'b1; end sequence_signal_fsm U1(.clk(clk), .rst_n(rst_n), .dout(dout)); endmodule

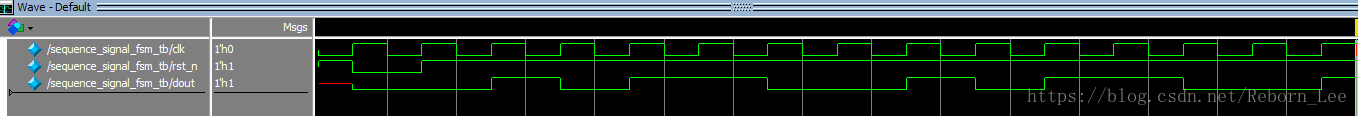

在Modelsim中仿真所得波形图为:

二、移位寄存器型序列信号产生器

下面描述的是一个6位移位寄存器类型的序列信号产生器,在输入端输入任意序列,通过移位寄存器,使得输入信号的最高位移入最低位,其他各位依次向左移一位,在每个时钟上升沿到来时,将输入信号的最高位通过dout输出,从而循环产生序列信号。

下面直接给出verilog HDL设计代码:

module signal_generator_shifter_reg(clk, rst, din, dout);

input clk, rst;

input [5:0] din;

output dout;

reg dout;

reg [5:0] temp;

always@(posedge clk)

begin

if(rst == 1'b1)

temp <= din;

else

begin

dout <= temp[5];

temp <= {temp[4:0], temp[5]};

end

end

endmodule

测试代码为:

`timescale 1ns/1ps module signal_generator_shifter_reg_tb; reg clk, rst; reg [5:0] din; wire dout; always #10 clk = ~clk; initial begin clk = 1'b0; rst = 1'b0; #10 rst = 1'b1; din = 6'b001011; #20 rst = 1'b0; end signal_generator_shifter_reg U1(.clk(clk), .rst(rst), .din(din), .dout(dout)); endmodule

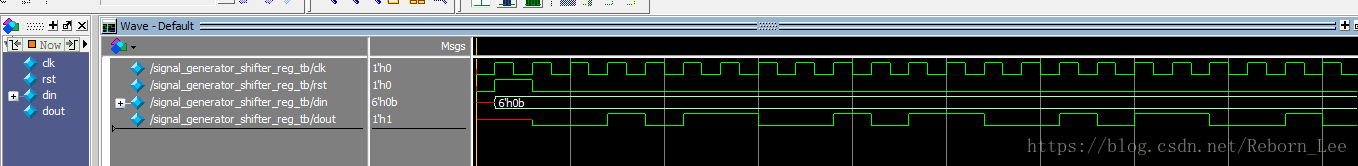

在Modelsim中仿真所得波形图如下:

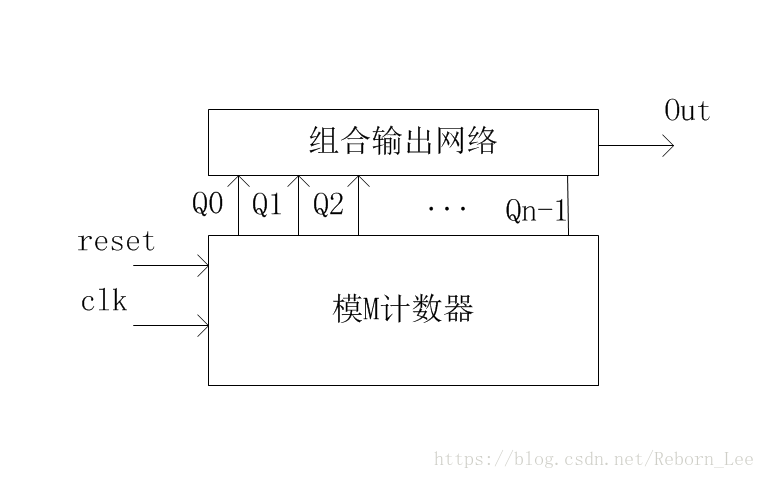

三、计数器加组合输出网络类型

计数型序列信号发生器的结构框图如上图示:它由计数器和组合输出网络两部分组成,序列信号从组合输出网络输出。这种类型的序列信号发生器一般分两步来设计,首先根据序列的长度M设计模M计数器,计数器的状态可以自定;然后按计数器的状态转移关系和序列码的要求设计组合输出网络。由于计数器的状态设置和输出网络没有直接的关系,因此这种结构对于输出序列的更改比较方便,而且还能同时产生多组序列码。

下面描述的为计数器加组合输出网络构成的序列信号发生器,产生001011序列信号,通过内部的3位计数器进行计数,由计数状态和输出序列的对应关系,得到其输出组合逻辑真值表,从表中可以看到,Q2Q1Q0从000开始计数并不断加1,每个状态对应一个输出Z。通过真值表可以得到卡诺图,化简后可以得到输出逻辑函数为:

Q2 |

Q1 |

Q0 |

Z |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

下面直接给出verilog HDL 设计代码:

module counter_sequence(clk, rst, dout); input clk, rst; output dout; reg [2:0] counter; always @(posedge clk) begin if(rst == 1'b1) counter <= 3'b000; else if(counter == 3'b101) counter <= 3'b000; else counter <= counter + 1'b1; end assign dout = ((~counter[0]) & counter[1]) | counter[2]; endmodule

测试文件:

module counter_sequence_tb; reg clk, rst; wire dout; always #10 clk = ~clk; initial begin clk = 1'b0; rst = 1'b0; #10 rst = 1'b1; #20 rst = 1'b0; end counter_sequence U1(.clk(clk), .rst(rst), .dout(dout)); endmodule

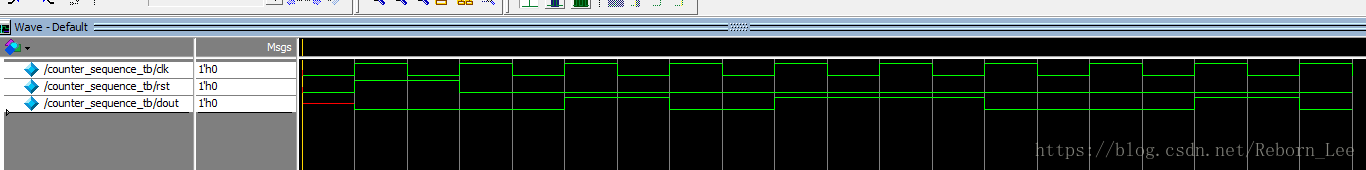

在Modelsim中仿真所得仿真图: