对于只有加法门和乘法门的arithmetic circuit,可将其理解为是“一系列的乘法门+一系列表示gate输入输出关系的linear consistency equations”。

一个 arithmetic circuit 可理解为是一个有向无环图,其中每个顶点称为gate。in-degree为0的gate为circuit的输入,可表示为 或者a constant field element。其它的gate可标示为 或 。

对于 fan-in 2 circuits,其所有 门和 门均具有 in-degree 2。

任何可表述为有向无环图的circuit均可转换为:

“一系列的乘法门+一系列表示gate输入输出关系的linear consistency equations”。

-

首先,需要将arithmetic circuit 中的加法门和常量乘法门替换为:

bilinear consistency equations on the inputs and outputs of the remaining gates

从而保证这些equations的satisfiability与原始circuit的satisfiability等同。

假设 为 的sub-circuit, 中包含了一个乘法门之前的所有wires和gates。 有 个input wires和 个output wires。这 个inputs可以单位向量表示 ,其中 。

– 对于每个加法门,其input表示为 ,其output表示为 。

– 对于每个常量乘法门,其input表示为 和常量 ,其output表示为 。

以此执行, 的 个output均可以length为 的向量来表示linear combinations of the inputs。

最多需要 个arithmetic operations。注意, 的所有output均为linear combinations of the inputs,所以 可表示为具有 个 fan-in 2 gates,使得consistency equations可直接从circuit description中获取。

注意,形如 的linear combination,可由 个常量乘法门和 个加法门组成。 -

其次,将 的gates 从 中移除,同时移除 any multiplication gates whose inputs are the inputs of the new circuit。

-

重复以上过程,知道找出所有的consistency equations。repeat the process of finding consistency equations until we have considered the whole of 。

注意,circuit

的第一个(input)和最后一个(output)sub-circuit需要增加额外操作。

以 output sub-circuit为例(input sub-circuit类似):

- 假设

为the output sub-circuit,其

个input表示为

,

个output表示为

。

其中,每个output 均可表示为 ,所有的可表示为:

其中 为 矩阵, 为size为 的列向量。

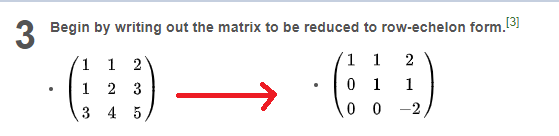

假设矩阵 的rank为 ,则可将 reduce 为 row echelon form ,可表示为:

附注:

- 所谓matrix rank是指:通过行列式转换,非零行的数量。matrix的rank最大可能值为 。

- 所谓row echelon form matrix是指:通过行列式转换,将矩阵左下角的所有元素均表示为0的过程。

参考资料:

[1] How to Reduce a Matrix to Row Echelon Form

[2] Bootle和Groth等人2016年论文《Efficient Zero-Knowledge Arguments for Arithmetic Circuits in the Discrete Log Setting》

[3] matrix rank