初识中断

事实上所有计算机都提供了允许其他模块(I/O,存储器)中断处理器正常处理过程的机制。常见的中断类别有如下几种:

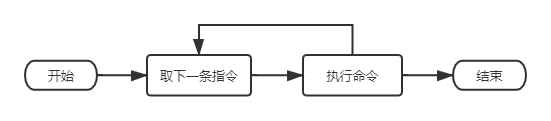

中断最初是用于提高处理器效率的一种手段。例如,如果处理器按照下图所示的指令周期给一个I/O设备传递数据,在每一次写操作之后,处理器必须暂停并保持空闲,直到I/O设备完成工作。暂停的时间长度可能相当于成百上千个不涉及I/O操作的指令周期。显然,这对于处理器的使用来说是非常浪费的。

假设有一个 1GHz 的 CPU,大约每秒可执行 10 亿条指令。一个典型的硬盘速度约为 7200 转/分,旋转半转的时间约为 4ms。如果没有中断机制的话,一个需要半转的I/O操作也要消耗掉约 400 万个指令周期。

中断与 I/O

上图描述了三种中断的流程:

- 左图:无中断

- 中图:有中断,且I/O操作时间短于完成两次写操作之间指令的时间。

- 右图:有中断,且I/O操作时间长于完成两次写操作之间指令的时间。

图中各代码段含义:

- 第 1,2,3 步骤均表示不涉及 I/O 的指令序列。

- WRITE 调用要执行一个 I/O 程序,此 I/O 程序是一个系统工具程序,由它执行真正的 I/O 操作。此 I/O 程序由三部分组成:

- 图中标记为 4 的指令序列用于为实际的 I/O 操作做准备。这包括复制将要输出到特定缓冲区的数据,为设备命令准备参数。

- 实际的 I/O 命令。如果不使用中断,当执行此命令时,程序必须等待 I/O 设备执行请求的函数(或周期性的检测 I/O 设备状态或轮询 I/O 设备)。

- 图中标记为 5 的指令序列用于完成操作。包括设置一个表示操作成功或失败的标记。

虚线代表处理器执行的路径:也就是说,这条线显示了指令执行的顺序。当遇到第一条 WRITE 指令之后,用户程序被中断,I/O 程序开始执行。在 I/O 程序执行完成后,WRITE 指令之后的用户程序才能恢复执行。

由于完成 I/O 操作可能花费较长的时间,I/O 程序需要挂起等待操作完成,因此用户会在 WRITE 调用处停留相当长的一段时间。

中断与指令周期

利用中断功能,处理器可以在 I/O 操作的执行过程中执行其他指令。考虑上图中间部分所示的控制流,和前面一样,用户到达系统调用 WRITE 处,但涉及的 I/O 程序仅包括准备代码和真正的 I/O 命令。在这些为数不多的几条指令执行后,控制流返回到用户程序。在这期间,外部设备正忙于从计算机存储器接收数据并打印。这种 I/O 操作和用户程序中指令的执行是并发的。

当外部设备准备接收更多数据时,可以给处理器发送一个中断请求信号。这是处理器会做出响应,暂停当前程序的处理,转去处理服务于特定 I/O 设备的程序,这个程序称为中断处理程序(interrupt handler)。在对该设备的服务响应完成后,处理器恢复原先的执行。如上图中间部分所示。

即便使用了中断机制,WRITE调用仍然可能导致用户程序被挂起。如上图右边部分所示,I/O 操作时间长于完成两次写操作之间指令的时间。在这种情况下,用户程序在由第一次调用产生的 I/O 操作完成之前,就到达了第二次WRITE调用。当前面的 I/O 操作完成之后,才能继续新的 WRITE 操作,也才能开始一次新的 I/O 操作。但即便如此,处理器的利用率仍有所提升,因为总会有一段时间窗口,用户程序和 I/O 操作在并发执行。

两次WRITE调用只能串行执行,可以理解为缓冲区已满,无法复制将要输出的数据,所以只能被挂起。

为适应中断的产生的情况,在指令周期中需添加一个中断阶段,如上图所示。

在中断阶段中,处理器会检查有无中断信号:如果没有,处理器继续执行下一条指令;如果有中断,处理器会挂起当前程序的执行,并执行一个中断处理程序。中断处理程序是操作系统的一部分,它确定中断的性质,并执行所需要的操作。

中断处理

中断激活了很多事件,包括处理器硬件中的事件以及软件中的事件。如下图所示,当 I/O 设备完成一次 I/O 操作时,发生下列事件:

PC:Program Counter。程序计数器,包含下一条待执行指令的地址。

PSW:Program Status Word。程序状态字,一般用一个专门的寄存器来指示处理器状态。PSW 包括的状态位有进位标志位(CF)、结果为零标志位(ZF)、符号标志位(SF)、溢出标志位(OF)、陷阱标志位(TF)、中断使能(中断屏蔽)标志位(IF)、虚拟中断标志位(VIF)、虚拟中断待决标志位(VIP)、I0特权级别(IOPL)。

- 设备给处理器发送一个中断信号。

- 处理器在响应中断前先完成当前指令的执行。

- 处理器对中断进行测定,确定存在未响应的中断,并给提交中断的设备发送确认信号,确认信号允许该设备取消它的中断信号。

- 处理器为开始执行中断程序做准备:保存从中断点恢复当前程序所需要的信息,要求的最少信息包括 PSW 和 PC 中的数据,这些数据被压入系统控制栈中。

- 处理器把响应此中断的中断处理程序入口地址装入PC中。每种设备和中断可以使用不同的中断处理程序。

将中断处理程序的入口地址装入 PC 后,处理器即进入下一个指令周期。因为PC的数据已被修改为中断处理程序的入口地址,所以CPU的控制权被转移到中断控制程序。

- 中断处理程序应将被中断程序的信息保存下来,例如所有寄存器的值。

- 中断处理程序现在可以开始处理中断。

- 中断处理结束后,被保存的寄存器的值恢复到寄存器中。

- 恢复 PSW 和 PC 的数据。这使得在处理器的下一个指令周期,控制权又回到了被中断程序。

多个中断

当处理器正在处理一个中断时,可能还会其他中断发生。处理多个中断有两个方法:

- 当正在处理一个中断时,禁止再发生中断。禁止的意思处理器对任何新的中断请求信号不予理睬。

- 定义中断优先级,允许高优先级的中断打断低优先级的中断处理程序的运行。