文章目录

目录

实验要求

第一步:

设计一个加减计数器,将其与实验一中的Binary-to-BCD译码器、和交替显示控制电路结合

如图:

计数器输入:Clk,Up,Down,Rst,Enable

8bits输出:Cnt7~Cnt0

Rst=1 ,计数器清零

Rst=0,Enable=1 ,则每个时钟上跳沿或下跳沿加一(Up=1)或减一(Down=1)

第二步

将计数器输入改成按键控制:

Basy3电路板(xc7a35tcpg236-1)

按上键代表Up加计数

下键代表Down减计数

中间键代表Enable表示暂停

计数器初始处于空闲状态

若捕捉到下键则开始减计数,之后又捕捉到上键改为加计数,一旦中间键按下,则计数过程暂停;若又捕捉到上键或者下键,则从暂停前的计数继续开始计数

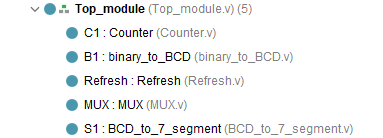

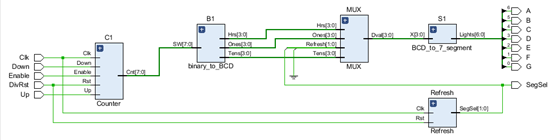

工程结构

核心代码

计数器模块

最重要的模块,剩下的模块都是借鉴上一个实验的:

module Counter(Clk,Up_set,Down_set,Rst_set,Enable_set,Cnt

);

input Clk;

input Up_set;

input Down_set;

input Rst_set;

input Enable_set;

output reg [7:0] Cnt;

reg [15:0] cnt_first;

reg [15:0] cnt_second;

reg CLK;

reg [3:0]Chg;

initial begin

Cnt<=8'b00000000;

Chg<=4'b0000;

cnt_first<=16'b0;

cnt_second<=16'b0;

end

always@(posedge Clk)begin

if(cnt_first==16'd5000)

cnt_first<=16'd0;

else cnt_first<=cnt_first+1'b1;

end

always@(posedge Clk)begin

if(cnt_first==16'd5000) cnt_second<=cnt_second+1'b1;

if(cnt_second==16'd5000) begin

cnt_second<=0;

CLK=~CLK;

end

end

always@(posedge Up_set or posedge Down_set or posedge Enable_set or posedge Rst_set)begin

if(Rst_set==1) Chg<=4'b0000;

else if(Up_set==1) Chg<=4'b1001;

else if(Down_set==1) Chg<=4'b1010;

else if(Enable_set==1) Chg[3]<=~Chg[3];

end

always@(posedge CLK)begin

case(Chg)

4'b0000:Cnt<=8'b0;

4'b1001:Cnt<=Cnt+1'b1;

4'b1010:Cnt<=Cnt-1'b1;

endcase

end

endmodule

其中:

always@(posedge Up_set or posedge Down_set or posedge Enable_set or posedge Rst_set)begin

if(Rst_set==1) Chg<=4'b0000;

else if(Up_set==1) Chg<=4'b1001;

else if(Down_set==1) Chg<=4'b1010;

else if(Enable_set==1) Chg[3]<=~Chg[3];

end

这一部分代码在实现implementation的时候会报错:

[Designutils 20-970] Unrecognized or unsupported command 'set_property IOSTANDARD LVCMOS33 [get_ports {Enable]

set_property IOSTANDARD LVCMOS33 [get_ports {SegSel_n[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {SegSel_n[2]}]

set_property IOSTANDARD LVCMO ... (truncated) ' found in constraint file. ["C:/Users/18000/For_Ba_Counter/For_Ba_Counter.srcs/constrs_1/new/Constr.xdc":27]

在约束文件中加入

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets Enable_IBUF]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets Up_IBUF]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets Down_IBUF]

即可解决问题

或者将这一段代码改为:

扫描二维码关注公众号,回复:

11569483 查看本文章

always@(posedge CLK)begin

if(Rst_set==1) Chg<=4'b0000;

else if(Up_set==1) Chg<=4'b1001;

else if(Down_set==1) Chg<=4'b1010;

else if(Enable_set==1) Chg[3]<=~Chg[3];

end

这是一种更好的方式,符合Verilog硬件编程的原则

顶层模块

module Top_module(Clk,Up,Down,SegSel_n,A,B,C,D,E,F,G,Enable,Rst

);

input Clk;

input Up;

input Down;

input Enable;

input Rst;

output [3:0]SegSel_n;

output A;

output B;

output C;

output D;

output E;

output F;

output G;

wire [7:0] Cnt;

wire [3:0]SegSel;

Counter C1(.Clk(Clk),.Up_set(Up),.Down_set(Down),.Rst_set(Rst),.Enable_set(Enable),.Cnt(Cnt));

wire [3:0]Hrs;

wire [3:0]Tens;

wire [3:0]Ones;

binary_to_BCD B1(.SW(Cnt),.Hrs(Hrs),.Tens(Tens),.Ones(Ones));

Refresh Refresh(.Clk(Clk),.Rst(1'b0),.SegSel(SegSel));

wire [3:0]Dval;

MUX MUX(.Refresh(SegSel),.Dval(Dval),.Hrs(Hrs),.Tens(Tens),.Ones(Ones));

wire [6:0]L;

BCD_to_7_segment S1(.X(Dval),.Lights(L));

assign {A,B,C,D,E,F,G}=~L;

assign SegSel_n=~SegSel;

endmodule

刷新电路

module Refresh(Clk,Rst,SegSel

);

input Clk,Rst;

output reg [3:0]SegSel;

initial begin

SegSel=4'b0001;

end

reg [7:0] count_fst;

reg[3:0]count_second;

always@(posedge Clk)begin

if(Rst==1) begin

count_fst<=8'b00000000;

SegSel<=4'b0000;

end

else begin

if(count_fst==8'b11111111)

begin

count_fst<=4'b00000000;

count_second<=count_second+1'b1;

if(count_second==4'b1111)begin

count_second<=4'b0000;

case(SegSel)

4'b0000:SegSel<=4'b0001;

4'b0001:SegSel<=4'b0010;

4'b0010:SegSel<=4'b0100;

4'b0100:SegSel<=4'b1000;

4'b1000:SegSel<=4'b0001;

default:SegSel<=4'b0000;

endcase

end

end

else count_fst<=count_fst+8'b00000001;

end

end

endmodule

多工器

module MUX(Refresh,Dval,Hrs,Tens,Ones

);

input [3:0] Refresh;

input [3:0]Tens;

input [3:0]Hrs;

input [3:0]Ones;

output reg [3:0]Dval;

always@(*) begin

case(Refresh)

4'b0000:Dval=4'b0000;

4'b0001:Dval=Ones;

4'b0010:Dval=Tens;

4'b0100:Dval=Hrs;

default:Dval=4'b0000;

endcase

end

endmodule

Binary-to-BCD译码器

module binary_to_BCD(SW,Hrs,Tens,Ones);

input [7:0] SW;

output [3:0]Hrs;

output [3:0]Tens;

output [3:0]Ones;

reg [17:0] Z;

always@(SW)begin

Z=18'b0;

Z[7:0]=SW;

repeat(8)

begin

if(Z[11:8]>4)

Z[11:8]=Z[11:8]+2'b11;

if(Z[15:12]>4)

Z[15:12]=Z[15:12]+2'b11;

Z[17:1]=Z[16:0];

end

end

assign Hrs=Z[17:16];

assign Tens=Z[15:12];

assign Ones=Z[11:8];

endmodule

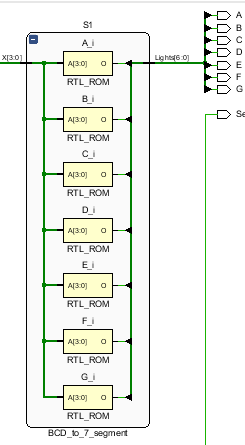

BCD-to-7-Segment

module BCD_to_7_segment(X,Lights);

input [3:0] X;

output reg [6:0] Lights;

reg X3,X2,X1,X0;

reg A,B,C,D,E,F,G;

always @(X)begin

{X3,X2,X1,X0}=X;

case({X3,X2,X1,X0})

4'd0:{A,B,C,D,E,F,G}=7'b1111110;

4'd1:{A,B,C,D,E,F,G}=7'b0110000;

4'd2:{A,B,C,D,E,F,G}=7'b1101101;

4'd3:{A,B,C,D,E,F,G}=7'b1111001;

4'd4:{A,B,C,D,E,F,G}=7'b0110011;

4'd5:{A,B,C,D,E,F,G}=7'b1011011;

4'd6:{A,B,C,D,E,F,G}=7'b1011111;

4'd7:{A,B,C,D,E,F,G}=7'b1110000;

4'd8:{A,B,C,D,E,F,G}=7'b1111111;

4'd9:{A,B,C,D,E,F,G}=7'b1111011;

default {A,B,C,D,E,F,G}=7'b0000000;

endcase

Lights={A,B,C,D,E,F,G};

end

endmodule

综合结果

该结构和实验要求中给出的逻辑图几乎完全一致

Refresh

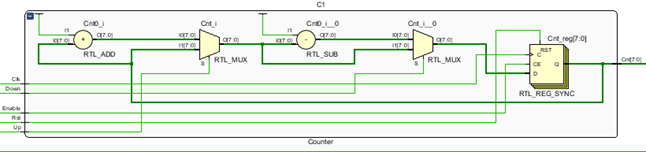

Counter计数模块

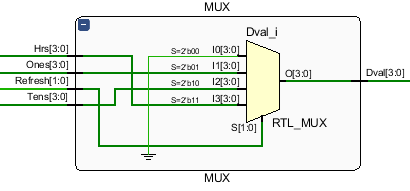

MUX模块:

七位译码器模块:

BCD译码器是如下图相同结构的八层迭代

管脚约束文件

set_property PACKAGE_PIN W6 [get_ports B]

set_property PACKAGE_PIN U8 [get_ports C]

set_property PACKAGE_PIN V8 [get_ports D]

set_property PACKAGE_PIN U5 [get_ports E]

set_property PACKAGE_PIN U7 [get_ports G]

set_property PACKAGE_PIN T18 [get_ports Up]

set_property IOSTANDARD LVCMOS33 [get_ports A]

set_property IOSTANDARD LVCMOS33 [get_ports B]

set_property IOSTANDARD LVCMOS33 [get_ports C]

set_property IOSTANDARD LVCMOS33 [get_ports Clk]

set_property IOSTANDARD LVCMOS33 [get_ports D]

set_property IOSTANDARD LVCMOS33 [get_ports Down]

set_property IOSTANDARD LVCMOS33 [get_ports E]

set_property IOSTANDARD LVCMOS33 [get_ports F]

set_property IOSTANDARD LVCMOS33 [get_ports G]

set_property IOSTANDARD LVCMOS33 [get_ports Up]

set_property PACKAGE_PIN W5 [get_ports Clk]

set_property PACKAGE_PIN U17 [get_ports Down]

set_property PACKAGE_PIN W7 [get_ports A]

set_property PACKAGE_PIN V5 [get_ports F]

set_property IOSTANDARD LVCMOS33 [get_ports Enable]

set_property PACKAGE_PIN W4 [get_ports {SegSel_n[3]}]

set_property PACKAGE_PIN V4 [get_ports {SegSel_n[2]}]

set_property PACKAGE_PIN U4 [get_ports {SegSel_n[1]}]

set_property PACKAGE_PIN U18 [get_ports Enable]

set_property PACKAGE_PIN U2 [get_ports {SegSel_n[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {SegSel_n[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {SegSel_n[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {SegSel_n[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {SegSel_n[0]}]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets Enable_IBUF]

set_property IOSTANDARD LVCMOS33 [get_ports Rst]

set_property PACKAGE_PIN W19 [get_ports Rst]