CRC校验原理

- 求解CRC-8的编码电路和CRC校验的原理

G(X) = X8+H7*X7+H6*X6+H5*X5+H4*X4+H3*X3+H2*X2+H1*X1+X0

生成多项式

G(X)=9‘b1_0000_0111

信息位(需要发送的数据)

16’b=1100_1101_0010_1110

1100_1101_0010_1110__0000_0000(待编码的数据)

1000_0011_1(二进制除法做异或运算)

0100_1110_10

100_0001_11

000_1111_0110_1

1000_0011_1

0111_0101_01

100_0001_11

011_0110_101

10_0000_111

01_0110_0100

1_0000_0111

0_0110_0011_00

100_0001_11

010_0010_110

10_0000_111

00_0010_0010_000

10_0000_111

10_1110

最后得到的是我们信息位的校验位,用于接收端对帧数据是否出错进行判断的冗余位。

编码后的数据为:

1100_1101_0010_1110__0010_1110

解码过程:

1100_1101_0010_1110__0010_1110

1000_0011_1(二进制除法做异或运算)

0100_1100_1

………………………..

0_0110_0011__00

100_0001__11

010_0010__111

10_0000__111

00_0010__0000_111

10_0000__111

00_0000__0000

|

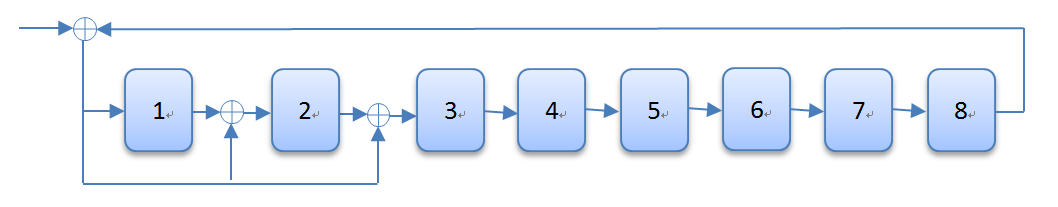

生成多项式的除法电路:

图中编号为1,2……7,8寄存器对应R[0]到R[7]

推导出两位并行输入的数据的CRC-8的算法

D[1:0]//数据的输入

R[7:0]//除法电路的寄存器

移入一比特时各个寄存器的状态为:(移入的数据比特指D[0])

第一个寄存器:D[0]^R[7]

第二个寄存器: D[0]^R[7]^R[0]

第三个寄存器: D[0]^R[7]^R[1]

第四个寄存器:R[2]

第五个寄存器: R[3]

第六个寄存器: R[4]

第七个寄存器: R[5]

第八个寄存器: R[6]

移入第二个数据比特时各个寄存器的状态为: (移入的第二个数据比特指D[1])

第一个寄存器:D[1]^R[6]

第二个寄存器: D[1]^R[6]^ D[0]^R[7]

第三个寄存器: D[1]^R[6]^ D[0]^R[7]^R[0]

第四个寄存器: D[0]^R[7]^R[1]

第五个寄存器: R[2]

第六个寄存器: R[3]

第七个寄存器: R[4]

第八个寄存器: R[5]

按照这个个推导方式可以推导出8位除法电路。同样32位CRC冗余校验也是这样的操作方法,32位运算起来太麻烦了,一般某项技术标准中会有直接的结论不需要自己再推,我们要做的是用FPGA把这些算法实现起来。