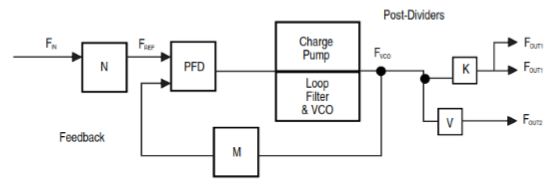

I PLL结构

PLL 由一个 N 位预分频计数器,鉴频鉴相器(PFD,Phase-Frequency Detector),电荷泵 (CP,Charge Pump),环路滤波器(LF,Loop Filter),压控振荡器(VCO,Voltage Controlled Oscillator), M 位的反馈乘法计数器以及 K 位和 N 位的后分频计数器构成。

在工作时,鉴频鉴相器检测F(REF)与返回信号(Feedback)之间的相位以及频率差异,控 制可将相位差异转换成电压的环路滤波器,进而控制压控振荡器产生更高或者更低的频率振 荡。当F(REF)与返回信号的频率相位相等时,输出电压与输入电压保持固定的相位差值,即输 出电压与输入电压的相位被锁住,这就是锁相环名称的由来

II FPGA中的PLL的使用

设计思路:使用PLL 分别输出25MHz、75MHz、100MHz的输出频率。

III 获取端口列表

module pllip (

areset, //异步复位

inclk0, //输入时钟

c0, //输出0

c1, //输入1

c2, //输出2

locked); //锁相环是否有稳定输出

input areset;

input inclk0;

output c0;

output c1;

output c2;

output locked;

IV testbench

`timescale 1ns/1ns

module pll_tb;

reg areset;

reg clk;

wire c0;

wire c1;

wire c2;

wire locked;

pllip f1(

.areset(areset),

.inclk0(clk),

.c0(c0),

.c1(c1),

.c2(c2),

.locked(locked)

);

initial clk = 1'b1;

always #10 clk = ~clk;

initial begin

areset = 1'b1;

#(20*100+1);

areset = 1'b0;

#(20*200+1);

$stop;

end

endmodule

V 前仿真