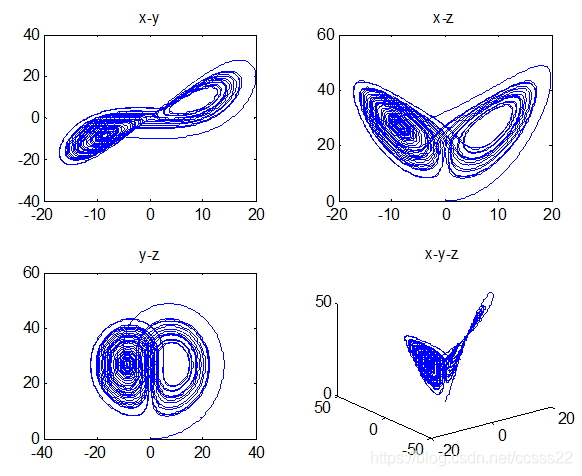

首先,我们使用MATLAB进行仿真,得到如下结果:

然后,我们使用FPGA进行实现

此时,式中A=10,B=28,C=8/3为典型参数。

为便于用FPGA实现连续混沌系统,可以采用Euler算法对式进行离散化处理,得到如下离散化方程:

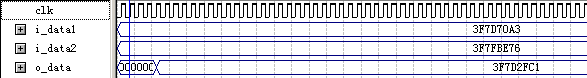

本系统我们采用IEEE754单精度表示方法进行表示,可以得到如下的结果。

0.99:3F7D70A3

0.999:3F7FBE76

0.01:3C23D70A

0.001:3A83126E

0.028:3CE56041

0.9973333:3F7F513C

2.1浮点乘法器

该乘法器,我们采用IP核来完成。

图1 乘法器IP核生成步骤1

下一步:

图2 乘法器IP核生成步骤2

下一步:

图3乘法器IP核生成步骤3

后面的保持默认的设置即可。

完成,对该核进行仿真,仿真结果如下所示:

图4乘法器IP核仿真

2.2浮点加/减法器

图5加法器IP核生成

其余保持默认,完成加法器IP核的设置。

其仿真结果如下所示:

图6加法器IP核仿真

其所有的顶层原理图如下所示:

从上,我们可以看到整个系统占用资源较少,主要实用到了大量的乘法器。

4 系统仿真

对系统进行功能仿真:得到如下的结果:

图13 系统总体仿真结果