void scia_fifo_init() //FIFO寄存器配置

{

SciaRegs.SCICCR.all =0x0007; // 1 stop bit, No loopback 无环回 SCI通信控制寄存器

// No parity,8 char bits,无校验,8个字符

// async mode, idle-line protocol 异步,空闲模式

SciaRegs.SCICTL1.all =0x0003; // enable TX, RX(向缓冲区传输), internal SCICLK, 使能收发引脚,SCICLK时钟周期

// Disable RX ERR, SLEEP, TXWAKE

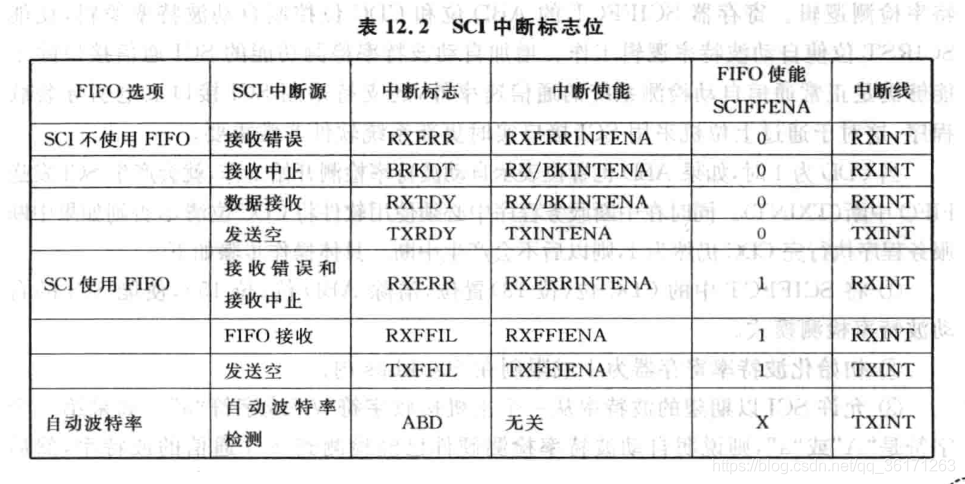

//SCITXBUF寄存器中断使能。该位控制由TXRDY标志位(SCICTL2.7)置1引起的中断请求。

//但是,它不会阻止设置TXRDY标志(设置表示寄存器SCITXBUF已准备好接收另一个字符)。

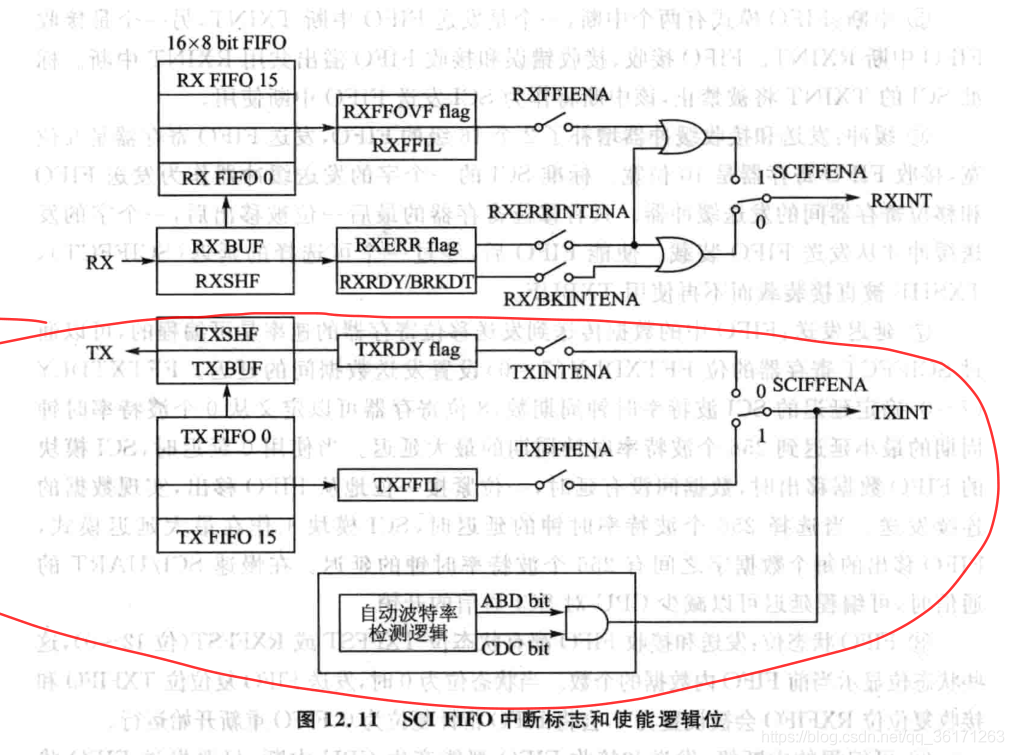

SciaRegs.SCICTL2.bit.TXINTENA =1;

//接收器缓冲/中断中断使能。 该位控制由RXRDY标志或BRKDT标志(位SCIRXST.6和.5)置1引起的中断请求。

//但是,RX / BK INT ENA不会阻止这些标志的设置。

SciaRegs.SCICTL2.bit.RXBKINTENA =1;

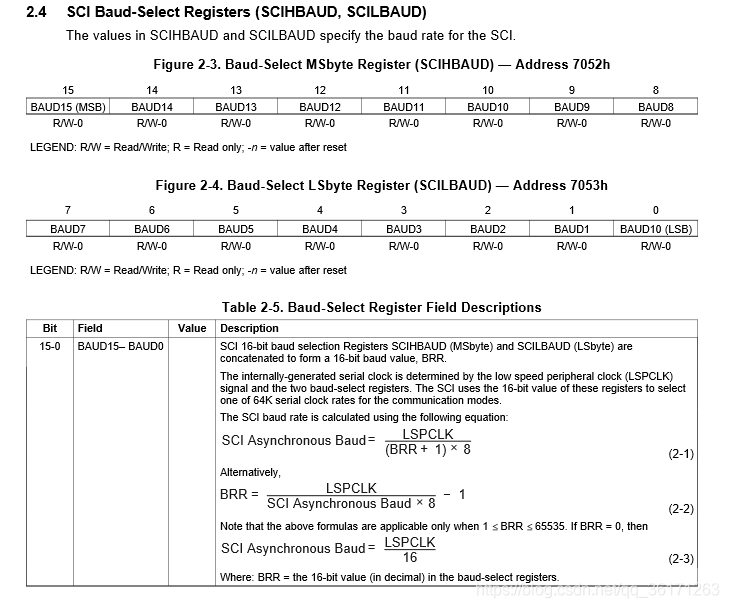

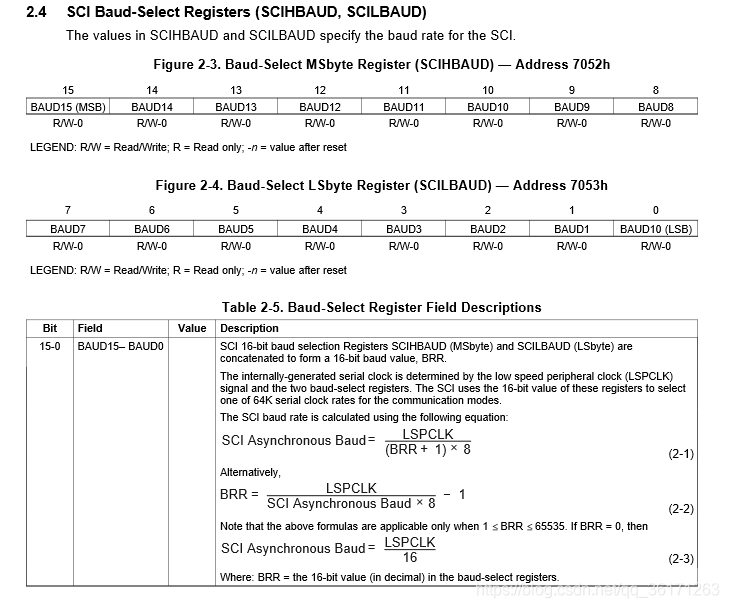

//SCI 波特率控制寄存器

SciaRegs.SCIHBAUD = 0x0000;

SciaRegs.SCILBAUD = SCI_PRD; //(150E6/4/(100E3*8))-1 150E6/4=LSPCLCK(默认低速时钟4倍分频) SCI_PRD=BRR

SciaRegs.SCICCR.bit.LOOPBKENA =1; // Enable loop back

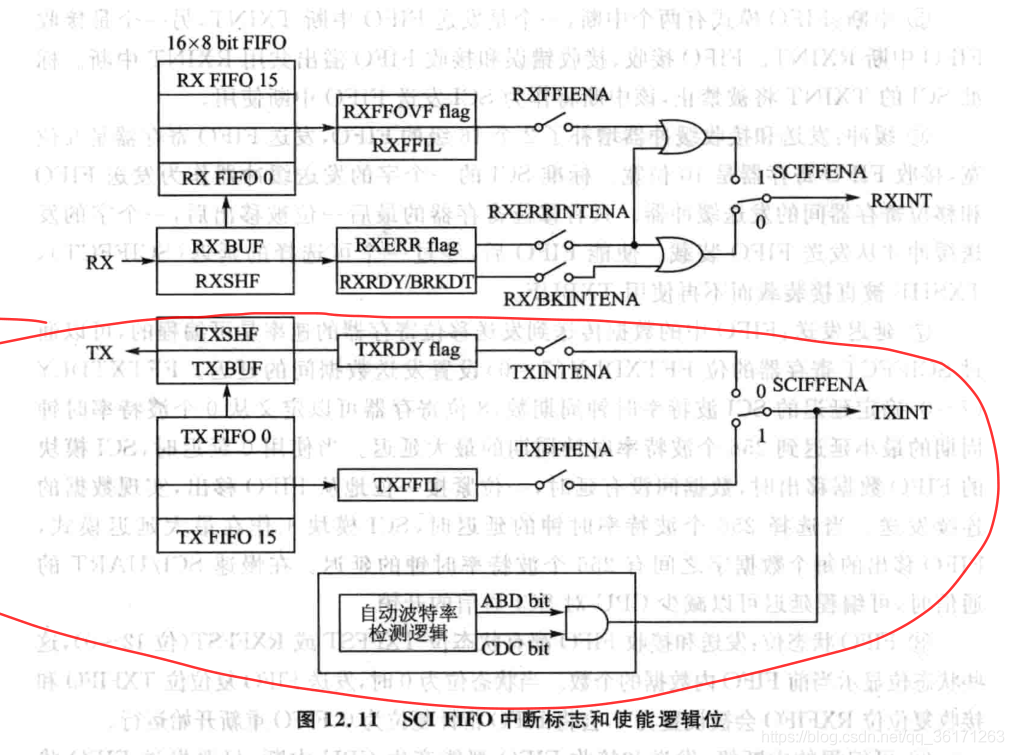

SciaRegs.SCIFFTX.all=0xC028; //FIFO 发送寄存器

SciaRegs.SCIFFRX.all=0x0028; //FIFO 接收寄存器

SciaRegs.SCIFFCT.all=0x00; //FIFO 控制寄存器

SciaRegs.SCICTL1.all =0x0023; // Relinquish SCI from Reset 重置SCI,循环上一步SCICTL1的以下的操作

SciaRegs.SCIFFTX.bit.TXFIFOXRESET=1; //重新启用FIFO发送操作

SciaRegs.SCIFFRX.bit.RXFIFORESET=1; //重新启用FIFO接收操作

}