-

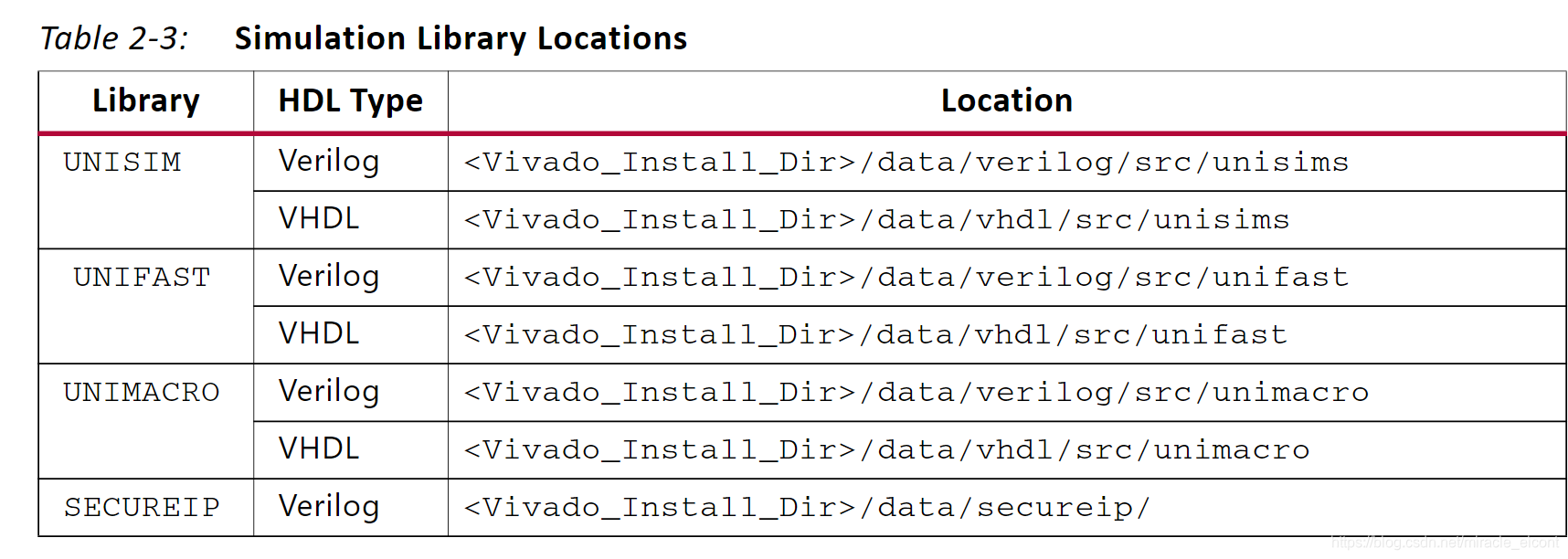

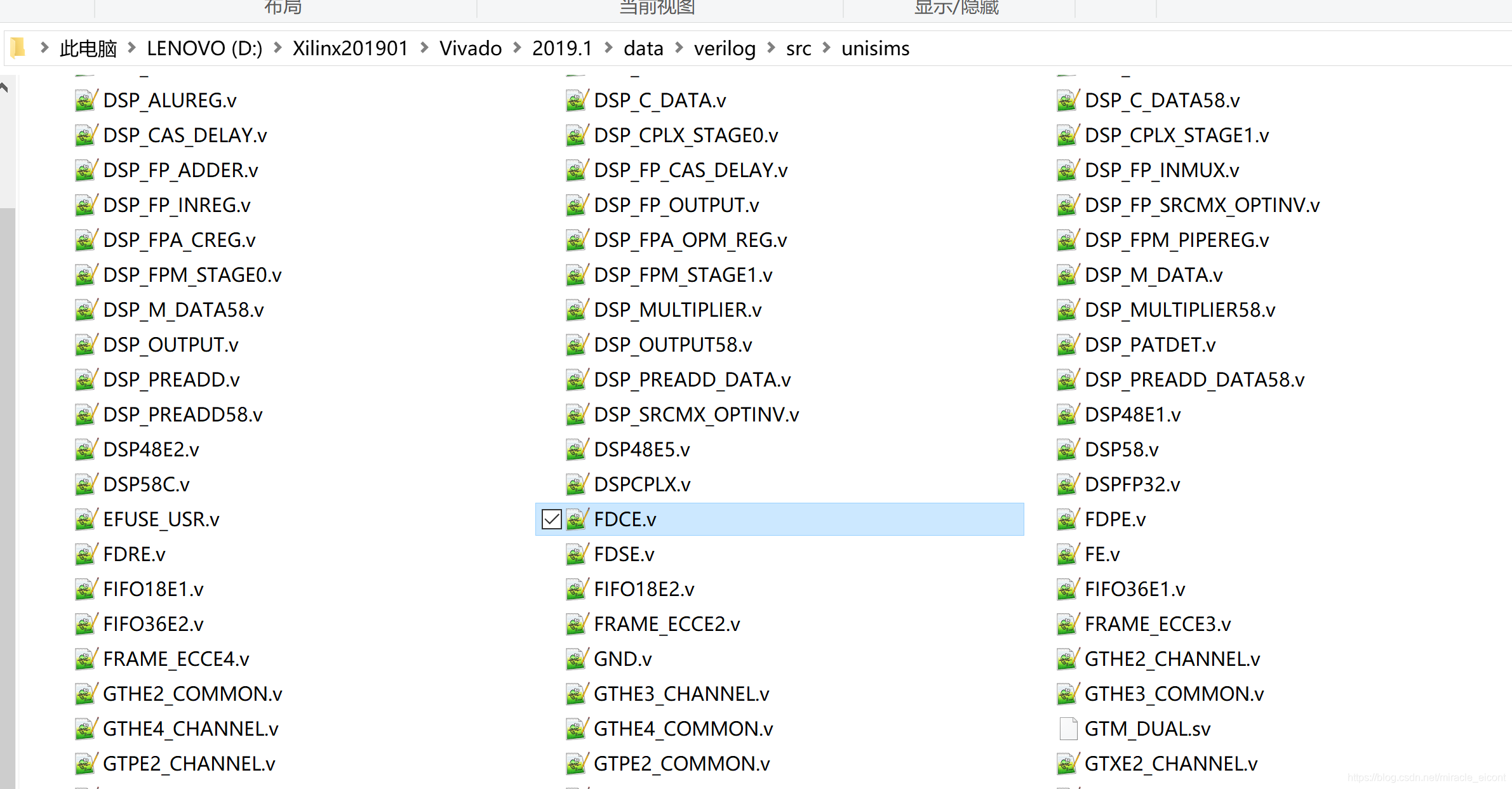

使用Vivado自带的simulator时,不需要编译仿真库,仿真库本身就存在,它在这里,如下图,但当使用第三方simulator时就必要要为该simulator编译专门的仿真库。 这些仿真库包括了元件与IP的形为、时序等模型,不编译是不行的,但只需要开始使用时编译一次就好。

-

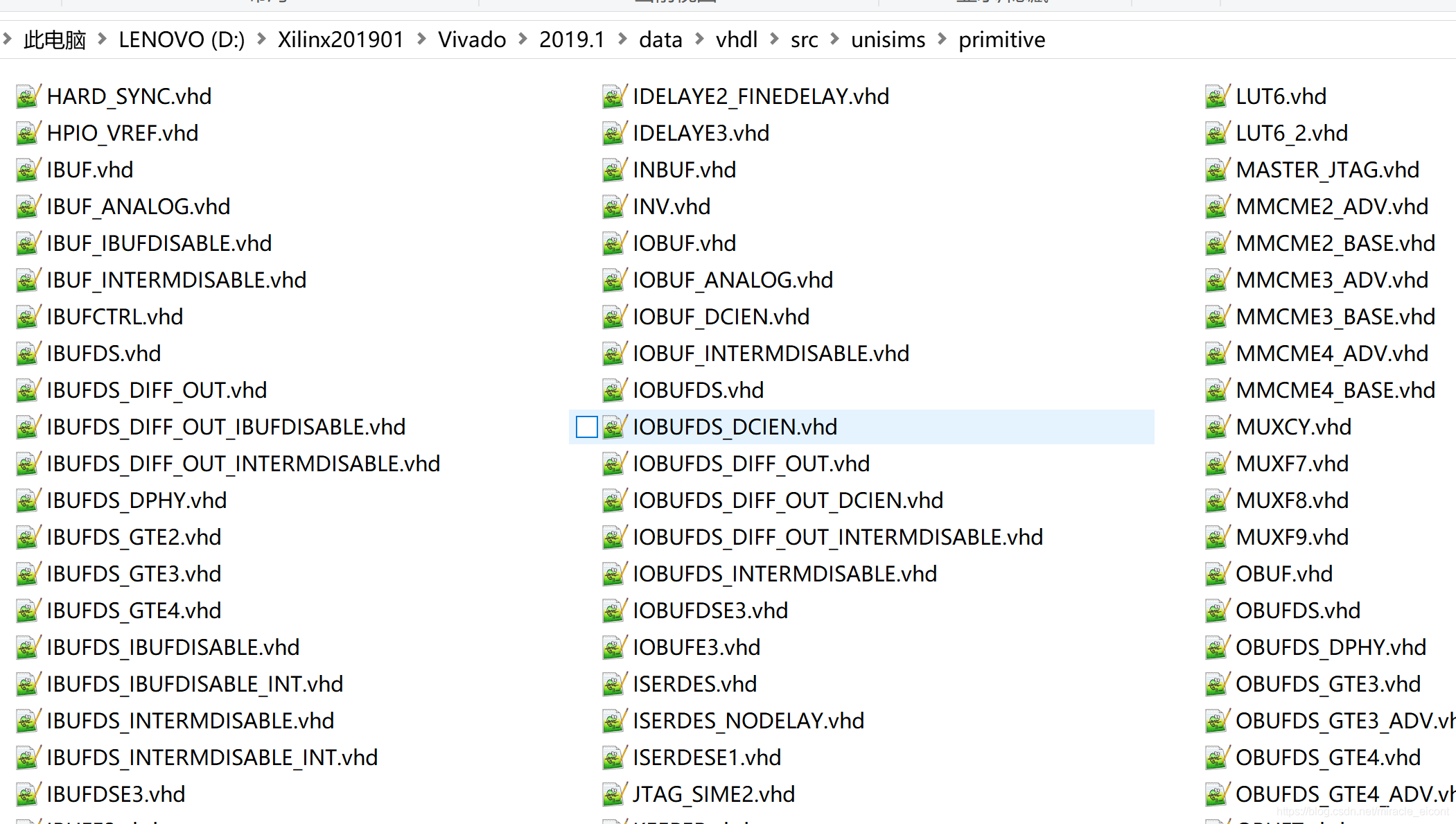

上图中VHDL和Verilog目录有许多基本元件件的描述,当一个项目想摆脱对某公司器件的依赖时,打算从基本元件自己描述起,比如寄存器,触发器等,可以直接用来修改。注意文件所在路径

-

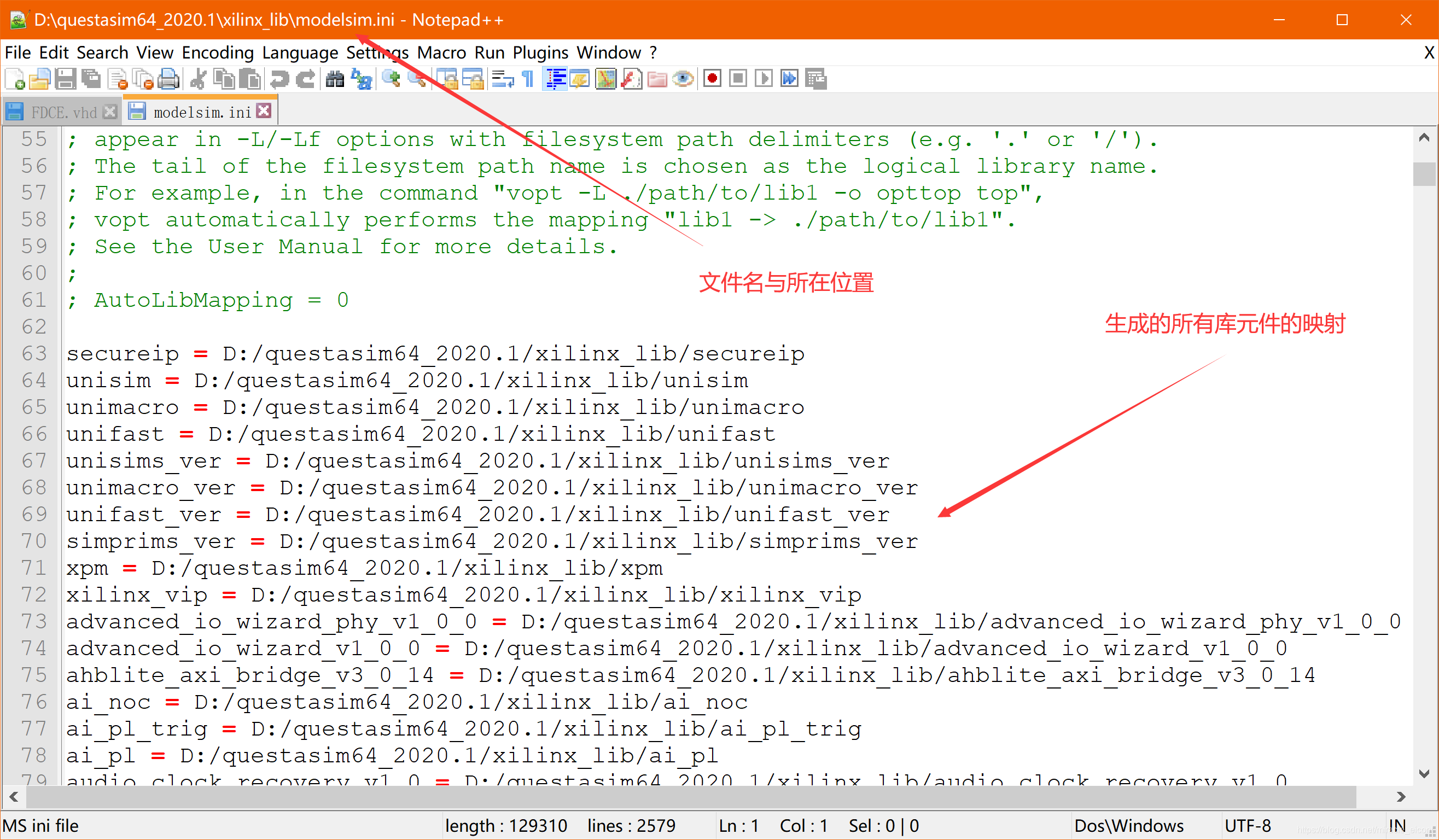

用Vivado的库编译工具compile_simlib为Questasim编译库时,会在生成库的目录(比如放在<questasim_install_dir>\xilinx_lib)下生成一个modelsim.ini文件,这个文件如下图,这个文件中对库的引用语句都已自动生成,可以直接复制到Questasim自己的modelsim.ini(在<questasim_install_dir>\)中,比自己写方便多了。

-

生成库有两种方法:一种是用Vivado的IDE,另一种是TCL命令。

-

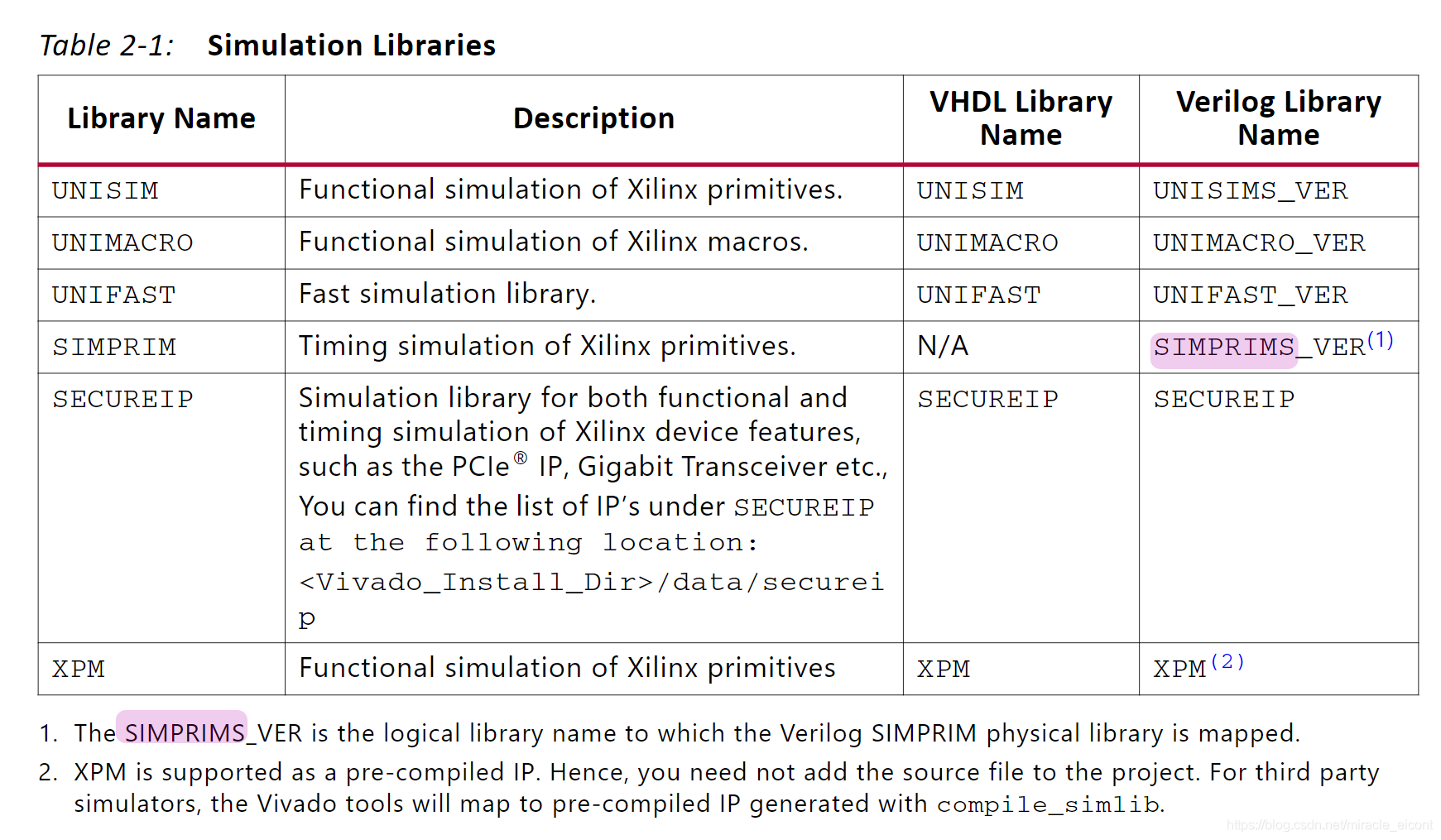

VHDL语言没有simprim库,这点要注意,如下图

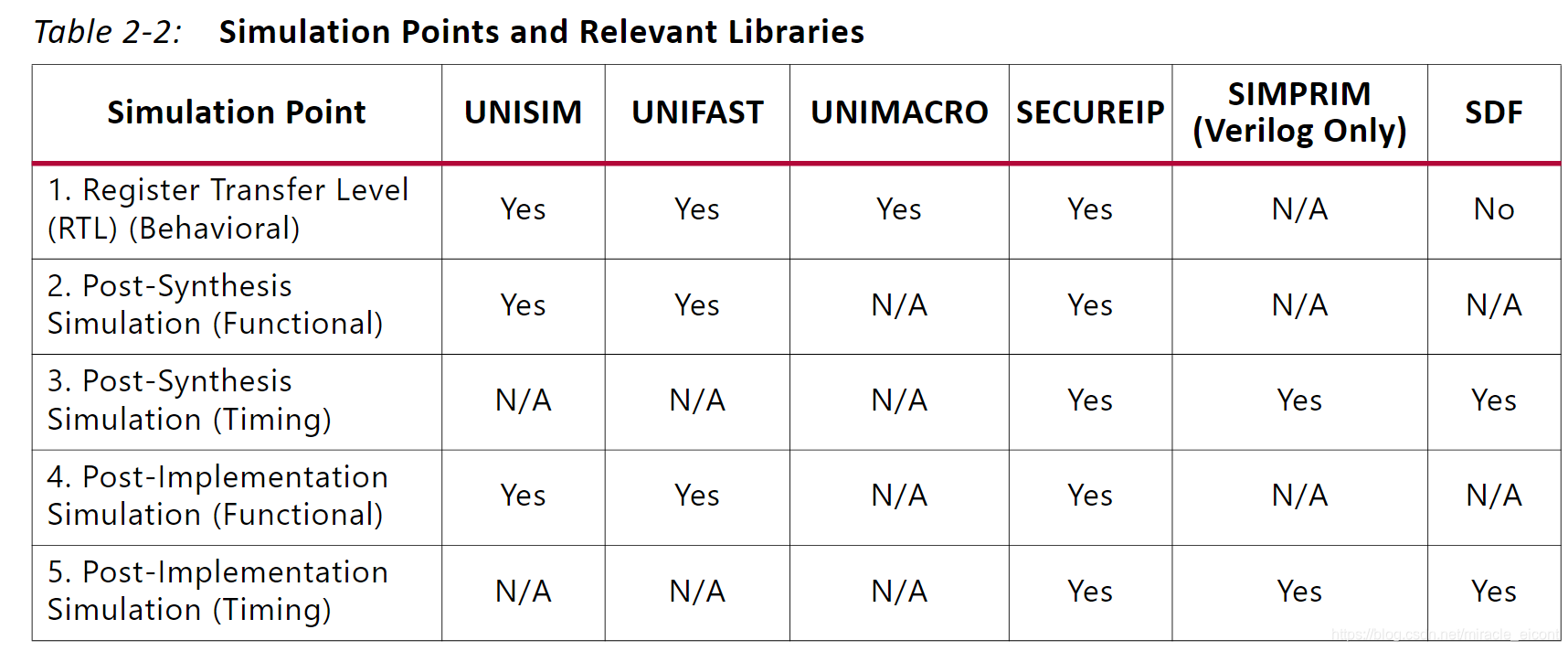

- RTL级仿真、综合后功能仿真、综合后时序 仿真、实现后功能仿真和实现后时序 仿真,需要不同的库支持,如下图

- 至于每个库的作用及其他细节,可以参考UG900