PCI-Express(peripheral component interconnect express)是一种高速串行计算机扩展总线标准,是由英特尔在2001年提出的。PCIe属于高速串行点对点双通道高带宽传输,所连接的设备分配独享通道带宽,不共享总线带宽,主要支持主动电源管理,错误报告,端对端的可靠性传输,热插拔以及服务质量(QOS)等功能。是PCI的更高发展,PCIe比以前的标准有许多改进,包括更高的最大系统总线吞吐量,更低的I/O引脚数量和更小的物理尺寸,更好的总线设备性能缩放,更详细的错误检测和报告机制(高级错误报告,AER)和本机热插拔功能。PCIe标准的更新版本为I/O虚拟化提供了硬件支持。PCIe的主要优势在于其减少延迟的能力。PCIe设备和PCIe总线直接相连,使缓存和数据更接近CPU。他们消除了传统存储协议的开销,并且EMC公司认为在合适的条件下能实现远远优于从08年开始销售的串列SCSI和SATA的固态硬盘SSD的性能。

在概念上,PCI Express总线是较旧的PCI/ PCI-X总线的高速串行替换。PCI Express总线与旧PCI之间的主要区别之一是总线拓扑。 PCI使用共享并行总线架构,其中PCI主机和所有设备共享一组通用的地址,数据和控制线。 相比之下,PCI Express基于点到点拓扑,单独的串行链路将每个设备连接到根系统(主机)。 由于其共享总线拓扑,可以对单个方向上的PCI总线进行仲裁(在多个主机的情况下),并且一次限制为一个主机。 此外,旧的PCI时钟方案将总线时钟限制在总线上最慢的外设(不管总线事务中涉及的设备如何)。 相比之下,PCI Express总线链路支持任何两个端点之间的全双工通信,同时跨多个端点的并发访问没有固有的限制。PCI插槽和PCI Express插槽不可互换。

单通道PCI Express(×1)卡可以插入多通道插槽(×4,×8等),初始化周期自动协商最高相互支持的通道数。该链接可以动态地自动配置自己,以便使用较少的通道,在存在不良或不可靠的通道的情况下提供故障容限。

多通道串行设计增加了灵活性,其能够为较慢的设备分配较少的通道。

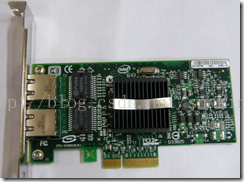

1. PCI-E插槽及金手指实物图

PCI-E插槽,从上至下依次为PCI-E 4X、PCI-E 16X、PCI-E 1X。

PCI-E 1X金手指:

PCI-E 4X金手指:

PCI-E 16X金手指:

2. PCI-E接口定义

说明:

| Ground pin | Zero volt reference | ||

| Power pin | Supplies power to the PCIe card / 为PCIe卡供电 | ||

| Card-to-host pin | Signal from the card to the motherboard / 从卡到主板的信号 | ||

| Host-to-card pin | Signal from the motherboard to the card / 从主板到卡的信号 | ||

| Open drain | May be pulled low or sensed by multiple cards / 可能拉低或由多张卡感应 | ||

| Sense pin / 感应针 | Tied together on card / 绑在一张卡上 | ||

| Reserved | Not presently used, do not connect | ||

| PCI-Express Connector Pin-Out / PCIE连接器引脚 | ||||

| Pin | Side B Connector / B侧 | Side A Connector / A侧 | ||

| # | Name | Description | Name | Description |

| 1 | +12v | +12 volt power /主电源引脚 | PRSNT#1 | Hot plug presence detect / 热插拔存在检测,必须连接到最远的PRSNT2 # |

| 2 | +12v | +12 volt power | +12v | +12 volt power |

| 3 | +12v | +12 volt power /有的标为保留针脚RSVD | +12v | +12 volt power |

| 4 | GND | Ground | GND | Ground |

| 5 | SMCLK | SMBus clock /系统管理总线 | JTAG2 | TCK |

| 6 | SMDAT | SMBus data | JTAG3 | TDI |

| 7 | GND | Ground | JTAG4 | TDO |

| 8 | +3.3v | +3.3 volt power | JTAG5 | TMS |

| 9 | JTAG1 | +TRST# | +3.3v | +3.3 volt power |

| 10 | 3.3Vaux | 3.3v volt power /备用(辅助)电源 | +3.3v | +3.3 volt power |

| 11 | WAKE# | Link Reactivation /链接激活信号 | PWRGD | Power Good /电源准备好信号 有歧义,有的当做复位用 |

| Mechanical Key | ||||

| 12 | RSVD | Reserved /有的标为CLKREQ#,请求运行时钟 | GND | Ground |

| 13 | GND | Ground | REFCLK+ | Reference Clock |

| 14 | HSOp(0) | Transmitter Lane 0, | REFCLK- | Differential pair |

| 15 | HSOn(0) | Differential pair | GND | Ground |

| 16 | GND | Ground | HSIp(0) | Receiver Lane 0, |

| 17 | PRSNT#2 | Hotplug detect / 热插拔存在检测 | HSIn(0) | Differential pair |

| 18 | GND | Ground | GND | Ground |

| End of the 1X connector / PCI Express×1卡在引脚18处结束 | ||||

| 19 | HSOp(1) | Transmitter Lane 1, | RSVD | Reserved |

| 20 | HSOn(1) | Differential pair | GND | Ground |

| 21 | GND | Ground | HSIp(1) | Receiver Lane 1, |

| 22 | GND | Ground | HSIn(1) | Differential pair |

| 23 | HSOp(2) | Transmitter Lane 2, | GND | Ground |

| 24 | HSOn(2) | Differential pair | GND | Ground |

| 25 | GND | Ground | HSIp(2) | Receiver Lane 2, |

| 26 | GND | Ground | HSIn(2) | Differential pair |

| 27 | HSOp(3) | Transmitter Lane 3, | GND | Ground |

| 28 | HSOn(3) | Differential pair | GND | Ground |

| 29 | GND | Ground | HSIp(3) | Receiver Lane 3, |

| 30 | RSVD | Reserved | HSIn(3) | Differential pair |

| 31 | PRSNT#2 | Hot plug detect | GND | Ground |

| 32 | GND | Ground | RSVD | Reserved |

| End of the 4X connector / PCI Express×4带宽模式在引脚32处结束 | ||||

| 33 | HSOp(4) | Transmitter Lane 4, | RSVD | Reserved |

| 34 | HSOn(4) | Differential pair | GND | Ground |

| 35 | GND | Ground | HSIp(4) | Receiver Lane 4, |

| 36 | GND | Ground | HSIn(4) | Differential pair |

| 37 | HSOp(5) | Transmitter Lane 5, | GND | Ground |

| 38 | HSOn(5) | Differential pair | GND | Ground |

| 39 | GND | Ground | HSIp(5) | Receiver Lane 5, |

| 40 | GND | Ground | HSIn(5) | Differential pair |

| 41 | HSOp(6) | Transmitter Lane 6, | GND | Ground |

| 42 | HSOn(6) | Differential pair | GND | Ground |

| 43 | GND | Ground | HSIp(6) | Receiver Lane 6, |

| 44 | GND | Ground | HSIn(6) | Differential pair |

| 45 | HSOp(7) | Transmitter Lane 7, | GND | Ground |

| 46 | HSOn(7) | Differential pair | GND | Ground |

| 47 | GND | Ground | HSIp(7) | Receiver Lane 7, |

| 48 | PRSNT#2 | Hot plug detect | HSIn(7) | Differential pair |

| 49 | GND | Ground | GND | Ground |

| End of the 8X connector / PCI Express×8卡在引脚49处结束 | ||||

| 50 | HSOp(8) | Transmitter Lane 8, | RSVD | Reserved |

| 51 | HSOn(8) | Differential pair | GND | Ground |

| 52 | GND | Ground | HSIp(8) | Receiver Lane 8, |

| 53 | GND | Ground | HSIn(8) | Differential pair |

| 54 | HSOp(9) | Transmitter Lane 9, | GND | Ground |

| 55 | HSOn(9) | Differential pair | GND | Ground |

| 56 | GND | Ground | HSIp(9) | Receiver Lane 9, |

| 57 | GND | Ground | HSIn(9) | Differential pair |

| 58 | HSOp(10) | Transmitter Lane 10, | GND | Ground |

| 59 | HSOn(10) | Differential pair | GND | Ground |

| 60 | GND | Ground | HSIp(10) | Receiver Lane 10, |

| 61 | GND | Ground | HSIn(10) | Differential pair |

| 62 | HSOp(11) | Transmitter Lane 11, | GND | Ground |

| 63 | HSOn(11) | Differential pair | GND | Ground |

| 64 | GND | Ground | HSIp(11) | Receiver Lane 11, |

| 65 | GND | Ground | HSIn(11) | Differential pair |

| 66 | HSOp(12) | Transmitter Lane 12, | GND | Ground |

| 67 | HSOn(12) | Differential pair | GND | Ground |

| 68 | GND | Ground | HSIp(12) | Receiver Lane 12, |

| 69 | GND | Ground | HSIn(12) | Differential pair |

| 70 | HSOp(13) | Transmitter Lane 13, | GND | Ground |

| 71 | HSOn(13) | Differential pair | GND | Ground |

| 72 | GND | Ground | HSIp(13) | Receiver Lane 13, |

| 73 | GND | Ground | HSIn(13) | Differential pair |

| 74 | HSOp(14) | Transmitter Lane 14, | GND | Ground |

| 75 | HSOn(14) | Differential pair | GND | Ground |

| 76 | GND | Ground | HSIp(14) | Receiver Lane 14, |

| 77 | GND | Ground | HSIn(14) | Differential pair |

| 78 | HSOp(15) | Transmitter Lane 15, | GND | Ground |

| 79 | HSOn(15) | Differential pair | GND | Ground |

| 80 | GND | Ground | HSIp(15) | Receiver Lane 15, |

| 81 | PRSNT#2 | Hot plug present detect | HSIn(15) | Differential pair |

| 82 | RSVD#2 | Hot Plug Detect | GND | Ground |

| End of the 16X connector | ||||

PCIE规格

|

传输通道数

|

脚Pin总数

|

主接口区Pin数

|

总 长 度

|

主接口区 长度

|

|

1

|

36

|

14

|

25 mm

|

7.65 mm

|

|

4

|

64

|

42

|

39 mm

|

21.65 mm

|

|

8

|

98

|

76

|

56 mm

|

38.65 mm

|

|

16

|

164

|

142

|

89 mm

|

71.65 mm

|

|

规格

|

总线宽度

|

工作时脉

|

传输速率

|

|

PCI-E x1

|

8 位

|

2.5 GHz

|

512 MiB/s

|

|

PCI-E x2

|

8 位

|

2.5 GHz

|

1.0 GiB/s

|

|

PCI-E x4

|

8 位

|

2.5 GHz

|

2.0 GiB/s

|

|

PCI-E x8

|

8 位

|

2.5 GHz

|

4.0 GiB/s

|

|

PCI-E x16

|

8 位

|

2.5 GHz

|

8.0 GiB/s

|

| PCI Express 版本 | 行代码 | 传输速率 | 吞吐量 | |||

| ×1 | ×4 | ×8 | ×16 | |||

| 1.0 | 8b/10b | 2.5GT/s | 250MB/s | 1GB/s | 2GB/s | 4GB/s |

| 2.0 | 8b/10b | 5GT/s | 500MB/s | 2GB/s | 4GB/s | 8GB/s |

| 3.0 | 128b/130b | 8GT/s | 984.6MB/s | 3.938GB/s | 7.877GB/s | 15.754GB/s |

| 4.0 | 128b/130b | 16GT/s | 1.969GB/s | 7.877GB/s | 15.754GB/s | 31.508GB/s |

| 5.0 | 128b/130b | 32 or 25GT/s | 3.9 or 3.08GB/s | 15.8 or 12.3GB/s | 31.5 or 24.6GB/s | 63.0 or 49.2GB/s |

PS:带宽、传输速率与吞吐量区别

举个例吧

一条路每秒最多能过100辆车(宽带就相当于100辆/秒)。

而并不是每秒都会有100辆车过,假如第一秒有0辆,第二秒有10辆...,(但是最多不能超过100辆)。

所以有第1秒0辆/秒,第2秒10辆/秒,第3秒30辆/秒,这不能说带宽多少吧,于是就用吞吐量表示具体时间通过的量有多少(也有可能等于带宽的量)。

由此可知带宽是说的是最大值速率,吞吐量说的是某时刻速率。但吞吐量不能超过最大速率。

传输速率又称作带宽,在数据传输的过程中,两个设备之间数据流动的物理速度称为传输速率,单位bps。各种传输媒介中信号的流动速度是恒定的,即使数据链路的传输速率不同,也不会出现忽快忽慢的情况。传输速率不是指单位数据流动的速度有多快,而是指单位时间内传输的数据量有多少。

以我们生活中的道路交通为例,低速数据链路如同车道较少无法让很多车同时通过的情况,与之相反,高速数据链路就相当于有多个车道,一次允许更多车辆行驶的道路。带宽越大网络传输能力就越强。

主机之间实际的传输速率被称作吞吐量。其单位与带宽相同,都是bps(Bits per second)。吞吐量不仅衡量带宽,同时也衡量主机的CPU处理能力、网络的拥堵程度、报文中数据字段的占有份额等信息。