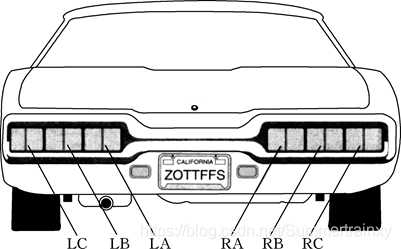

汽车尾灯发出的信号主要是给后面行驶汽车的司机看的,通常汽车驾驶室有刹车开关(HAZ)、左转弯开关(LEFT)和右转弯开关(RIGHT),司机通过操作这3个开关给出车辆的行驶状态。假设在汽车尾部左、右两侧各有3个指示灯,分别用LA、LB、LC、RA、RB、RC表示。这些灯的亮、灭规律如下:

1)汽车正常行驶时,尾部两侧的6个灯全部熄灭。

2)刹车时,汽车尾灯工作在告警状态,所有6个灯按一定频率闪烁。

3)左转弯时,左侧3个灯轮流顺序点亮,其规律如图(a)所示,右侧灯全灭。

4)右转弯时,右侧3个灯轮流顺序点亮,其规律如图(b)所示,左侧灯全灭。

假设电路的输入时钟信号为CP,CP的频率对应于汽车尾灯所要求的闪烁频率。试根据上述要求设计出一个时钟同步的状态机来控制汽车的尾灯,并进行仿真测试。

采用三段式状态机

汽车尾灯控制电路代码

module carlight_541_V3(CP,nCR,HAZ,LEFT,RIGHT,LA,LB,LC,RA,RB,RC);

input nCR,CP;

input HAZ,LEFT,RIGHT;

output reg LA,LB,LC,RA,RB,RC;

reg [2:0]Current_state,Next_state;

parameter [2:0]IDLE=3'b000,L1=3'b001,L2=3'b010,L3=3'b011,R1=3'b100,R2=3'b101,R3=3'b110,LR3=3'b111;

//时序逻辑

always @(posedge CP or negedge nCR)

begin

if (~nCR)

Current_state<=IDLE;

else

Current_state<=Next_state;

end

//组合逻辑

always @(Current_state or HAZ or LEFT or RIGHT)

begin

Next_state=3'bxxx;

case(Current_state)

IDLE:begin

if(LEFT&&(!HAZ)&&(!RIGHT)) Next_state=L1;

else if (HAZ+LEFT&&RIGHT) Next_state=LR3;

else if (RIGHT&&(!HAZ)&&(!LEFT)) Next_state=R1;

else Next_state=IDLE; //

end

L1:begin

if(!HAZ) Next_state=L2;

else Next_state=LR3;

end

L2:begin

if(!HAZ) Next_state=L3;

else Next_state=LR3;

end

L3:begin

Next_state=IDLE;

end

R1:begin

if(!HAZ) Next_state=R2;

else Next_state=LR3;

end

R2:begin

if(!HAZ) Next_state=R3;

else Next_state=LR3;

end

R3:begin

Next_state=IDLE;

end

LR3:begin

Next_state=IDLE;

end

endcase

end

//输出逻辑

always @(posedge CP or negedge nCR)

begin

if(~nCR)

begin

LC=1'b0;LB=1'b0;LA=1'b0;RC=1'b0;RB=1'b0;RA=1'b0;

end

else begin

LC=1'b0;LB=1'b0;LA=1'b0;RC=1'b0;RB=1'b0;RA=1'b0;

case(Current_state)

IDLE:begin LC=1'b0;LB=1'b0;LA=1'b0;RC=1'b0;RB=1'b0;RA=1'b0; end

L1:begin LC=1'b0;LB=1'b0;LA=1'b1;RC=1'b0;RB=1'b0;RA=1'b0; end

L2:begin LC=1'b0;LB=1'b1;LA=1'b1;RC=1'b0;RB=1'b0;RA=1'b0; end

L3:begin LC=1'b1;LB=1'b1;LA=1'b1;RC=1'b0;RB=1'b0;RA=1'b0; end

R1:begin LC=1'b0;LB=1'b0;LA=1'b0;RC=1'b0;RB=1'b0;RA=1'b1; end

R2:begin LC=1'b0;LB=1'b0;LA=1'b0;RC=1'b0;RB=1'b1;RA=1'b1; end

R3:begin LC=1'b0;LB=1'b0;LA=1'b0;RC=1'b1;RB=1'b1;RA=1'b1; end

LR3:begin LC=1'b1;LB=1'b1;LA=1'b1;RC=1'b1;RB=1'b1;RA=1'b1; end

endcase

end

end

endmodule

- 测试文件

`timescale 1ns/1ns

module carlight_541_V3_test;

reg CP,nCR,HAZ,LEFT,RIGHT;

wire LA,LB,LC,RA,RB,RC;

carlight_541_V3 u0(CP,nCR,HAZ,LEFT,RIGHT,LA,LB,LC,RA,RB,RC);

initial

begin

nCR=1'b0;

nCR= #20 1'b1;

HAZ=1'b0;LEFT=1'b0;RIGHT=1'b0;

#200 HAZ=1'b0;LEFT=1'b0;RIGHT=1'b0;

#200 HAZ=1'b0;LEFT=1'b0;RIGHT=1'b1; //RIGHT

#200 HAZ=1'b0;LEFT=1'b1;RIGHT=1'b0; //LEFT

#200 HAZ=1'b0;LEFT=1'b1;RIGHT=1'b1;

#200 HAZ=1'b1;LEFT=1'b0;RIGHT=1'b0; //HAZ

#200 HAZ=1'b1;LEFT=1'b0;RIGHT=1'b1;

#200 HAZ=1'b1;LEFT=1'b1;RIGHT=1'b0;

#200 HAZ=1'b1;LEFT=1'b1;RIGHT=1'b1;

#200 $stop;

end

always

begin

CP=1'b0;

CP= #10 1'b1;

#10;

end

endmodule

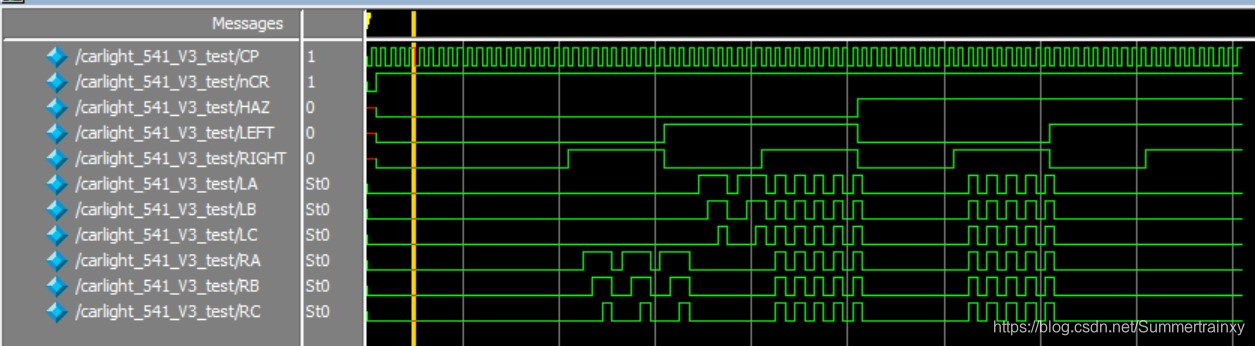

3.仿真结果