SC60开发板默认是不支持CAN接口的,需要外接转换芯片,选取MICROCHIP的MCP25625这一款。

芯片特点如下:

• Stand-Alone CAN 2.0B Controller with Integrated CAN Transceiver and Serial Peripheral

Interface (SPI)

• Up to 1 Mb/s Operation

• Very Low Standby Current (10 μA, typical)

• Up to 10 MHz SPI Clock Speed

• Interfaces Directly with Microcontrollers with 2.7V to 5.5V I/Os

• Available in SSOP-28L and 6x6 QFN-28L

• Temperature Ranges: - Extended (E): -40°C to +125°C

最主要的特点是集成了Transceiver,避免了外接Transceiver的电路,设计简单。

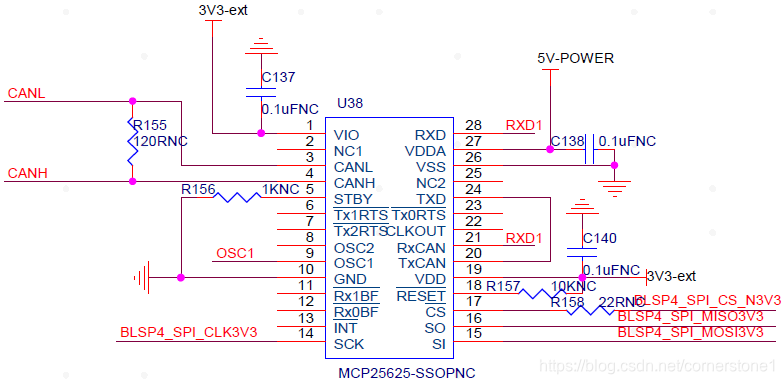

参考原理图:

osc1接8M晶振,CANL和CANH连接到外部CAN网络,串联120欧的阻抗匹配,使用4线SPI和主控通讯。

驱动参考:

/*

* CAN bus driver for Microchip 251x CAN Controller with SPI Interface

*

* MCP2510 support and bug fixes by Christian Pellegrin

* <[email protected]>

*

* Copyright 2009 Christian Pellegrin EVOL S.r.l.

*

* Copyright 2007 Raymarine UK, Ltd. All Rights Reserved.

* Written under contract by:

* Chris Elston, Katalix Systems, Ltd.

*

* Based on Microchip MCP251x CAN controller driver written by

* David Vrabel, Copyright 2006 Arcom Control Systems Ltd.

*

* Based on CAN bus driver for the CCAN controller written by

* - Sascha Hauer, Marc Kleine-Budde, Pengutronix

* - Simon Kallweit, intefo AG

* Copyright 2007

*

* This program is free software; you can redistribute it and/or modify

* it under the terms of the version 2 of the GNU General Public License

* as published by the Free Software Foundation

*

* This program is distributed in the hope that it will be useful,

* but WITHOUT ANY WARRANTY; without even the implied warranty of

* MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

* GNU General Public License for more details.

*

* You should have received a copy of the GNU General Public License

* along with this program; if not, write to the Free Software

* Foundation, Inc., 59 Temple Place, Suite 330, Boston, MA 02111-1307 USA

*

*

*

* Your platform definition file should specify something like:

*

* static struct mcp251x_platform_data mcp251x_info = {

* .oscillator_frequency = 8000000,

* .board_specific_setup = &mcp251x_setup,

* .power_enable = mcp251x_power_enable,

* .transceiver_enable = NULL,

* };

*

* static struct spi_board_info spi_board_info[] = {

* {

* .modalias = "mcp2510",

* // or "mcp2515" depending on your controller

* .platform_data = &mcp251x_info,

* .irq = IRQ_EINT13,

* .max_speed_hz = 2*1000*1000,

* .chip_select = 2,

* },

* };

*

* Please see mcp251x.h for a description of the fields in

* struct mcp251x_platform_data.

*

*/

#include <linux/can/core.h>

#include <linux/can/dev.h>

#include <linux/can/led.h>

#include <linux/can/platform/mcp251x.h>

#include <linux/completion.h>

#include <linux/delay.h>

#include <linux/device.h>

#include <linux/dma-mapping.h>

#include <linux/freezer.h>

#include <linux/interrupt.h>

#include <linux/io.h>

#include <linux/kernel.h>

#include <linux/module.h>

#include <linux/netdevice.h>

#include <linux/platform_device.h>

#include <linux/slab.h>

#include <linux/spi/spi.h>

#include <linux/uaccess.h>

//stone added

#include <linux/of_gpio.h>

/* SPI interface instruction set */

#define INSTRUCTION_WRITE 0x02

#define INSTRUCTION_READ 0x03

#define INSTRUCTION_BIT_MODIFY 0x05

#define INSTRUCTION_LOAD_TXB(n) (0x40 + 2 * (n))

#define INSTRUCTION_READ_RXB(n) (((n) == 0) ? 0x90 : 0x94)

#define INSTRUCTION_RESET 0xC0

#define RTS_TXB0 0x01

#define RTS_TXB1 0x02

#define RTS_TXB2 0x04

#define INSTRUCTION_RTS(n) (0x80 | ((n) & 0x07))

/* MPC251x registers */

#define CANSTAT 0x0e

#define CANCTRL 0x0f

# define CANCTRL_REQOP_MASK 0xe0

# define CANCTRL_REQOP_CONF 0x80

# define CANCTRL_REQOP_LISTEN_ONLY 0x60

# define CANCTRL_REQOP_LOOPBACK 0x40

# define CANCTRL_REQOP_SLEEP 0x20

# define CANCTRL_REQOP_NORMAL 0x00

# define CANCTRL_OSM 0x08

# define CANCTRL_ABAT 0x10

#define TEC 0x1c

#define REC 0x1d

#define CNF1 0x2a

# define CNF1_SJW_SHIFT 6

#define CNF2 0x29

# define CNF2_BTLMODE 0x80

# define CNF2_SAM 0x40

# define CNF2_PS1_SHIFT 3

#define CNF3 0x28

# define CNF3_SOF 0x08

# define CNF3_WAKFIL 0x04

# define CNF3_PHSEG2_MASK 0x07

#define CANINTE 0x2b

# define CANINTE_MERRE 0x80

# define CANINTE_WAKIE 0x40

# define CANINTE_ERRIE 0x20

# define CANINTE_TX2IE 0x10

# define CANINTE_TX1IE 0x08

# define CANINTE_TX0IE 0x04

# define CANINTE_RX1IE 0x02

# define CANINTE_RX0IE 0x01

#define CANINTF 0x2c

# define CANINTF_MERRF 0x80

# define CANINTF_WAKIF 0x40

# define CANINTF_ERRIF 0x20

# define CANINTF_TX2IF 0x10

# define CANINTF_TX1IF 0x08

# define CANINTF_TX0IF 0x04

# define CANINTF_RX1IF 0x02

# define CANINTF_RX0IF 0x01

# define CANINTF_RX (CANINTF_RX0IF | CANINTF_RX1IF)

# define CANINTF_TX (CANINTF_TX2IF | CANINTF_TX1IF | CANINTF_TX0IF)

# define CANINTF_ERR (CANINTF_ERRIF)

#define EFLG 0x2d

# define EFLG_EWARN 0x01

# define EFLG_RXWAR 0x02

# define EFLG_TXWAR 0x04

# define EFLG_RXEP 0x08

# define EFLG_TXEP 0x10

# define EFLG_TXBO 0x20

# define EFLG_RX0OVR 0x40

# define EFLG_RX1OVR 0x80

#define TXBCTRL(n) (((n) * 0x10) + 0x30 + TXBCTRL_OFF)

# define TXBCTRL_ABTF 0x40

# define TXBCTRL_MLOA 0x20

# define TXBCTRL_TXERR 0x10

# define TXBCTRL_TXREQ 0x08

#define TXBSIDH(n) (((n) * 0x10) + 0x30 + TXBSIDH_OFF)

# define SIDH_SHIFT 3

#define TXBSIDL(n) (((n) * 0x10) + 0x30 + TXBSIDL_OFF)

# define SIDL_SID_MASK 7

# define SIDL_SID_SHIFT 5

# define SIDL_EXIDE_SHIFT 3

# define SIDL_EID_SHIFT 16

# define SIDL_EID_MASK 3

#define TXBEID8(n) (((n) * 0x10) + 0x30 + TXBEID8_OFF)

#define TXBEID0(n) (((n) * 0x10) + 0x30 + TXBEID0_OFF)

#define TXBDLC(n) (((n) * 0x10) + 0x30 + TXBDLC_OFF)

# define DLC_RTR_SHIFT 6

#define TXBCTRL_OFF 0

#define TXBSIDH_OFF 1

#define TXBSIDL_OFF 2

#define TXBEID8_OFF 3

#define TXBEID0_OFF 4

#define TXBDLC_OFF 5

#define TXBDAT_OFF 6

#define RXBCTRL(n) (((n) * 0x10) + 0x60 + RXBCTRL_OFF)

# define RXBCTRL_BUKT 0x04

# define RXBCTRL_RXM0 0x20

# define RXBCTRL_RXM1 0x40

#define RXBSIDH(n) (((n) * 0x10) + 0x60 + RXBSIDH_OFF)

# define RXBSIDH_SHIFT 3

#define RXBSIDL(n) (((n) * 0x10) + 0x60 + RXBSIDL_OFF)

# define RXBSIDL_IDE 0x08

# define RXBSIDL_SRR 0x10

# define RXBSIDL_EID 3

# define RXBSIDL_SHIFT 5

#define RXBEID8(n) (((n) * 0x10) + 0x60 + RXBEID8_OFF)

#define RXBEID0(n) (((n) * 0x10) + 0x60 + RXBEID0_OFF)

#define RXBDLC(n) (((n) * 0x10) + 0x60 + RXBDLC_OFF)

# define RXBDLC_LEN_MASK 0x0f

# define RXBDLC_RTR 0x40

#define RXBCTRL_OFF 0

#define RXBSIDH_OFF 1

#define RXBSIDL_OFF 2

#define RXBEID8_OFF 3

#define RXBEID0_OFF 4

#define RXBDLC_OFF 5

#define RXBDAT_OFF 6

#define RXFSIDH(n) ((n) * 4)

#define RXFSIDL(n) ((n) * 4 + 1)

#define RXFEID8(n) ((n) * 4 + 2)

#define RXFEID0(n) ((n) * 4 + 3)

#define RXMSIDH(n) ((n) * 4 + 0x20)

#define RXMSIDL(n) ((n) * 4 + 0x21)

#define RXMEID8(n) ((n) * 4 + 0x22)

#define RXMEID0(n) ((n) * 4 + 0x23)

#define GET_BYTE(val, byte) \

(((val) >> ((byte) * 8)) & 0xff)

#define SET_BYTE(val, byte) \

(((val) & 0xff) << ((byte) * 8))

/*

* Buffer size required for the largest SPI transfer (i.e., reading a

* frame)

*/

#define CAN_FRAME_MAX_DATA_LEN 8

#define SPI_TRANSFER_BUF_LEN (6 + CAN_FRAME_MAX_DATA_LEN)

#define CAN_FRAME_MAX_BITS 128

#define TX_ECHO_SKB_MAX 1

#define DEVICE_NAME "mcp25625"

static int mcp251x_enable_dma; /* Enable SPI DMA. Default: 0 (Off) */

module_param(mcp251x_enable_dma, int, S_IRUGO);

MODULE_PARM_DESC(mcp251x_enable_dma, "Enable SPI DMA. Default: 0 (Off)");

static const struct can_bittiming_const mcp251x_bittiming_const = {

.name = DEVICE_NAME,

.tseg1_min = 3,

.tseg1_max = 16,

.tseg2_min = 2,

.tseg2_max = 8,

.sjw_max = 4,

.brp_min = 1,

.brp_max = 64,

.brp_inc = 1,

};

enum mcp251x_model {

CAN_MCP251X_MCP2510 = 0x2510,

CAN_MCP251X_MCP2515 = 0x2515,

};

struct mcp251x_priv {

struct can_priv can;

struct net_device *net;

struct spi_device *spi;

enum mcp251x_model model;

struct mutex mcp_lock; /* SPI device lock */

u8 *spi_tx_buf;

u8 *spi_rx_buf;

dma_addr_t spi_tx_dma;

dma_addr_t spi_rx_dma;

struct sk_buff *tx_skb;

int tx_len;

struct workqueue_struct *wq;

struct work_struct tx_work;

struct work_struct restart_work;

//stone added

struct work_struct irq_work;

int force_quit;

int after_suspend;

#define AFTER_SUSPEND_UP 1

#define AFTER_SUSPEND_DOWN 2

#define AFTER_SUSPEND_POWER 4

#define AFTER_SUSPEND_RESTART 8

int restart_tx;

};

#define MCP251X_IS(_model) \

static inline int mcp251x_is_##_model(struct spi_device *spi) \

{ \

struct mcp251x_priv *priv = spi_get_drvdata(spi); \

return priv->model == CAN_MCP251X_MCP##_model; \

}

MCP251X_IS(2510);

MCP251X_IS(2515);

//Begin:stone added

static struct mcp251x_platform_data mcp251x_info = {

.oscillator_frequency = 8000000,

//.board_specific_setup = &mcp251x_setup,

//.power_enable = mcp251x_power_enable,

.transceiver_enable = NULL,

};

//End:stone added

static void mcp251x_clean(struct net_device *net)

{

struct mcp251x_priv *priv = netdev_priv(net);

if (priv->tx_skb || priv->tx_len)

net->stats.tx_errors++;

if (priv->tx_skb)

dev_kfree_skb(priv->tx_skb);

if (priv->tx_len)

can_free_echo_skb(priv->net, 0);

priv->tx_skb = NULL;

priv->tx_len = 0;

}

/*

* Note about handling of error return of mcp251x_spi_trans: accessing

* registers via SPI is not really different conceptually than using

* normal I/O assembler instructions, although it's much more

* complicated from a practical POV. So it's not advisable to always

* check the return value of this function. Imagine that every

* read{b,l}, write{b,l} and friends would be bracketed in "if ( < 0)

* error();", it would be a great mess (well there are some situation

* when exception handling C++ like could be useful after all). So we

* just check that transfers are OK at the beginning of our

* conversation with the chip and to avoid doing really nasty things

* (like injecting bogus packets in the network stack).

*/

static int mcp251x_spi_trans(struct spi_device *spi, int len)

{

struct mcp251x_priv *priv = spi_get_drvdata(spi);

struct spi_transfer t = {

.tx_buf = priv->spi_tx_buf,

.rx_buf = priv->spi_rx_buf,

.len = len,

.cs_change = 0,

};

struct spi_message m;

int ret;

spi_message_init(&m);

if (mcp251x_enable_dma) {

t.tx_dma = priv->spi_tx_dma;

t.rx_dma = priv->spi_rx_dma;

m.is_dma_mapped = 1;

}

spi_message_add_tail(&t, &m);

ret = spi_sync(spi, &m);

if (ret)

dev_err(&spi->dev, "spi transfer failed: ret = %d\n", ret);

return ret;

}

static u8 mcp251x_read_reg(struct spi_device *spi, uint8_t reg)

{

struct mcp251x_priv *priv = spi_get_drvdata(spi);

u8 val = 0;

priv->spi_tx_buf[0] = INSTRUCTION_READ;

priv->spi_tx_buf[1] = reg;

mcp251x_spi_trans(spi, 3);

val = priv->spi_rx_buf[2];

return val;

}

static void mcp251x_read_2regs(struct spi_device *spi, uint8_t reg,

uint8_t *v1, uint8_t *v2)

{

struct mcp251x_priv *priv = spi_get_drvdata(spi);

priv->spi_tx_buf[0] = INSTRUCTION_READ;

priv->spi_tx_buf[1] = reg;

mcp251x_spi_trans(spi, 4);

*v1 = priv->spi_rx_buf[2];

*v2 = priv->spi_rx_buf[3];

}

static void mcp251x_write_reg(struct spi_device *spi, u8 reg, uint8_t val)

{

struct mcp251x_priv *priv = spi_get_drvdata(spi);

priv->spi_tx_buf[0] = INSTRUCTION_WRITE;

priv->spi_tx_buf[1] = reg;

priv->spi_tx_buf[2] = val;

mcp251x_spi_trans(spi, 3);

}

static void mcp251x_write_bits(struct spi_device *spi, u8 reg,

u8 mask, uint8_t val)

{

struct mcp251x_priv *priv = spi_get_drvdata(spi);

priv->spi_tx_buf[0] = INSTRUCTION_BIT_MODIFY;

priv->spi_tx_buf[1] = reg;

priv->spi_tx_buf[2] = mask;

priv->spi_tx_buf[3] = val;

mcp251x_spi_trans(spi, 4);

}

static void mcp251x_hw_tx_frame(struct spi_device *spi, u8 *buf,

int len, int tx_buf_idx)

{

struct mcp251x_priv *priv = spi_get_drvdata(spi);

//stone added

dev_err(&spi->dev, "-----mcp251x_hw_tx_frame-----");

//stone modify

if (mcp251x_is_2510(spi)) {

//if(1){

int i;

for (i = 1; i < TXBDAT_OFF + len; i++)

mcp251x_write_reg(spi, TXBCTRL(tx_buf_idx) + i,

buf[i]);

}

else {

//stone added

dev_err(&spi->dev, "-----mcp251x_hw_tx_frame else-----");

memcpy(priv->spi_tx_buf, buf, TXBDAT_OFF + len);

mcp251x_spi_trans(spi, TXBDAT_OFF + len);

}

}

static void mcp251x_hw_tx(struct spi_device *spi, struct can_frame *frame,

int tx_buf_idx)

{

//stone delete

//struct mcp251x_priv *priv = spi_get_drvdata(spi);

u32 sid, eid, exide, rtr;

u8 buf[SPI_TRANSFER_BUF_LEN];

dev_err(&spi->dev, "-----mcp251x_hw_tx-----");

exide = (frame->can_id & CAN_EFF_FLAG) ? 1 : 0; /* Extended ID Enable */

if (exide)

sid = (frame->can_id & CAN_EFF_MASK) >> 18;

else

sid = frame->can_id & CAN_SFF_MASK; /* Standard ID */

eid = frame->can_id & CAN_EFF_MASK; /* Extended ID */

rtr = (frame->can_id & CAN_RTR_FLAG) ? 1 : 0; /* Remote transmission */

buf[TXBCTRL_OFF] = INSTRUCTION_LOAD_TXB(tx_buf_idx);

buf[TXBSIDH_OFF] = sid >> SIDH_SHIFT;

buf[TXBSIDL_OFF] = ((sid & SIDL_SID_MASK) << SIDL_SID_SHIFT) |

(exide << SIDL_EXIDE_SHIFT) |

((eid >> SIDL_EID_SHIFT) & SIDL_EID_MASK);

buf[TXBEID8_OFF] = GET_BYTE(eid, 1);

buf[TXBEID0_OFF] = GET_BYTE(eid, 0);

buf[TXBDLC_OFF] = (rtr << DLC_RTR_SHIFT) | frame->can_dlc;

memcpy(buf + TXBDAT_OFF, frame->data, frame->can_dlc);

mcp251x_hw_tx_frame(spi, buf, frame->can_dlc, tx_buf_idx);

//stone added this line

mcp251x_write_reg(spi, TXBCTRL(tx_buf_idx), TXBCTRL_TXREQ);//请求发送tx0

/* use INSTRUCTION_RTS, to avoid "repeated frame problem" */

//stone delete

//priv->spi_tx_buf[0] = INSTRUCTION_RTS(1 << tx_buf_idx);

//mcp251x_spi_trans(priv->spi, 1);

}

static void mcp251x_hw_rx_frame(struct spi_device *spi, u8 *buf,

int buf_idx)

{

struct mcp251x_priv *priv = spi_get_drvdata(spi);

if (mcp251x_is_2510(spi)) {

int i, len;

for (i = 1; i < RXBDAT_OFF; i++)

buf[i] = mcp251x_read_reg(spi, RXBCTRL(buf_idx) + i);

len = get_can_dlc(buf[RXBDLC_OFF] & RXBDLC_LEN_MASK);

for (; i < (RXBDAT_OFF + len); i++)

buf[i] = mcp251x_read_reg(spi, RXBCTRL(buf_idx) + i);

} else {

priv->spi_tx_buf[RXBCTRL_OFF] = INSTRUCTION_READ_RXB(buf_idx);

mcp251x_spi_trans(spi, SPI_TRANSFER_BUF_LEN);

memcpy(buf, priv->spi_rx_buf, SPI_TRANSFER_BUF_LEN);

}

}

static void mcp251x_hw_rx(struct spi_device *spi, int buf_idx)

{

struct mcp251x_priv *priv = spi_get_drvdata(spi);

struct sk_buff *skb;

struct can_frame *frame;

u8 buf[SPI_TRANSFER_BUF_LEN];

//stone added debug

int i;

skb = alloc_can_skb(priv->net, &frame);

if (!skb) {

dev_err(&spi->dev, "cannot allocate RX skb\n");

priv->net->stats.rx_dropped++;

return;

}

mcp251x_hw_rx_frame(spi, buf, buf_idx);

//Begin:stone added debug for rx data

dev_err(&spi->dev, "buf_idx=%d\n",buf_idx);

for(i=0; i<SPI_TRANSFER_BUF_LEN; i++)

{

dev_err(&spi->dev, "buf[%d]=%x\n",i,buf[i]);

}

//End:stone added debug for rx data

if (buf[RXBSIDL_OFF] & RXBSIDL_IDE) {

/* Extended ID format */

frame->can_id = CAN_EFF_FLAG;

frame->can_id |=

/* Extended ID part */

SET_BYTE(buf[RXBSIDL_OFF] & RXBSIDL_EID, 2) |

SET_BYTE(buf[RXBEID8_OFF], 1) |

SET_BYTE(buf[RXBEID0_OFF], 0) |

/* Standard ID part */

(((buf[RXBSIDH_OFF] << RXBSIDH_SHIFT) |

(buf[RXBSIDL_OFF] >> RXBSIDL_SHIFT)) << 18);

/* Remote transmission request */

if (buf[RXBDLC_OFF] & RXBDLC_RTR)

frame->can_id |= CAN_RTR_FLAG;

} else {

/* Standard ID format */

frame->can_id =

(buf[RXBSIDH_OFF] << RXBSIDH_SHIFT) |

(buf[RXBSIDL_OFF] >> RXBSIDL_SHIFT);

if (buf[RXBSIDL_OFF] & RXBSIDL_SRR)

frame->can_id |= CAN_RTR_FLAG;

}

/* Data length */

frame->can_dlc = get_can_dlc(buf[RXBDLC_OFF] & RXBDLC_LEN_MASK);

memcpy(frame->data, buf + RXBDAT_OFF, frame->can_dlc);

priv->net->stats.rx_packets++;

priv->net->stats.rx_bytes += frame->can_dlc;

can_led_event(priv->net, CAN_LED_EVENT_RX);

netif_rx_ni(skb);

}

static void mcp251x_hw_sleep(struct spi_device *spi)

{

mcp251x_write_reg(spi, CANCTRL, CANCTRL_REQOP_SLEEP);

}

static netdev_tx_t mcp251x_hard_start_xmit(struct sk_buff *skb,

struct net_device *net)

{

struct mcp251x_priv *priv = netdev_priv(net);

struct spi_device *spi = priv->spi;

if (priv->tx_skb || priv->tx_len) {

dev_warn(&spi->dev, "hard_xmit called while tx busy\n");

return NETDEV_TX_BUSY;

}

if (can_dropped_invalid_skb(net, skb))

return NETDEV_TX_OK;

netif_stop_queue(net);

priv->tx_skb = skb;

queue_work(priv->wq, &priv->tx_work);

return NETDEV_TX_OK;

}

static int mcp251x_do_set_mode(struct net_device *net, enum can_mode mode)

{

struct mcp251x_priv *priv = netdev_priv(net);

switch (mode) {

case CAN_MODE_START:

mcp251x_clean(net);

/* We have to delay work since SPI I/O may sleep */

priv->can.state = CAN_STATE_ERROR_ACTIVE;

priv->restart_tx = 1;

if (priv->can.restart_ms == 0)

priv->after_suspend = AFTER_SUSPEND_RESTART;

queue_work(priv->wq, &priv->restart_work);

break;

default:

return -EOPNOTSUPP;

}

return 0;

}

static int mcp251x_set_normal_mode(struct spi_device *spi)

{

struct mcp251x_priv *priv = spi_get_drvdata(spi);

unsigned long timeout;

/* Enable interrupts */

mcp251x_write_reg(spi, CANINTE,

CANINTE_ERRIE | CANINTE_TX2IE | CANINTE_TX1IE |

CANINTE_TX0IE | CANINTE_RX1IE | CANINTE_RX0IE);

if (priv->can.ctrlmode & CAN_CTRLMODE_LOOPBACK) {

/* Put device into loopback mode */

mcp251x_write_reg(spi, CANCTRL, CANCTRL_REQOP_LOOPBACK);

} else if (priv->can.ctrlmode & CAN_CTRLMODE_LISTENONLY) {

/* Put device into listen-only mode */

mcp251x_write_reg(spi, CANCTRL, CANCTRL_REQOP_LISTEN_ONLY);

} else {

dev_err(&spi->dev, "mcp251x_set_normal_mode else \n");

/* Put device into normal mode */

mcp251x_write_reg(spi, CANCTRL, CANCTRL_REQOP_NORMAL);

/* Wait for the device to enter normal mode */

timeout = jiffies + HZ;

while (mcp251x_read_reg(spi, CANSTAT) & CANCTRL_REQOP_MASK) {

schedule();

if (time_after(jiffies, timeout)) {

dev_err(&spi->dev, "MCP251x didn't"

" enter in normal mode\n");

return -EBUSY;

}

}

}

priv->can.state = CAN_STATE_ERROR_ACTIVE;

return 0;

}

static int mcp251x_do_set_bittiming(struct net_device *net)

{

struct mcp251x_priv *priv = netdev_priv(net);

struct can_bittiming *bt = &priv->can.bittiming;

struct spi_device *spi = priv->spi;

dev_err(&spi->dev, "before CNF: 0x%02x 0x%02x 0x%02x\n",

mcp251x_read_reg(spi, CNF1),

mcp251x_read_reg(spi, CNF2),

mcp251x_read_reg(spi, CNF3));

mcp251x_write_reg(spi, CNF1, ((bt->sjw - 1) << CNF1_SJW_SHIFT) |

(bt->brp - 1));

mcp251x_write_reg(spi, CNF2, CNF2_BTLMODE |

(priv->can.ctrlmode & CAN_CTRLMODE_3_SAMPLES ?

CNF2_SAM : 0) |

((bt->phase_seg1 - 1) << CNF2_PS1_SHIFT) |

(bt->prop_seg - 1));

mcp251x_write_bits(spi, CNF3, CNF3_PHSEG2_MASK,

(bt->phase_seg2 - 1));

dev_err(&spi->dev, "CNF: 0x%02x 0x%02x 0x%02x\n",

mcp251x_read_reg(spi, CNF1),

mcp251x_read_reg(spi, CNF2),

mcp251x_read_reg(spi, CNF3));

return 0;

}

static int mcp251x_setup(struct net_device *net, struct mcp251x_priv *priv,

struct spi_device *spi)

{

mcp251x_do_set_bittiming(net);

mcp251x_write_reg(spi, RXBCTRL(0),

RXBCTRL_BUKT | RXBCTRL_RXM0 | RXBCTRL_RXM1);

mcp251x_write_reg(spi, RXBCTRL(1),

RXBCTRL_RXM0 | RXBCTRL_RXM1);

return 0;

}

static int mcp251x_hw_reset(struct spi_device *spi)

{

struct mcp251x_priv *priv = spi_get_drvdata(spi);

int ret;

unsigned long timeout;

priv->spi_tx_buf[0] = INSTRUCTION_RESET;

ret = spi_write(spi, priv->spi_tx_buf, 1);

if (ret) {

dev_err(&spi->dev, "reset failed: ret = %d\n", ret);

return -EIO;

}

/* Wait for reset to finish */

timeout = jiffies + HZ;

mdelay(10);

while ((mcp251x_read_reg(spi, CANSTAT) & CANCTRL_REQOP_MASK)

!= CANCTRL_REQOP_CONF) {

schedule();

if (time_after(jiffies, timeout)) {

dev_err(&spi->dev, "MCP251x didn't"

" enter in conf mode after reset\n");

return -EBUSY;

}

}

return 0;

}

static int mcp251x_hw_probe(struct spi_device *spi)

{

int st1, st2;

mcp251x_hw_reset(spi);

//stone added

printk(KERN_ERR "------mcp251x_hw_probe ------\n");

/*

* Please note that these are "magic values" based on after

* reset defaults taken from data sheet which allows us to see

* if we really have a chip on the bus (we avoid common all

* zeroes or all ones situations)

*/

st1 = mcp251x_read_reg(spi, CANSTAT) & 0xEE;

st2 = mcp251x_read_reg(spi, CANCTRL) & 0x17;

//stone

//dev_dbg(&spi->dev, "CANSTAT 0x%02x CANCTRL 0x%02x\n", st1, st2);

printk(KERN_ERR "CANSTAT 0x%02x CANCTRL 0x%02x\n", st1, st2);

/* Check for power up default values */

return (st1 == 0x80 && st2 == 0x07) ? 1 : 0;

}

static void mcp251x_open_clean(struct net_device *net)

{

struct mcp251x_priv *priv = netdev_priv(net);

struct spi_device *spi = priv->spi;

struct mcp251x_platform_data *pdata = spi->dev.platform_data;

free_irq(spi->irq, priv);

mcp251x_hw_sleep(spi);

if (pdata->transceiver_enable)

pdata->transceiver_enable(0);

close_candev(net);

}

static int mcp251x_stop(struct net_device *net)

{

struct mcp251x_priv *priv = netdev_priv(net);

struct spi_device *spi = priv->spi;

struct mcp251x_platform_data *pdata = spi->dev.platform_data;

close_candev(net);

priv->force_quit = 1;

free_irq(spi->irq, priv);

destroy_workqueue(priv->wq);

priv->wq = NULL;

mutex_lock(&priv->mcp_lock);

/* Disable and clear pending interrupts */

mcp251x_write_reg(spi, CANINTE, 0x00);

mcp251x_write_reg(spi, CANINTF, 0x00);

mcp251x_write_reg(spi, TXBCTRL(0), 0);

mcp251x_clean(net);

mcp251x_hw_sleep(spi);

if (pdata->transceiver_enable)

pdata->transceiver_enable(0);

priv->can.state = CAN_STATE_STOPPED;

mutex_unlock(&priv->mcp_lock);

can_led_event(net, CAN_LED_EVENT_STOP);

return 0;

}

static void mcp251x_error_skb(struct net_device *net, int can_id, int data1)

{

struct sk_buff *skb;

struct can_frame *frame;

skb = alloc_can_err_skb(net, &frame);

if (skb) {

frame->can_id |= can_id;

frame->data[1] = data1;

netif_rx_ni(skb);

} else {

netdev_err(net, "cannot allocate error skb\n");

}

}

static void mcp251x_tx_work_handler(struct work_struct *ws)

{

struct mcp251x_priv *priv = container_of(ws, struct mcp251x_priv,

tx_work);

struct spi_device *spi = priv->spi;

struct net_device *net = priv->net;

struct can_frame *frame;

//stone added log

dev_err(&spi->dev, "-----mcp251x_tx_work_handler-----");

mutex_lock(&priv->mcp_lock);

if (priv->tx_skb) {

if (priv->can.state == CAN_STATE_BUS_OFF) {

mcp251x_clean(net);

}

else

{

dev_err(&spi->dev, "-----mcp251x_tx_work_handler else-----");

frame = (struct can_frame *)priv->tx_skb->data;

if (frame->can_dlc > CAN_FRAME_MAX_DATA_LEN)

frame->can_dlc = CAN_FRAME_MAX_DATA_LEN;

mcp251x_hw_tx(spi, frame, 0);

priv->tx_len = 1 + frame->can_dlc;

can_put_echo_skb(priv->tx_skb, net, 0);

priv->tx_skb = NULL;

}

}

mutex_unlock(&priv->mcp_lock);

}

static void mcp251x_restart_work_handler(struct work_struct *ws)

{

struct mcp251x_priv *priv = container_of(ws, struct mcp251x_priv,

restart_work);

struct spi_device *spi = priv->spi;

struct net_device *net = priv->net;

mutex_lock(&priv->mcp_lock);

if (priv->after_suspend) {

mdelay(10);

mcp251x_hw_reset(spi);

mcp251x_setup(net, priv, spi);

if (priv->after_suspend & AFTER_SUSPEND_RESTART) {

mcp251x_set_normal_mode(spi);

} else if (priv->after_suspend & AFTER_SUSPEND_UP) {

netif_device_attach(net);

mcp251x_clean(net);

mcp251x_set_normal_mode(spi);

netif_wake_queue(net);

} else {

mcp251x_hw_sleep(spi);

}

priv->after_suspend = 0;

priv->force_quit = 0;

}

if (priv->restart_tx) {

priv->restart_tx = 0;

mcp251x_write_reg(spi, TXBCTRL(0), 0);

mcp251x_clean(net);

netif_wake_queue(net);

mcp251x_error_skb(net, CAN_ERR_RESTARTED, 0);

}

mutex_unlock(&priv->mcp_lock);

}

//stone modify isr to work

#if 0

static irqreturn_t mcp251x_can_isr(int irq, void *dev_id)

{

struct mcp251x_priv *priv = dev_id;

struct spi_device *spi = priv->spi;

struct net_device *net = priv->net;

dev_err(&spi->dev, "-----mcp251x_can_isr-----\n");

mutex_lock(&priv->mcp_lock);

while (!priv->force_quit) {

enum can_state new_state;

u8 intf, eflag;

u8 clear_intf = 0;

int can_id = 0, data1 = 0;

mcp251x_read_2regs(spi, CANINTF, &intf, &eflag);

/* mask out flags we don't care about */

intf &= CANINTF_RX | CANINTF_TX | CANINTF_ERR;

/* receive buffer 0 */

if (intf & CANINTF_RX0IF) {

mcp251x_hw_rx(spi, 0);

/*

* Free one buffer ASAP

* (The MCP2515 does this automatically.)

*/

if (mcp251x_is_2510(spi))

mcp251x_write_bits(spi, CANINTF, CANINTF_RX0IF, 0x00);

}

/* receive buffer 1 */

if (intf & CANINTF_RX1IF) {

mcp251x_hw_rx(spi, 1);

/* the MCP2515 does this automatically */

if (mcp251x_is_2510(spi))

clear_intf |= CANINTF_RX1IF;

}

/* any error or tx interrupt we need to clear? */

if (intf & (CANINTF_ERR | CANINTF_TX))

clear_intf |= intf & (CANINTF_ERR | CANINTF_TX);

if (clear_intf)

mcp251x_write_bits(spi, CANINTF, clear_intf, 0x00);

if (eflag)

mcp251x_write_bits(spi, EFLG, eflag, 0x00);

/* Update can state */

if (eflag & EFLG_TXBO) {

new_state = CAN_STATE_BUS_OFF;

can_id |= CAN_ERR_BUSOFF;

} else if (eflag & EFLG_TXEP) {

new_state = CAN_STATE_ERROR_PASSIVE;

can_id |= CAN_ERR_CRTL;

data1 |= CAN_ERR_CRTL_TX_PASSIVE;

} else if (eflag & EFLG_RXEP) {

new_state = CAN_STATE_ERROR_PASSIVE;

can_id |= CAN_ERR_CRTL;

data1 |= CAN_ERR_CRTL_RX_PASSIVE;

} else if (eflag & EFLG_TXWAR) {

new_state = CAN_STATE_ERROR_WARNING;

can_id |= CAN_ERR_CRTL;

data1 |= CAN_ERR_CRTL_TX_WARNING;

} else if (eflag & EFLG_RXWAR) {

new_state = CAN_STATE_ERROR_WARNING;

can_id |= CAN_ERR_CRTL;

data1 |= CAN_ERR_CRTL_RX_WARNING;

} else {

new_state = CAN_STATE_ERROR_ACTIVE;

}

/* Update can state statistics */

switch (priv->can.state) {

case CAN_STATE_ERROR_ACTIVE:

if (new_state >= CAN_STATE_ERROR_WARNING &&

new_state <= CAN_STATE_BUS_OFF)

priv->can.can_stats.error_warning++;

case CAN_STATE_ERROR_WARNING: /* fallthrough */

if (new_state >= CAN_STATE_ERROR_PASSIVE &&

new_state <= CAN_STATE_BUS_OFF)

priv->can.can_stats.error_passive++;

break;

default:

break;

}

priv->can.state = new_state;

if (intf & CANINTF_ERRIF) {

/* Handle overflow counters */

if (eflag & (EFLG_RX0OVR | EFLG_RX1OVR)) {

if (eflag & EFLG_RX0OVR) {

net->stats.rx_over_errors++;

net->stats.rx_errors++;

}

if (eflag & EFLG_RX1OVR) {

net->stats.rx_over_errors++;

net->stats.rx_errors++;

}

can_id |= CAN_ERR_CRTL;

data1 |= CAN_ERR_CRTL_RX_OVERFLOW;

}

mcp251x_error_skb(net, can_id, data1);

}

if (priv->can.state == CAN_STATE_BUS_OFF) {

if (priv->can.restart_ms == 0) {

priv->force_quit = 1;

can_bus_off(net);

mcp251x_hw_sleep(spi);

break;

}

}

if (intf == 0)

break;

if (intf & CANINTF_TX) {

net->stats.tx_packets++;

net->stats.tx_bytes += priv->tx_len - 1;

can_led_event(net, CAN_LED_EVENT_TX);

if (priv->tx_len) {

can_get_echo_skb(net, 0);

priv->tx_len = 0;

}

netif_wake_queue(net);

}

}

mutex_unlock(&priv->mcp_lock);

return IRQ_HANDLED;

}

#endif

static irqreturn_t mcp251x_can_isr(int irq, void *dev_id)

{

struct mcp251x_priv *priv = dev_id;

//stone added for debug

printk(KERN_ERR "----mcp251x_can_isr----\n");

disable_irq_nosync(irq);

if (!work_pending(&priv->irq_work))

queue_work(priv->wq, &priv->irq_work);

return IRQ_HANDLED;

}

void can_irq_work(struct work_struct *ws)

{

struct mcp251x_priv *priv = container_of(ws, struct mcp251x_priv,

irq_work);

struct spi_device *spi = priv->spi;

struct net_device *net = priv->net;

//stone added for debug

dev_err(&spi->dev, "Int lower half: can_irq_work\n");

mutex_lock(&priv->mcp_lock);

while (!priv->force_quit) {

enum can_state new_state;

u8 intf, eflag;

u8 clear_intf = 0;

int can_id = 0, data1 = 0;

mcp251x_read_2regs(spi, CANINTF, &intf, &eflag);

/* mask out flags we don't care about */

intf &= CANINTF_RX | CANINTF_TX | CANINTF_ERR ;//| CANINTF_MERRF;

//stone added for debug

printk(KERN_ERR "intf = %x\n", intf);

if (intf & CANINTF_TX) {

net->stats.tx_packets++;

net->stats.tx_bytes += priv->tx_len - 1;

if (priv->tx_len) {

can_get_echo_skb(net, 0);

priv->tx_len = 0;

}

netif_wake_queue(net);

}

/* receive buffer 1 */

if (intf & CANINTF_RX1IF) {

//stone added for debug

printk(KERN_ERR "receive buffer 1\n");

mcp251x_hw_rx(spi, 1);

/* the MCP2515 does this automatically */

if (mcp251x_is_2510(spi))

clear_intf |= CANINTF_RX1IF;

}

/* receive buffer 0 */

if (intf & CANINTF_RX0IF) {

//stone added for debug

printk(KERN_ERR "receive buffer 0\n");

mcp251x_hw_rx(spi, 0);

/*

* Free one buffer ASAP

* (The MCP2515 does this automatically.)

*/

if (mcp251x_is_2510(spi))

mcp251x_write_bits(spi, CANINTF, CANINTF_RX0IF, 0x00);

}

/* any error or tx interrupt we need to clear? */

if (intf & (CANINTF_ERR | CANINTF_TX))

clear_intf |= intf & (CANINTF_ERR | CANINTF_TX);

if (clear_intf)

mcp251x_write_bits(spi, CANINTF, clear_intf, 0x00);

if (eflag)

mcp251x_write_bits(spi, EFLG, eflag, 0x00);

/* Update can state */

if (eflag & EFLG_TXBO) {

new_state = CAN_STATE_BUS_OFF;

can_id |= CAN_ERR_BUSOFF;

} else if (eflag & EFLG_TXEP) {

new_state = CAN_STATE_ERROR_PASSIVE;

can_id |= CAN_ERR_CRTL;

data1 |= CAN_ERR_CRTL_TX_PASSIVE;

} else if (eflag & EFLG_RXEP) {

new_state = CAN_STATE_ERROR_PASSIVE;

can_id |= CAN_ERR_CRTL;

data1 |= CAN_ERR_CRTL_RX_PASSIVE;

} else if (eflag & EFLG_TXWAR) {

new_state = CAN_STATE_ERROR_WARNING;

can_id |= CAN_ERR_CRTL;

data1 |= CAN_ERR_CRTL_TX_WARNING;

} else if (eflag & EFLG_RXWAR) {

new_state = CAN_STATE_ERROR_WARNING;

can_id |= CAN_ERR_CRTL;

data1 |= CAN_ERR_CRTL_RX_WARNING;

} else {

new_state = CAN_STATE_ERROR_ACTIVE;

}

/* Update can state statistics */

switch (priv->can.state) {

case CAN_STATE_ERROR_ACTIVE:

if (new_state >= CAN_STATE_ERROR_WARNING &&

new_state <= CAN_STATE_BUS_OFF)

priv->can.can_stats.error_warning++;

case CAN_STATE_ERROR_WARNING: /* fallthrough */

if (new_state >= CAN_STATE_ERROR_PASSIVE &&

new_state <= CAN_STATE_BUS_OFF)

priv->can.can_stats.error_passive++;

break;

default:

break;

}

priv->can.state = new_state;

if (intf & CANINTF_ERRIF) {

/* Handle overflow counters */

if (eflag & (EFLG_RX0OVR | EFLG_RX1OVR)) {

if (eflag & EFLG_RX0OVR) {

net->stats.rx_over_errors++;

net->stats.rx_errors++;

}

if (eflag & EFLG_RX1OVR) {

net->stats.rx_over_errors++;

net->stats.rx_errors++;

}

can_id |= CAN_ERR_CRTL;

data1 |= CAN_ERR_CRTL_RX_OVERFLOW;

}

mcp251x_error_skb(net, can_id, data1);

}

if (priv->can.state == CAN_STATE_BUS_OFF) {

if (priv->can.restart_ms == 0) {

priv->force_quit = 1;

can_bus_off(net);

mcp251x_hw_sleep(spi);

break;

}

}

if (intf == 0)

break;

}

mutex_unlock(&priv->mcp_lock);

enable_irq(spi->irq);

}

static int mcp251x_open(struct net_device *net)

{

struct mcp251x_priv *priv = netdev_priv(net);

struct spi_device *spi = priv->spi;

struct mcp251x_platform_data *pdata = spi->dev.platform_data;

unsigned long flags;

int ret;

ret = open_candev(net);

if (ret) {

dev_err(&spi->dev, "unable to set initial baudrate!\n");

return ret;

}

//stone added log

dev_err(&spi->dev, "mcp251x_open-->open_candev");

mutex_lock(&priv->mcp_lock);

if (pdata->transceiver_enable)

pdata->transceiver_enable(1);

priv->force_quit = 0;

priv->tx_skb = NULL;

priv->tx_len = 0;

flags = IRQF_ONESHOT;

if (pdata->irq_flags)

flags |= pdata->irq_flags;

else

flags |= IRQF_TRIGGER_FALLING;

//中断处理接收

//stone added irq

spi->irq = gpio_to_irq(pdata->gpio_int1);

dev_err(&spi->dev, "Interrupt gpio=%d, irq=%d\n", pdata->gpio_int1, spi->irq);

if(spi->irq)

{

ret = request_threaded_irq(spi->irq, NULL, mcp251x_can_isr,

flags, DEVICE_NAME, priv);

if (ret) {

dev_err(&spi->dev, "failed to acquire irq %d\n", spi->irq);

if (pdata->transceiver_enable)

pdata->transceiver_enable(0);

close_candev(net);

goto open_unlock;

}

INIT_WORK(&priv->irq_work, can_irq_work);

}

priv->wq = create_freezable_workqueue("mcp251x_wq");

INIT_WORK(&priv->tx_work, mcp251x_tx_work_handler);

INIT_WORK(&priv->restart_work, mcp251x_restart_work_handler);

ret = mcp251x_hw_reset(spi);

//stone added log

dev_err(&spi->dev, "mcp251x_hw_reset");

if (ret) {

mcp251x_open_clean(net);

goto open_unlock;

}

ret = mcp251x_setup(net, priv, spi);

dev_err(&spi->dev, "mcp251x_setup");

if (ret) {

mcp251x_open_clean(net);

goto open_unlock;

}

ret = mcp251x_set_normal_mode(spi);

dev_err(&spi->dev, "mcp251x_set_normal_mode");

if (ret) {

mcp251x_open_clean(net);

goto open_unlock;

}

can_led_event(net, CAN_LED_EVENT_OPEN);

netif_wake_queue(net);

open_unlock:

mutex_unlock(&priv->mcp_lock);

return ret;

}

static const struct net_device_ops mcp251x_netdev_ops = {

.ndo_open = mcp251x_open,

.ndo_stop = mcp251x_stop,

.ndo_start_xmit = mcp251x_hard_start_xmit,

};

//stone added for int

#ifdef CONFIG_OF

static int mcp25625_parse_dt(struct device *dev,

struct mcp251x_platform_data *pdata)

{

#if 0

//u32 temp_val;

//int rc;

//rc = of_property_read_u32(np, "bosch,init-interval", &temp_val);

if (rc && (rc != -EINVAL)) {

dev_err(dev, "Unable to read init-interval\n");

return rc;

} else {

pdata->poll_interval = temp_val;

}

#endif

pdata->gpio_int1 = of_get_named_gpio_flags(dev->of_node,

"mcp25625,irq-gpio", 0, &pdata->int1_flag);

return 0;

}

#else

static int mcp25625_parse_dt(struct device *dev,

struct mcp251x_platform_data *pdata)

{

return -EINVAL;

}

#endif

static int mcp251x_can_probe(struct spi_device *spi)

{

struct net_device *net;

struct mcp251x_priv *priv;

//stone added

struct mcp251x_platform_data *pdata;

//struct mcp251x_platform_data *pdata = spi->dev.platform_data;

int ret = -ENODEV;

//这里platform_data都指到一起mcp251x_info

spi->dev.platform_data = &mcp251x_info;

pdata = spi->dev.platform_data;

if (spi->dev.of_node) {

ret = mcp25625_parse_dt(&spi->dev, pdata);

if (ret) {

dev_err(&spi->dev, "Failed to parse device tree\n");

ret = -EINVAL;

goto error_out;

}

}

//stone added for gpio int

{

if (!gpio_is_valid(pdata->gpio_int1)) {

dev_err(&spi->dev,

"gpio(%d) is invalid,\n", pdata->gpio_int1);

return -EINVAL;

}

ret = gpio_request(pdata->gpio_int1, "mscp25625_gpio_int");

if (ret) {

dev_err(&spi->dev,

"Unable to request gpio %d, err=%d\n",

pdata->gpio_int1, ret);

return ret;

}

ret = gpio_direction_input(pdata->gpio_int1);

if (ret) {

dev_err(&spi->dev,

"Unable to set gpio direction %d, err=%d\n",

pdata->gpio_int1, ret);

gpio_free(pdata->gpio_int1);

return ret;

}

}

//stone added

priv = kzalloc(sizeof(struct mcp251x_priv), GFP_KERNEL);

if (!priv) {

goto error_out;

}

mcp251x_enable_dma = 1;

spi_set_drvdata(spi, priv);

//data->client = client;

//data->dev = &client->dev;

printk(KERN_ERR "------mcp251x_can_probe------\n");

if (!pdata)

/* Platform data is required for osc freq */

goto error_out;

/* Allocate can/net device */

net = alloc_candev(sizeof(struct mcp251x_priv), TX_ECHO_SKB_MAX);

if (!net) {

ret = -ENOMEM;

goto error_alloc;

}

//stone added

printk(KERN_ERR "------mcp251x_can_probe1------\n");

net->netdev_ops = &mcp251x_netdev_ops;

net->flags |= IFF_ECHO;

priv = netdev_priv(net);

priv->can.bittiming_const = &mcp251x_bittiming_const;

priv->can.do_set_mode = mcp251x_do_set_mode;

priv->can.clock.freq = pdata->oscillator_frequency / 2;

priv->can.ctrlmode_supported = CAN_CTRLMODE_3_SAMPLES |

CAN_CTRLMODE_LOOPBACK | CAN_CTRLMODE_LISTENONLY;

priv->model = spi_get_device_id(spi)->driver_data;

priv->net = net;

spi_set_drvdata(spi, priv);

priv->spi = spi;

mutex_init(&priv->mcp_lock);

/* If requested, allocate DMA buffers */

if (mcp251x_enable_dma) {

spi->dev.coherent_dma_mask = ~0;

/*

* Minimum coherent DMA allocation is PAGE_SIZE, so allocate

* that much and share it between Tx and Rx DMA buffers.

*/

priv->spi_tx_buf = dma_alloc_coherent(&spi->dev,

PAGE_SIZE,

&priv->spi_tx_dma,

GFP_DMA);

if (priv->spi_tx_buf) {

priv->spi_rx_buf = (priv->spi_tx_buf + (PAGE_SIZE / 2));

priv->spi_rx_dma = (dma_addr_t)(priv->spi_tx_dma +

(PAGE_SIZE / 2));

} else {

/* Fall back to non-DMA */

mcp251x_enable_dma = 0;

}

}

/* Allocate non-DMA buffers */

if (!mcp251x_enable_dma) {

priv->spi_tx_buf = kmalloc(SPI_TRANSFER_BUF_LEN, GFP_KERNEL);

if (!priv->spi_tx_buf) {

ret = -ENOMEM;

goto error_tx_buf;

}

priv->spi_rx_buf = kmalloc(SPI_TRANSFER_BUF_LEN, GFP_KERNEL);

if (!priv->spi_rx_buf) {

ret = -ENOMEM;

goto error_rx_buf;

}

}

if (pdata->power_enable)

pdata->power_enable(1);

/* Call out to platform specific setup */

if (pdata->board_specific_setup)

pdata->board_specific_setup(spi);

SET_NETDEV_DEV(net, &spi->dev);

/* Configure the SPI bus */

spi->mode = SPI_MODE_0;

spi->bits_per_word = 8;

spi_setup(spi);

/* Here is OK to not lock the MCP, no one knows about it yet */

if (!mcp251x_hw_probe(spi)) {

dev_info(&spi->dev, "Probe failed\n");

goto error_probe;

}

mcp251x_hw_sleep(spi);

if (pdata->transceiver_enable)

pdata->transceiver_enable(0);

ret = register_candev(net);

if (ret)

goto error_probe;

devm_can_led_init(net);

dev_info(&spi->dev, "probed\n");

//stone added

printk(KERN_ERR "------mcp251x_can_probe OK------\n");

return ret;

error_probe:

if (!mcp251x_enable_dma)

kfree(priv->spi_rx_buf);

error_rx_buf:

if (!mcp251x_enable_dma)

kfree(priv->spi_tx_buf);

error_tx_buf:

free_candev(net);

if (mcp251x_enable_dma)

dma_free_coherent(&spi->dev, PAGE_SIZE,

priv->spi_tx_buf, priv->spi_tx_dma);

error_alloc:

if (pdata->power_enable)

pdata->power_enable(0);

dev_err(&spi->dev, "probe failed\n");

//stone added

printk(KERN_ERR "------mcp251x_can_probe err------\n");

error_out:

return ret;

}

static int mcp251x_can_remove(struct spi_device *spi)

{

struct mcp251x_platform_data *pdata = spi->dev.platform_data;

struct mcp251x_priv *priv = spi_get_drvdata(spi);

struct net_device *net = priv->net;

unregister_candev(net);

free_candev(net);

if (mcp251x_enable_dma) {

dma_free_coherent(&spi->dev, PAGE_SIZE,

priv->spi_tx_buf, priv->spi_tx_dma);

} else {

kfree(priv->spi_tx_buf);

kfree(priv->spi_rx_buf);

}

if (pdata->power_enable)

pdata->power_enable(0);

return 0;

}

#ifdef CONFIG_PM_SLEEP

static int mcp251x_can_suspend(struct device *dev)

{

struct spi_device *spi = to_spi_device(dev);

struct mcp251x_platform_data *pdata = spi->dev.platform_data;

struct mcp251x_priv *priv = spi_get_drvdata(spi);

struct net_device *net = priv->net;

priv->force_quit = 1;

disable_irq(spi->irq);

/*

* Note: at this point neither IST nor workqueues are running.

* open/stop cannot be called anyway so locking is not needed

*/

if (netif_running(net)) {

netif_device_detach(net);

mcp251x_hw_sleep(spi);

if (pdata->transceiver_enable)

pdata->transceiver_enable(0);

priv->after_suspend = AFTER_SUSPEND_UP;

} else {

priv->after_suspend = AFTER_SUSPEND_DOWN;

}

if (pdata->power_enable) {

pdata->power_enable(0);

priv->after_suspend |= AFTER_SUSPEND_POWER;

}

return 0;

}

static int mcp251x_can_resume(struct device *dev)

{

struct spi_device *spi = to_spi_device(dev);

struct mcp251x_platform_data *pdata = spi->dev.platform_data;

struct mcp251x_priv *priv = spi_get_drvdata(spi);

if (priv->after_suspend & AFTER_SUSPEND_POWER) {

pdata->power_enable(1);

queue_work(priv->wq, &priv->restart_work);

} else {

if (priv->after_suspend & AFTER_SUSPEND_UP) {

if (pdata->transceiver_enable)

pdata->transceiver_enable(1);

queue_work(priv->wq, &priv->restart_work);

} else {

priv->after_suspend = 0;

}

}

priv->force_quit = 0;

enable_irq(spi->irq);

return 0;

}

#endif

static SIMPLE_DEV_PM_OPS(mcp251x_can_pm_ops, mcp251x_can_suspend,

mcp251x_can_resume);

//stone added mcp25625

static const struct spi_device_id mcp251x_id_table[] = {

//{ "mcp2510", CAN_MCP251X_MCP2510 },

//{ "mcp2515", CAN_MCP251X_MCP2515 },

//{ },

{"mcp25625", 0},

};

MODULE_DEVICE_TABLE(spi, mcp251x_id_table);

//stone added mcp251x_of_match

static const struct of_device_id mcp251x_of_match[] = {

{ .compatible = "mcp25625", },

{ },

};

static struct spi_driver mcp251x_can_driver = {

.driver = {

.owner = THIS_MODULE,

.name = DEVICE_NAME,

.pm = &mcp251x_can_pm_ops,

//stone added

.of_match_table = mcp251x_of_match,

},

.id_table = mcp251x_id_table,

.probe = mcp251x_can_probe,

.remove = mcp251x_can_remove,

};

//stone added

#if 1

static int __init mcp251x_init(void)

{

return spi_register_driver(&mcp251x_can_driver);

}

static void __exit mcp251x_exit(void)

{

spi_unregister_driver(&mcp251x_can_driver);

}

module_init(mcp251x_init);

module_exit(mcp251x_exit);

#else

module_spi_driver(mcp251x_can_driver);

#endif

MODULE_AUTHOR("Chris Elston <[email protected]>");

MODULE_DESCRIPTION("Microchip 251x CAN driver");

MODULE_LICENSE("GPL v2");

由于没有找到CAN分析仪来验证,找了一块stm32的开发板,自己写了个简单的测试程序,main程序参考如下:

/****************************************Copyright (c)****************************************************

**

** http://www.powermcu.com

**

**--------------File Info---------------------------------------------------------------------------------

** File name: main.c

** Descriptions: The CAN-BUS application function

**

**--------------------------------------------------------------------------------------------------------

** Created by: AVRman

** Created date: 2010-10-30

** Version: v1.0

** Descriptions: The original version

**

**--------------------------------------------------------------------------------------------------------

** Modified by:

** Modified date:

** Version:

** Descriptions:

**

*********************************************************************************************************/

/* Includes ------------------------------------------------------------------*/

#include "stm32f10x.h"

#include "systick.h"

#include <stdlib.h>

#include <stdio.h>

#ifdef __GNUC__

/* With GCC/RAISONANCE, small printf (option LD Linker->Libraries->Small printf

set to 'Yes') calls __io_putchar() */

#define PUTCHAR_PROTOTYPE int __io_putchar(int ch)

#else

#define PUTCHAR_PROTOTYPE int fputc(int ch, FILE *f)

#endif /* __GNUC__ */

/* Private variables ---------------------------------------------------------*/

uint16_t CAN_ID;

uint8_t CAN_DATA0,CAN_DATA1,CAN_DATA2,CAN_DATA3,CAN_DATA4,CAN_DATA5,CAN_DATA6,CAN_DATA7;

uint8_t CanFlag,Display;

/* Private function prototypes -----------------------------------------------*/

void GPIO_Configuration(void);

void USART_Configuration(void);

void NVIC_Configuration(void);

void CAN_Configuration(void);

void CanWriteData(uint16_t ID);

/*******************************************************************************

* Function Name : main

* Description : Main program

* Input : None

* Output : None

* Return : None

* Attention : None

*******************************************************************************/

int main(void)

{

delay_init();

CAN_Configuration();

USART_Configuration();

printf("\r\n");

printf("*****************************************************************\r\n");

printf("* *\r\n");

printf("* Thank you for using HY-RedBull V3.0 Development Board !^_^ *\r\n");

printf("* *\r\n");

printf("*****************************************************************\r\n");

printf("CAN-Bus Test \r\n");

printf("CAN-Bus Speed 500kHz \r\n");

GPIO_SetBits(GPIOA , GPIO_Pin_7); //LED1 off

GPIO_SetBits(GPIOA , GPIO_Pin_6); //LED2 off

GPIO_SetBits(GPIOA , GPIO_Pin_5); //LED3 off

GPIO_SetBits(GPIOA , GPIO_Pin_4); //LED4 off

/* Infinite loop */

while (1)

{

if( CanFlag == ENABLE )

{

CanFlag = DISABLE;

printf("CAN Received Data \r\n");

printf("CAN ID %x \r\n",CAN_ID);

printf("CAN_DATA0 %x \r\n",CAN_DATA0);

printf("CAN_DATA1 %x \r\n",CAN_DATA1);

printf("CAN_DATA2 %x \r\n",CAN_DATA2);

printf("CAN_DATA3 %x \r\n",CAN_DATA3);

printf("CAN_DATA4 %x \r\n",CAN_DATA4);

printf("CAN_DATA5 %x \r\n",CAN_DATA5);

printf("CAN_DATA6 %x \r\n",CAN_DATA6);

printf("CAN_DATA7 %x \r\n",CAN_DATA7);

}

CanWriteData(0x88);

if( Display )

{

/*====LED-ON=======*/

GPIO_ResetBits(GPIOA , GPIO_Pin_7);

//GPIO_ResetBits(GPIOA , GPIO_Pin_6);

//GPIO_ResetBits(GPIOA , GPIO_Pin_5);

//GPIO_ResetBits(GPIOA , GPIO_Pin_4);

}

else

{

/*====LED-OFF=======*/

GPIO_SetBits(GPIOA , GPIO_Pin_7);

//GPIO_SetBits(GPIOA , GPIO_Pin_6);

//GPIO_SetBits(GPIOA , GPIO_Pin_5);

//GPIO_SetBits(GPIOA , GPIO_Pin_4);

}

Display = ~Display;

delay_ms(500); /* delay 200ms */

}

}

/*******************************************************************************

* Function Name : GPIO_Configuration

* Description : Configures the different GPIO ports.

* Input : None

* Output : None

* Return : None

* Attention : None

*******************************************************************************/

void GPIO_Configuration(void)

{

GPIO_InitTypeDef GPIO_InitStructure;

/* CAN Periph clock enable */

//stone comment :RCC_APB2Periph_GPIOA must add for config GPIOA

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOB | RCC_APB2Periph_GPIOD | RCC_APB2Periph_GPIOA | RCC_APB2Periph_AFIO ,ENABLE);

RCC_APB1PeriphClockCmd(RCC_APB1Periph_CAN1, ENABLE);

//Begin:stone added

/* Enable GPIO clock */

//RCC_APB2PeriphClockCmd(CAN_TX_GPIO_CLK|CAN_RX_GPIO_CLK, ENABLE);

//End:stone added

GPIO_PinRemapConfig(GPIO_Remap1_CAN1,ENABLE);

/* Configure CAN pin: RX PB8 */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_8;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN_FLOATING;

GPIO_Init(GPIOB, &GPIO_InitStructure);

/* Configure CAN pin: TX PB9*/

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_9;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;

GPIO_Init(GPIOB, &GPIO_InitStructure);

/**

* LED1 -> PA7 , LED2 -> PA6 , LED3 -> PA5 , LED4 -> PA4

*/

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_7 | GPIO_Pin_6 | GPIO_Pin_5 | GPIO_Pin_4;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_PP;

GPIO_Init(GPIOA, &GPIO_InitStructure);

}

/*******************************************************************************

* Function Name : NVIC_Configuration

* Description : Configures the nested vectored interrupt controller.

* Input : None

* Output : None

* Return : None

* Attention : None

*******************************************************************************/

void NVIC_Configuration(void)

{

NVIC_InitTypeDef NVIC_InitStructure;

/* Enable CAN1 RX0 interrupt IRQ channel */

NVIC_InitStructure.NVIC_IRQChannel = USB_LP_CAN1_RX0_IRQn;

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0;

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0;

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;

NVIC_Init(&NVIC_InitStructure);

}

/*******************************************************************************

* Function Name : USART_Configuration

* Description : Configure USART1

* Input : None

* Output : None

* Return : None

* Attention : None

*******************************************************************************/

void USART_Configuration(void)

{

GPIO_InitTypeDef GPIO_InitStructure;

USART_InitTypeDef USART_InitStructure;

RCC_APB2PeriphClockCmd( RCC_APB2Periph_GPIOA | RCC_APB2Periph_USART1,ENABLE);

/*

* USART1_TX -> PA9 , USART1_RX -> PA10

*/

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_9;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_Init(GPIOA, &GPIO_InitStructure);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_10;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN_FLOATING;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_Init(GPIOA, &GPIO_InitStructure);

USART_InitStructure.USART_BaudRate = 115200;

USART_InitStructure.USART_WordLength = USART_WordLength_8b;

USART_InitStructure.USART_StopBits = USART_StopBits_1;

USART_InitStructure.USART_Parity = USART_Parity_No;

USART_InitStructure.USART_HardwareFlowControl = USART_HardwareFlowControl_None;

USART_InitStructure.USART_Mode = USART_Mode_Rx | USART_Mode_Tx;

USART_Init(USART1, &USART_InitStructure);

USART_ITConfig(USART1, USART_IT_RXNE, ENABLE);

USART_ITConfig(USART1, USART_IT_TXE, ENABLE);

USART_Cmd(USART1, ENABLE);

}

/*******************************************************************************

* Function Name : CAN_Configuration

* Description : Configures the CAN

* Input : None

* Output : None

* Return : None

* Attention : None

*******************************************************************************/

void CAN_Configuration(void)

{

CAN_InitTypeDef CAN_InitStructure;

CAN_FilterInitTypeDef CAN_FilterInitStructure;

NVIC_Configuration();

GPIO_Configuration();

/* CAN register init */

CAN_DeInit(CAN1);

CAN_StructInit(&CAN_InitStructure);

/* CAN cell init */

CAN_InitStructure.CAN_TTCM = DISABLE; /* 时间触发禁止, 时间触发:CAN硬件的内部定时器被激活,并且被用于产生时间戳 */

CAN_InitStructure.CAN_ABOM = DISABLE; /* 自动离线禁止,自动离线:一旦硬件监控到128次11个隐性位,就自动退出离线状态。在这里要软件设定后才能退出 */

CAN_InitStructure.CAN_AWUM = ENABLE; /* 自动唤醒禁止,有报文来的时候自动退出休眠 */

CAN_InitStructure.CAN_NART = DISABLE; /* 报文重传, 如果错误一直传到成功止,否则只传一次 */

CAN_InitStructure.CAN_RFLM = DISABLE; /* 接收FIFO锁定, 1--锁定后接收到新的报文摘不要,0--接收到新的报文则覆盖前一报文 */

CAN_InitStructure.CAN_TXFP = ENABLE; /* 发送优先级 0---由标识符决定 1---由发送请求顺序决定 */

CAN_InitStructure.CAN_Mode = CAN_Mode_Normal; /* 模式 */

CAN_InitStructure.CAN_SJW = CAN_SJW_2tq; /* 重新同步跳宽,只有can硬件处于初始化模式时才能访问这个寄存器 */

CAN_InitStructure.CAN_BS1 = CAN_BS1_5tq; /* 时间段1 */

CAN_InitStructure.CAN_BS2 = CAN_BS2_3tq; /* 时间段2 */

//CAN_InitStructure.CAN_Prescaler = 45; /* 波特率预分频数 */

CAN_InitStructure.CAN_Prescaler = 12; /* 波特率预分频数 stone modify to 500K*/

/*注意:12M的晶振配置为5 3 12才能得到500Kbps 比较奇怪*/

/* 波特率计算方法 CAN 时钟频率为 APB1 = 36 MHz */

/* CANbps= Fpclk/((BRP+1)*((Tseg1+1)+(Tseg2+1)+1) 此处计算为 CANbps=36000000/(45*(4+3+1))=100kHz */ //此处Tseg1+1 = CAN_BS1_8tp

/* 配置大方向: Tseg1>=Tseg2 Tseg2>=tq; Tseg2>=2TSJW */

if (CAN_Init(CAN1,&CAN_InitStructure) == CANINITFAILED)

{

/* 初始化时先设置CAN_MCR的初始化位 */

/* 然后查看硬件是否真的设置了CAN_MSR的初始化位来确认是否进入了初始化模式 */

}

/* 配置CAN过滤器 */

/* 32位对应的id */

/* stdid[10:0],extid[17:0],ide,rtr */

/* 16位对应的id */

/* stdid[10:0],ide,rtr,extid[17:15] */

/* 一般使用屏蔽模式 */

/* 要注意的是fifo接收存满了中断,还有就是fifo的概念,即取的一直是最早那一个数据, 要释放才能取下一个数据 */

/* 常使用的中断有 */

/* 1,有信息中断,即fifo挂号中断 */

/* 2,fifo满中断 */

/* 3,fifo满之后又有信息来则中断,即fifo溢出中断 */

CAN_FilterInitStructure.CAN_FilterNumber=0; /* 过滤器0 */

CAN_FilterInitStructure.CAN_FilterMode=CAN_FilterMode_IdMask; /* 屏敝模式 */

CAN_FilterInitStructure.CAN_FilterScale=CAN_FilterScale_32bit; /* 32位 */

CAN_FilterInitStructure.CAN_FilterIdHigh=0x0000; /* 以下四个都为0, 表明不过滤任何id */

CAN_FilterInitStructure.CAN_FilterIdLow=0x0000;

CAN_FilterInitStructure.CAN_FilterMaskIdHigh=0x0000;

CAN_FilterInitStructure.CAN_FilterMaskIdLow=0x0000;

CAN_FilterInitStructure.CAN_FilterFIFOAssignment=0; /* 能够通过该过滤器的报文存到fifo0中 */

CAN_FilterInitStructure.CAN_FilterActivation=ENABLE;

CAN_ITConfig(CAN1,CAN_IT_FMP0, ENABLE); /* 挂号中断, 进入中断后读fifo的报文函数释放报文清中断标志 */

CAN_FilterInit(&CAN_FilterInitStructure);

}

/*******************************************************************************

* Function Name : CanWriteData

* Description : Can Write Date to CAN-BUS

* Input : None

* Output : None

* Return : None

* Attention : None

*******************************************************************************/

void CanWriteData(uint16_t ID)

{

CanTxMsg TxMessage;

CAN_DATA0=rand()%0xff; CAN_DATA1=rand()%0xff;

CAN_DATA2=rand()%0xff; CAN_DATA3=rand()%0xff;

CAN_DATA4=rand()%0xff; CAN_DATA5=rand()%0xff;

CAN_DATA6=rand()%0xff; CAN_DATA7=rand()%0xff;

/* transmit */

TxMessage.StdId = ID; /* 设置标准id 注意标准id的最高7位不能全是隐性(1)。共11位 */

//TxMessage.ExtId = 0x00; //设置扩展id 扩展id共18位

TxMessage.RTR = CAN_RTR_DATA; /* 设置为数据帧 */

TxMessage.IDE = CAN_ID_STD; /* 使用标准id */

TxMessage.DLC = 8; /* 数据长度, can报文规定最大的数据长度为8字节 */

TxMessage.Data[0] = CAN_DATA0;

TxMessage.Data[1] = CAN_DATA1;

TxMessage.Data[2] = CAN_DATA2;

TxMessage.Data[3] = CAN_DATA3;

TxMessage.Data[4] = CAN_DATA4;

TxMessage.Data[5] = CAN_DATA5;

TxMessage.Data[6] = CAN_DATA6;

TxMessage.Data[7] = CAN_DATA7;

CAN_Transmit(CAN1,&TxMessage); /* 返回这个信息请求发送的邮箱号0,1,2或没有邮箱申请发送no_box */

}

/*******************************************************************************

* Function Name : USB_LP_CAN1_RX0_IRQHandler

* Description : This function handles USB Low Priority or CAN RX0 interrupts

* Input : None

* Output : None

* Return : None

* Attention : None

*******************************************************************************/

void USB_LP_CAN1_RX0_IRQHandler(void)

{

CanRxMsg RxMessage;

CAN_Receive(CAN1,CAN_FIFO0, &RxMessage); /* 此函数包含释放提出报文了的,在非必要时,不需要自己释放 */

CAN_ID=RxMessage.StdId;

CAN_DATA0=RxMessage.Data[0];

CAN_DATA1=RxMessage.Data[1];

CAN_DATA2=RxMessage.Data[2];

CAN_DATA3=RxMessage.Data[3];

CAN_DATA4=RxMessage.Data[4];

CAN_DATA5=RxMessage.Data[5];

CAN_DATA6=RxMessage.Data[6];

CAN_DATA7=RxMessage.Data[7];

CAN_ClearITPendingBit(CAN1,CAN_IT_FMP0); /* 清除挂起中断 */

CanFlag = ENABLE;

}

/**

* @brief Retargets the C library printf function to the USART.

* @param None

* @retval None

*/

PUTCHAR_PROTOTYPE

{

/* Place your implementation of fputc here */

/* e.g. write a character to the USART */

USART_SendData(USART1, (uint8_t) ch);

/* Loop until the end of transmission */

while (USART_GetFlagStatus(USART1, USART_FLAG_TC) == RESET)

{}

return ch;

}

#ifdef USE_FULL_ASSERT

/**

* @brief Reports the name of the source file and the source line number

* where the assert_param error has occurred.

* @param file: pointer to the source file name

* @param line: assert_param error line source number

* @retval None

*/

void assert_failed(uint8_t* file, uint32_t line)

{

/* User can add his own implementation to report the file name and line number,

ex: printf("Wrong parameters value: file %s on line %d\r\n", file, line) */

/* Infinite loop */

while (1)

{

}

}

#endif

/*********************************************************************************************************

END FILE

*********************************************************************************************************/

在Android侧还需要找个apk去设置CAN参数来通讯,懒得去写apk了。参考网上的例子简单写了个可执行程序运行验证是否正确:

/*

* can_test_send_and_dump.c

*

* Created on: 2018-8-25

* Author: tanghanyue

*/

#include <stdio.h>

#include <stdlib.h>

#include <string.h>

#include <unistd.h>

#include <net/if.h>

#include <sys/ioctl.h>

#include <sys/socket.h>

#include <linux/can.h>

#include <linux/can/raw.h>

int main(int argc, char *argv[])

{

int s, nbytes;

unsigned char number=0;

struct sockaddr_can addr;

struct ifreq ifr;

struct can_frame frame;

struct can_frame frame_send;

struct can_filter rfilter[1];

pid_t pid = -1;

int i;

/* handle (optional) flags first */

if(argc != 2) {

fprintf(stderr, "Usage: %s <-r> <can interface name> for receiving\nor <-s> <can interface name> for sending\n", argv[0]);

exit(1);

}

/* create socket */

if ((s = socket(PF_CAN, SOCK_RAW, CAN_RAW)) < 0)

{

perror("Create socket failed");

exit(-1);

}

/* set up can interface */

strcpy(ifr.ifr_name, argv[1]);

printf("can port is %s\n",ifr.ifr_name);

/* assign can device */

ioctl(s, SIOCGIFINDEX, &ifr);

addr.can_family = AF_CAN;

addr.can_ifindex = ifr.ifr_ifindex;

/* bind can device */

if(bind(s, (struct sockaddr *)&addr, sizeof(addr)) < 0)

{

perror("Bind can device failed\n");

close(s);

exit(-2);

}

pid = fork();

if(pid == -1)

{

perror("\n\tfailed to fork!!\n\n");

return -1;

}

else if(pid==0)/* configure receiving can data*/

{

/* set filter for only receiving packet with can id 0x88 */

rfilter[0].can_id = 0x88;

rfilter[0].can_mask = CAN_SFF_MASK;

if(setsockopt(s, SOL_CAN_RAW, CAN_RAW_FILTER, &rfilter, sizeof(rfilter)) < 0)

{

perror("set receiving filter error\n");

close(s);

exit(-3);

}

/* keep reading */

while(1)

{

nbytes = read(s, &frame, sizeof(frame));

if(nbytes > 0)

{

printf("read datas:%s ID=%#x data length=%d\n", ifr.ifr_name, frame.can_id, frame.can_dlc);

for ( i=0; i < frame.can_dlc; i++)

printf("%#x ", frame.data[i]);

printf("\n");

}

printf("read can data over\n");

}

}/* configure sending can data*/

else

{

while(1)

{

/* configure can_id and can data length */

frame_send.can_id = 0x88;

frame_send.can_dlc = 8;

printf("%s ID=%#x data length=%d\n", ifr.ifr_name, frame_send.can_id, frame_send.can_dlc);

/* prepare data for sending: 0x11,0x22...0x88 */

for (i=0; i<8; i++)

{

frame_send.data[i] = ((i+1)<<4) | (i+1);

frame_send.data[7] =number;

printf("%#x ", frame_send.data[i]);

}

printf("success to Sent out\n");

/* Sending data */

if(write(s, &frame_send, sizeof(frame_send)) < 0)

{

perror("Send failed");

close(s);

exit(-4);

}

sleep(1);

number++;

}

}

close(s);

return 0;

}

把两块板子的CAN总线连接在一起,验证和stm32可以正常通讯,中断log如下:

[ 105.920481] ----mcp251x_can_isr----

[ 105.923041] mcp25625 spi4.0: Int lower half: can_irq_work

[ 105.928635] intf = 1

[ 105.930614] receive buffer 0

[ 105.933581] mcp25625 spi4.0: buf_idx=0

[ 105.937203] mcp25625 spi4.0: buf[0]=ff

[ 105.942904] mcp25625 spi4.0: buf[1]=11

[ 105.945622] mcp25625 spi4.0: buf[2]=0

[ 105.949728] mcp25625 spi4.0: buf[3]=ff

[ 105.953206] mcp25625 spi4.0: buf[4]=57

[ 105.960300] mcp25625 spi4.0: buf[5]=8

[ 105.962932] mcp25625 spi4.0: buf[6]=5d

[ 105.966664] mcp25625 spi4.0: buf[7]=e3

[ 105.971056] mcp25625 spi4.0: buf[8]=4c

[ 105.974610] mcp25625 spi4.0: buf[9]=cf

[ 105.978517] mcp25625 spi4.0: buf[10]=60

[ 105.981858] mcp25625 spi4.0: buf[11]=1

[ 105.986312] mcp25625 spi4.0: buf[12]=7a

[ 105.990031] mcp25625 spi4.0: buf[13]=16

[ 105.993205] intf = 0

至此调试完成。