基于Multisim10.0.1的多功能数字钟的设计

信息工程学院电子技术综合实训

注:本实验报告,仅供参考,其中资料文献本文后面有注明来处,侵权删。

文章目录

课题前言

电子综合实训包括很多实验,本实验课题选择多功能电子时钟的设计,其中包括模拟电子技术和数字电子技术的知识的运用,本文使用的实验环境是win7(当然win10可以的),仿真软件是Multisim10.0.1,打开界面如下:

提示:以下是本篇文章正文内容,下面案例供参考

一、设计目的和要求

设计一个多功能数字钟,能够准确记时并以数字化形式显示时、分、秒的时间,且该数字钟能够有以下功能:

| 序号 | 功能 |

|---|---|

| 1 | 校正时间 |

| 2 | 准点报时 |

| 3 | 定时闹钟 |

二、选题的目的和意义

数字钟从原理上来讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。目前,数字钟的功能越来越多,并且有多种专门的大规模集成电路可供选择,一般由数钟电路、放大执行电路、电源电路等组成。

设计多功能数字电路,通过简单的电路结构,并更改设定电路,了解通过输入脉冲,达到设计时钟目的,同时运用芯片以及逻辑门来实现进制从而理解数字电路的应用。

三、方案的可行性论证

1、方案的设计要求

1、时间以24小时为周期;

2、显示时、分、秒;

3、具有校时功能,可以分别对时、分、秒进行单独校时,使其校正达到标准时间;

4、具有整点报时功能,即设置时间到达整点前10秒进行蜂鸣器报时;

5、具有定时闹钟功能。

2、各电路模块初步分析

时间显示电路

时间显示模块包括时、分、秒部分,可用显示译码器来显示,从而实现24制以及60制。

时间校准电路

时间校准包括时钟校准、分钟校准和秒钟校准三个模块,可在各模块中设置点动开关,需要校准时,对应的显示模块数值随点动开关连续变换,待调到所需要的数值时,停止校准,从而达到对各个模块的单独校时。

整点报时电路

将显示译码器电路中加逻辑门与其相连,当整点时,报时可通过蜂鸣器蜂鸣实现,并可设置蜂鸣器的长鸣时间。

定时闹钟电路

可通过开关组来设置闹钟时间,芯片与逻辑门

3、工作原理及图例

当秒计时器计60后向分计数器进位,分计数器计数60后向小时进位,小时计数器设置成24进制计数器,满24后清零,重新开始计时。计数器的输出直接送到LED显示器,当计时出现误差时可以用校时电路进行校时、校分,校时电路是由一开关接到一个高电位上,当按一下开关就传送一个高位脉冲,计数器加一。

四、元件、器件明细表

1、74LS161N:

可预置四位二进制计数器(并清除异步)

1.QA~QD:计数输出端,输出二进制代码

2.A~D:预置数据输入端,输入二进制代码

3.CLK:相当于CP,接单次脉冲端输入

4.ENT,ENP:计数控制端

5.~CLR:直接清零端

6.~LOAD:预置数控制端

7.RCO:进位输出端

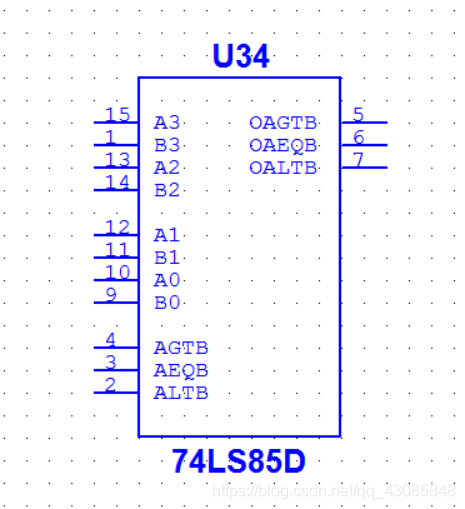

2、74LS85D:

四位数字比较器

通过功能表可知,该比较器的比较原理和两位比较器的比较原理相同。两个4位数的比较是从芯片1的最高位A3和芯片2的最高位B3进行比较,如果它们不相等,则该位的比较结果可以作为两数的比较结果。若最高位A3=B3,则再比较次高位A2和B2,余类推。显然,如果两数相等,那么,比较步骤必须进行到最低位才能得到结果,即可从而达到定时闹钟的效果。

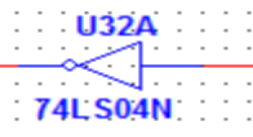

3、74LS04N:

74LS04是六个单输入端的反相器.它的输出信号与输入信号相位相反。六个反相器共用电源端和接地端,其它都是独立的。输出信号手动负载的能力也有一定程度的放大。

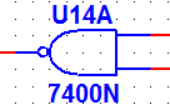

4、7400 输入与非门:

内含四个独立的2输入端与非门,其逻辑功能是:输入端全部为1时,输出为0;输入端只要有0,输出就为1.

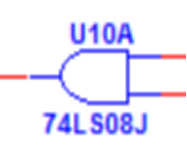

5、74LS08J 2输入四与门:

与门,详细地说是4二输入与门,即一片74LS08芯片内有共四路二个输入端的与门。

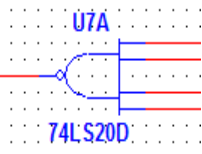

6、74LS20D 4输入双与非门:

两个4输入与非门,内含两组4与非门。

7、元件、器件明细表:

| 序号 | 名称 | 数量 |

|---|---|---|

| 1 | 显示译码器 | 6 |

| 2 | 蜂鸣器 | 2 |

| 3 | 74LS161N | 6 |

| 4 | 74LS85D | 4 |

| 5 | 7400N | 8 |

| 6 | 74LS08J | 3 |

| 7 | 74LS20D | 2 |

| 8 | 瞬时开关 | 3 |

| 9 | 开关组 | 4 |

| 10 | 数字电源VCC | 5 |

| 11 | 时钟脉冲源 | 1 |

| 12 | 单刀双置开关 | 1 |

| 13 | 电子探针 | 1 |

五、各个电路模块分析

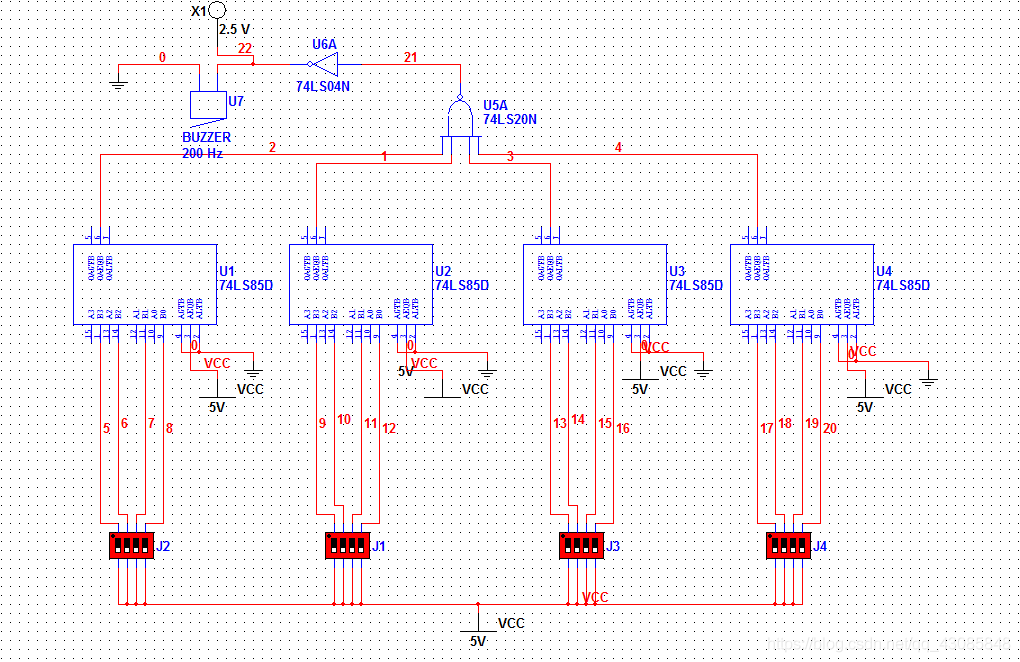

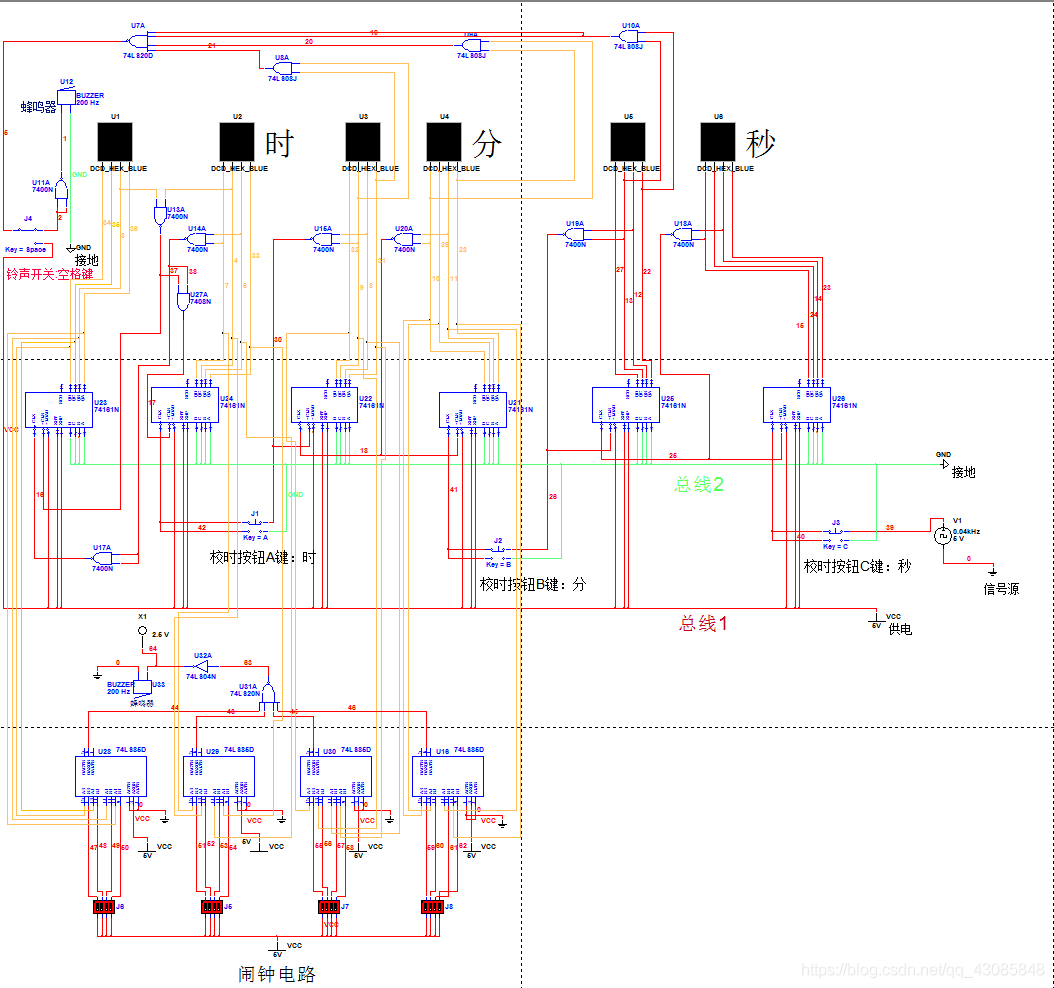

1、闹钟电路

闹钟电路蛮好做,如图,采用4片74LS85D芯片和4个拨码开关构成闹钟电路,从最低位(分个位)对应的比较器74LS85D(U21)的OAEQB端输出高电平,从而实现闹钟功能。

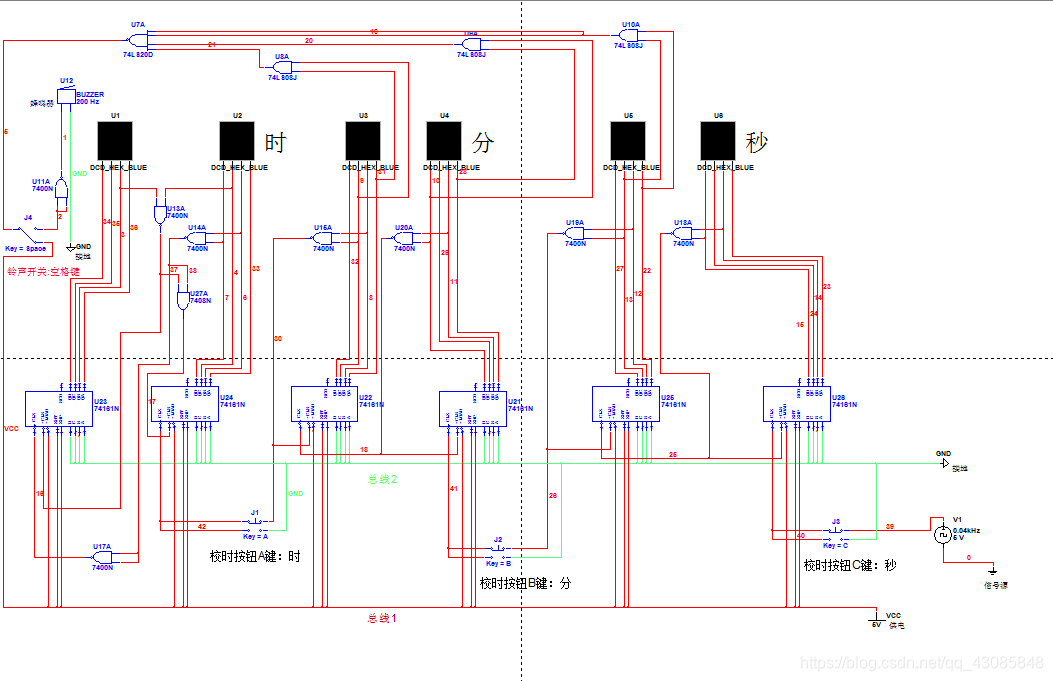

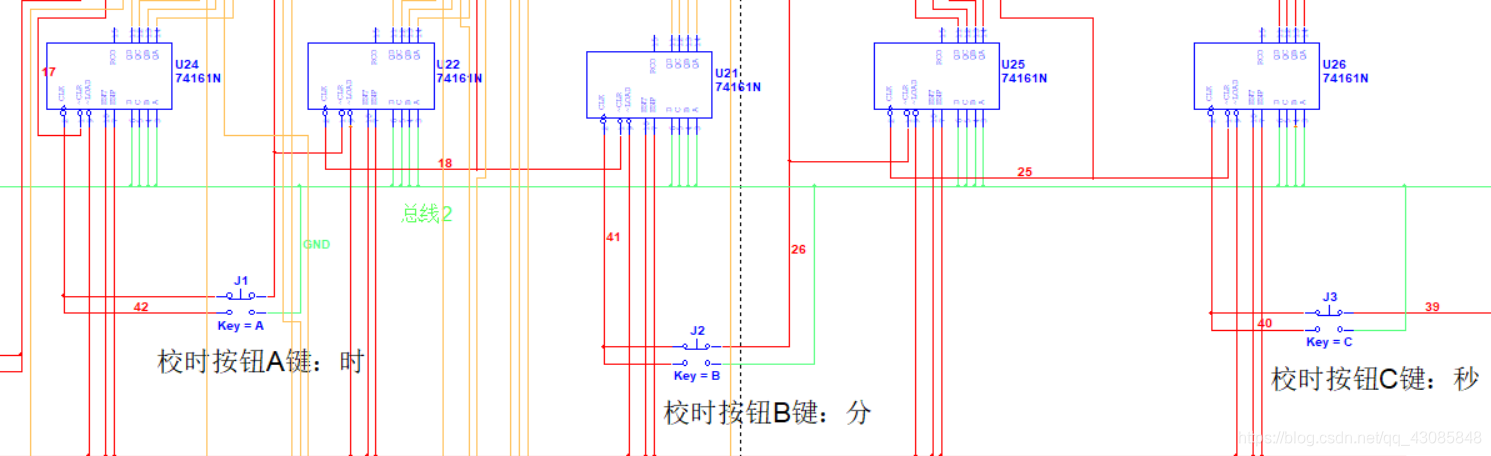

2、校时电路

在分、秒的与非门与上一级的脉冲接口之间接瞬间开关即可。当开关按下时,产生一个低电平给计数器,从而在下降沿的时候计数器加一。

注:瞬时开关是交互组件,在Multisim中可以通过键盘上的一个键或使用鼠标点击激活,

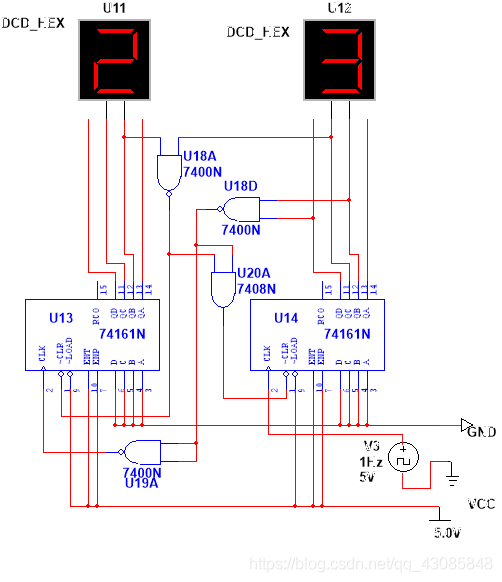

3、时记时电路

24进制的实现用的是两片74LS161芯片以及与非门实现24进制(00~23)。时计时器的十位是二进制,个位是十进制,同时和与非门相连,实现满24时清零,由于小时位和分为、秒为不同,它是以十进制来显示24进制数,即它有两个清零信号,一是在小时的个位计数到10的瞬间,向本位发送一个清零信号,并同时向十位数发送一个进位脉冲。二是在小时的十位计数到2并且个数计数到4的瞬间,向个位和十位同时发送一个清零信号。

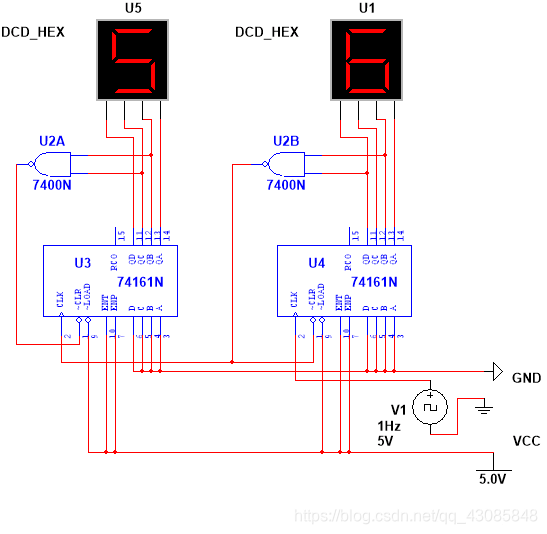

4、分、秒记时电路

60进制的实现是采用两片74LS161芯片和与非门实现的,分、秒计数器的十位都是60进制,个位都是10进制,共同构成60精致。分、秒计时电路的控制是一样的,采用同一器件74LS161N的反馈置数法来实现10进制功能和6进制功能,根据芯片74LS161N的结构把输出端的0100(十进制为6)用一个与非门7400N引到CLR端便可置0,即当分(秒)的个位计数到10的瞬间,向本位发送一个清零信号,并同时向其个位发送一个进位脉冲。分(秒)的十位加法计数器在计数到6的瞬间,向本位发送一个清零信号,并同时向分(秒)位的个位发送一个进位脉冲。这样就构成了一个级联而形成的60进制带进位与清零的加法计数器。

六、总电路图

- 不带闹钟总电路图:

- 带闹钟总电路图:

七、测试结果图

连接好电路图后,准备开始仿真,同时可测试闹钟功能。

结果如下:

文献

1、参考作者以及网址

https://blog.csdn.net/Jason_yesly

https://blog.csdn.net/Jason_yesly/article/details/85297274

https://wenku.baidu.com/view/64c63f1edd36a32d737581bc.html

https://wenku.baidu.com/view/bb573f76700abb68a982fbe5.html

2、书籍文献

《电路基础与电子技术》

《电类专业基础实践教程》

总结

以上,就是我对该实验的看法,通过实训,虽然最终电路设计有些缺陷和不足,但掌握了许多知识,学会了用Multisim仿真的基本操作,对改进电路和连接线路方面上有很充分的研究和认识,同时通过查阅大量书籍和网上资料,对元件的选用和代替以及不同元件的不同特性也作了比较到最终的选用,以及最终电路中某些开关以及小型元器件的参数调整进行了反复地测试,到达了基本本课题的基本要求,特别是对Multisim该软件的认识以及运用和该课题中所用到的模拟电子技术和数字电子技术的知识的运用。

本博客,是我在CSDN上第一次发的博客,毕竟自己忙活了几周的结果,自己学到了不少知识,通过书本资料和网站确实不易。若有不当错误,望评论区订正。