FPGA学习笔记

图像处理算法

1. RGB转灰度算法

1.1 背景

1.2 FPGA实现RGB图像转Gray图像

1. RGB转灰度算法

- 1.1 背景:

- Gray图像:灰度图像,黑白图像,由黑到白为灰阶:0~255(8bits).

- YUV图像:欧洲电视系统采用的颜色编码方法,主要用于优化彩色视频信号的传输。采用彩色摄影机或者彩色CCD摄影机取像,将彩色图像信号进行分色,分别放大校正,得到RGB,经过矩阵变换电路,得到亮度信号Y和两个色差信号B-Y(U), R-Y(V),经过发送端编码,用同一信道发送出去。

“Y”:表示明亮度(Luminance,Luma),灰阶值;通过RGB输入信号建立,将RGB信号的特定部分叠加在一起。

“U”“V”表示色度(Chrominance,Chroma),定义色彩以及饱和度,指定像素颜色。Cr:RGB输入信号红色部分与RGB信号亮度值之间的差异;Cb: RGB输入信号蓝色部分与RGB信号亮度值之间的差异。 - Ycbcr图像:Ycbcr,Y’CbCr, YCBCR, Y’CBCR, 色彩空间,用于影像连续处理,数字摄影系统。Y’:luma,亮度成分,CB, CR:蓝色,红色的浓度偏移量成分。Y:luminance,表示光的浓度且为非线性,使用伽马修正(gamma correction)编码处理。

- 1.2 FPGA实现RGB图像转Gray图像

方法(2种): 1. RGB图像的单通道显示图像(R,G,B). 2. RGB图像转换成Ycbcr图像,使用Y分量显示图像

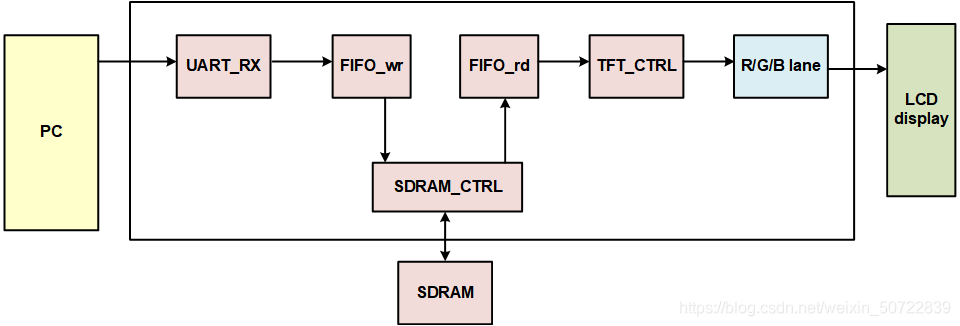

- RGB图像的单通道显示图像(R,G,B)

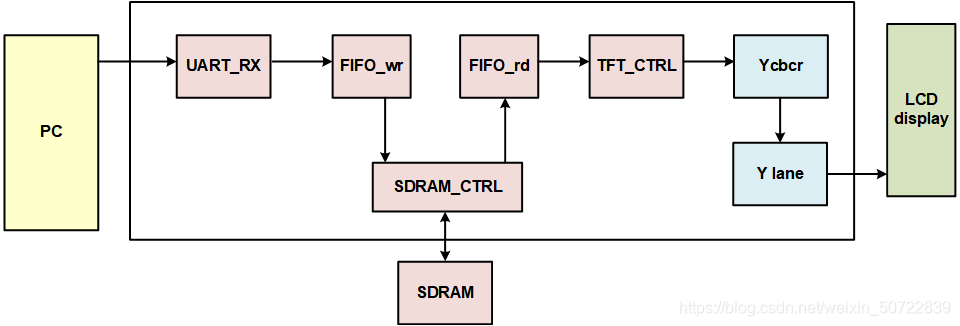

- RGB图像转换成Ycbcr图像,使用Y分量显示图像

RGB转Ycbcr算法:

公式:

Y = 0.183R + 0.614G + 0.062B + 16;

Cb = -0.101R - 0.338G + 0.439B + 128;

Cr = 0.439R – 0.399G -0.040B + 128;

计算未用到时序,输入到输出由三个clock的延时。

第一级流水线:计算所有乘法;

第二级流水线:计算所有加法,把正的和负的分开进行加法;

第三级流水线:计算最终的和,若为负数,取0;

- Verilog代码

/*

RGB-->Ycbcr:

Y = 0.183R + 0.614G + 0.062B + 16;

Cb = -0.101R - 0.338G + 0.439B + 128;

Cr = 0.439R – 0.399G -0.040B + 128;

*/

module rgb2ycbcr#(

//formula_y

parameter p0183_10b = 10'd47, //0.183*256 = 46.848

parameter p0614_10b = 10'd157,//0.614*256 = 15.7184

parameter p0062_10b = 10'd16,//0.062*256 = 15.872

parameter p16_10b = 18'd4096,//16*256 = 4096

//formula_cb

parameter p0101_10b = 10'd26,//0.101*256=25.856

parameter p0338_10b = 10'd86,//0.338*256=86.852

parameter p0439_10b = 10'd112,//0439*256=112.384

parameter p128_10b = 10'd32768,//128*256=32768

//formula_cr

// parameter p0439_10b = 10'd112,//0.439*256=112.384

parameter p0399_10b = 10'd102,//0.399*256=102.144

parameter p0040_10b = 10'd10//0.04*256=10.24

// parameter p128_10b = 10'd32768//128*256=32768

)

(

input clk,

input rst_n,

input [7:0] data_in_r,

input [7:0] data_in_g,

input [7:0] data_in_b,

input data_in_en, //input enable signal

input sync_in_h,

input sync_in_v,

output [7:0] data_out_y,

output [7:0] data_out_cb,

output [7:0] data_out_cr,

output wire data_out_en,

output wire sync_out_h,

output wire sync_out_v

);

//----pipeline-----------------------

wire signed_cb;

wire signed_cr;

reg [17:0] mult_y_r;

reg [17:0] mult_y_g;

reg [17:0] mult_y_b;

reg [17:0] mult_cb_r;

reg [17:0] mult_cb_g;

reg [17:0] mult_cb_b;

reg [17:0] mult_cr_r;

reg [17:0] mult_cr_g;

reg [17:0] mult_cr_b;

reg [17:0] add_y_0;

reg [17:0] add_y_1;

reg [17:0] add_cb_0;

reg [17:0] add_cb_1;

reg [17:0] add_cr_0;

reg [17:0] add_cr_1;

reg [17:0] add_final_y;

reg [17:0] add_final_cb;

reg [17:0] add_final_cr;

reg [9:0] around_y;

reg [9:0] around_cb;

reg [9:0] around_cr;

//----syn timing------------------

reg syn_data_in_en0;

reg syn_data_in_en1;

reg syn_data_in_en2;

reg sync_in_h0;

reg sync_in_h1;

reg sync_in_h2;

reg sync_in_v0;

reg sync_in_v1;

reg sync_in_v2;

/*

Y = 0.183R + 0.614G + 0.062B + 16;

Cb = -0.101R - 0.338G + 0.439B + 128;

Cr = 0.439R – 0.399G -0.040B + 128;

*/

/*--------------------------------------------------------

|---------pipeline1_mult----------------------------------|

--------------------------------------------------------*/

//---mult_formula_y---------------------|

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin

mult_y_r <= 18'd0;

mult_y_g <= 18'd0;

mult_y_b <= 18'd0;

end else

begin

mult_y_r <= data_in_r * p0183_10b;

mult_y_g <= data_in_g * p0614_10b;

mult_y_b <= data_in_b * p0062_10b;

end

//---mult_formula_cb---------------------|

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin

mult_cb_r <= 18'd0;

mult_cb_g <= 18'd0;

mult_cb_b <= 18'd0;

end else

begin

mult_cb_r <= data_in_r * p0101_10b;

mult_cb_g <= data_in_g * p0338_10b;

mult_cb_b <= data_in_b * p0439_10b;

end

//---mult_formula_cr---------------------|

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin

mult_cr_r <= 18'd0;

mult_cr_g <= 18'd0;

mult_cr_b <= 18'd0;

end else

begin

mult_cr_r <= data_in_r * p0439_10b;

mult_cr_g <= data_in_g * p0399_10b;

mult_cr_b <= data_in_b * p0040_10b;

end

/*--------------------------------------------------------

|---------pipeline1_add----------------------------------|

--------------------------------------------------------*/

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin

add_y_0 <= 18'd0;

add_y_1 <= 18'd0;

add_cb_0 <= 18'd0;

add_cb_1 <= 18'd0;

add_cr_0 <= 18'd0;

add_cr_1 <= 18'd0;

end else

begin

//Y = 0.183R + 0.614G + 0.062B + 16;

add_y_0 <= mult_y_r + mult_y_g;

add_y_1 <= mult_y_b + p16_10b;

//Cb = -0.101R - 0.338G + 0.439B + 128;

add_cb_0 <= mult_cb_r + mult_cb_g;

add_cb_1 <= mult_cb_b + p16_10b;

//Cr = 0.439R – 0.399G -0.040B + 128;

add_cr_0 <= mult_cr_g + mult_cr_b;

add_cr_1 <= mult_cr_r + p16_10b;

end

/*--------------------------------------------------------

|-----pipeline3_add_final(negtive = 0)-------------------|

--------------------------------------------------------*/

assign signed_cb = (add_cb_0>=add_cb_1);

assign signed_cr = (add_cr_0>=add_cr_1);

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

begin

add_final_y <= 18'd0;

add_final_cb <= 18'd0;

add_final_cr <= 18'd0;

end else

begin

add_final_y <= add_y_0 + add_y_1;

add_final_cb <= signed_cb?(add_cb_0 - add_cb_1):1'd0;

add_final_cr <= signed_cr?(add_cr_0 - add_cr_1):1'd0;

end

end

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin

around_y <= 10'd0;

around_cb <= 10'd0;

around_cr <= 10'd0;

end else

begin

around_y <= add_final_y[17:8]+{

9'd0,add_final_y[7]}; //around(add_final_y/256)

around_cb <= add_final_cb[17:8]+{

9'd0,add_final_cb[7]};

around_cr <= add_final_cr[17:8]+{

9'd0,add_final_cr[7]};

end

/*--------------------------------------------------------

|-----gray2ycbcr-----------------------------------------|

--------------------------------------------------------*/

assign data_out_y = (around_y[9:8]==2'b00)?around_y[7:0]:8'd255;

assign data_out_cb = (around_cb[9:8]==2'b00)?around_cb[7:0]:8'd255;

assign data_out_cr = (around_cr[9:8]==2'b00)?around_cr[7:0]:8'd255;

/*--------------------------------------------------------

|-----syn timing-----------------------------------------|

--------------------------------------------------------*/

//----data_in_en------------------------

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin

syn_data_in_en0 <= 18'd0;

syn_data_in_en1 <= 18'd0;

syn_data_in_en2 <= 18'd0;

end else

begin

syn_data_in_en0 <= data_in_en;

syn_data_in_en1 <= syn_data_in_en0;

syn_data_in_en2 <= syn_data_in_en1;

end

//----sync_in_h-------------------------

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin

sync_in_h0 <= 18'd0;

sync_in_h1 <= 18'd0;

sync_in_h2 <= 18'd0;

end else

begin

sync_in_h0 <= sync_in_h;

sync_in_h1 <= sync_in_h0;

sync_in_h2 <= sync_in_h1;

end

//----sync_in_v-------------------------

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin

sync_in_v0 <= 18'd0;

sync_in_v1 <= 18'd0;

sync_in_v2 <= 18'd0;

end else

begin

sync_in_v0 <= sync_in_v;

sync_in_v1 <= sync_in_v0;

sync_in_v2 <= sync_in_v1;

end

//---------------------------------------

assign data_out_en = syn_data_in_en2;

assign sync_out_h = sync_in_h2;

assign sync_out_v = sync_in_v2;

/*--------------------------------------------------------

|--------------------------------------------------------|

--------------------------------------------------------*/

endmodule

- 结果

5寸TFT电容触摸显示屏

图像:800*480像素

(1). (易烊千玺^^)网络原图:

(2). FPGA显示原图:

(3). FPGA灰度处理图:

参考资料:《FPGA系统设计与验证实战指南》

【注】:个人学习笔记,如有错误,望不吝赐教,这厢有礼了~~~