奋斗的小孩系列 FPGA学习altera系列: 第八篇 时序仿真及分配管脚操作

作者:奋斗的小孩 郝旭帅(转载请注明出处)

大侠好,欢迎来到FPGA技术江湖,江湖偌大,相见即是缘分。大侠可以关注FPGA技术江湖,在“闯荡江湖”、"行侠仗义"栏里获取其他感兴趣的资源,或者一起煮酒言欢。

今天给大侠带来“FPGA学习系列altera"系列,持续更新。

此学习心得是本人之前所写,所用设计软件为Quartus II 13.1,现Quartus 新版本已更新到20+,以下仅供初学者学习参考。后续会更新其他系列,敬请关注。话不多说,上货。

第八篇 时序仿真及分配管脚操作

时序仿真

时序仿真使用布局布线后器件给出的模块和连线的延时信息,在最坏的情况下对电路的行为作出实际地估价。时序仿真使用的仿真器和功能仿真使用的仿真器是相同的,所需的流程和激励也是相同的;唯一的差别是时序仿真加载到仿真器的设计包括基于实际布局布线设计的最坏情况的布局布线延时,并且在仿真结果波形图中,时序仿真后的信号加载了时延,而功能仿真没有。

那么下面我们就来实现和分析时序仿真:

1.全编译。点击:

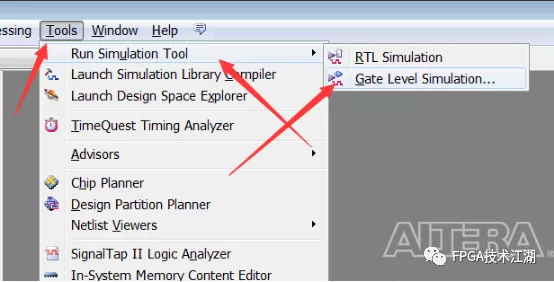

2.运行仿真工具。

3.选择模型&