模拟CMOS 基础知识4——短沟道效应

其他

2021-03-22 02:22:45

阅读次数: 0

模拟CMOS 基础知识4——短沟道效应以及对当前工艺的理解

参考资料

什么是短沟道效应?

- 在半导体的制造中,始终遵循着摩尔定律,于是集成电路的尺寸持续减小,于是MOSFET的沟道长度也相应地缩短,这就导致了MOSFET管中的S和D(源和漏)的距离越来越短,因此栅极对沟道的控制能力变差,这就意味着栅极电压夹断(pinch off)沟道的难度变大,于是使得亚阈值漏电(subthreshold leakage)现象,即短沟道效应(short-channel effect)更加容易发生。

- 胡正明教授对此给了个非常容易理解的例子:当一条水管很长的时候,那么用一块石头就可以很容易将其堵住(或者踩一脚),但是,当它很短的时候,这块石头就可能堵不住水管了,因为它可能放不下了,这就对应上段说的,沟道越短越难堵住电流(防止漏电)

短沟道效应影响因素

- 有下列五种,简单讲就是沟道短了容易漏电

- (1)由于电源电压没能按比例缩小而引起的电场增大;

- (2)内建电势既不能按比例缩小又不能忽略;

- (3)源漏结深不能也不容易按比例减小;

- (4)衬底掺杂浓度的增加引起载流子迁移率的降低;

- (5)亚阈值斜率不能按比例缩小

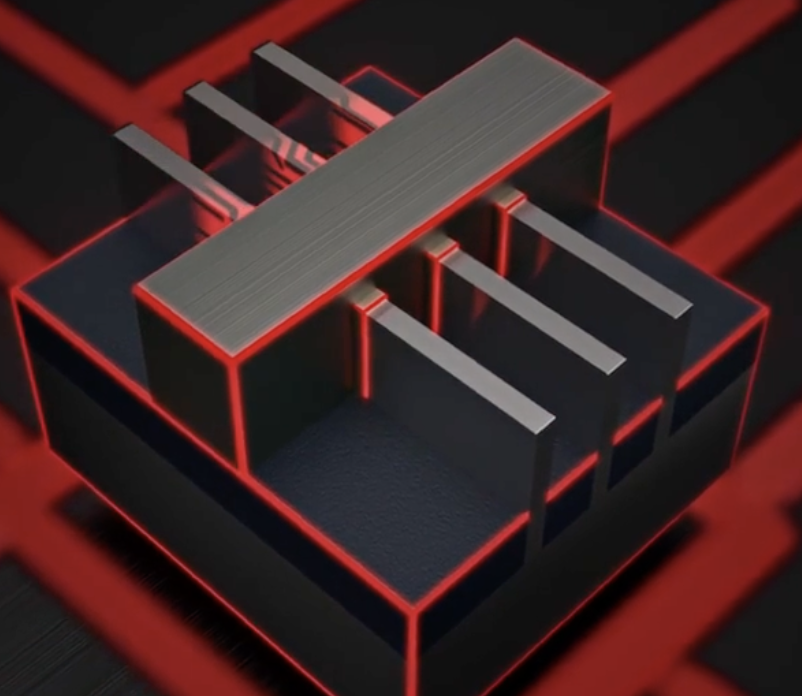

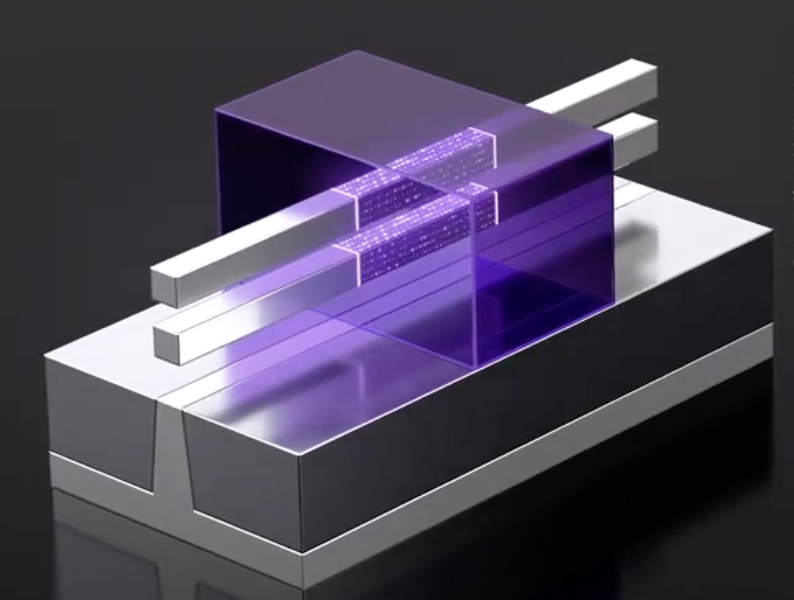

- 为了减小短沟道效应的影响,提出了应变硅技术、高K电介质氧化层、金属栅、SOI等新方法以改善器件性能。然而,在28 nm以下工艺节点,平面MOSFET器件结构中,栅极对沟道的有效控制面临严峻挑战,而革新的三维立体器件结构,如Fin FET结构具有更有效的栅极控制,可获得更优异的器件性能。

- 这里稍微有个疑问就是:为什么增加沟道接触面可以缓解短沟道的发生? 也就是下面FinFET工艺原文中实验部分的证明。目前我的理解就是可以使得栅极更容易地夹断电流。

FinFET工艺

总结

- 沟道短了——短沟道效应——新材料、FinFET工艺等缓解(k值(介电常数)与面积)

- 正如胡伟武老师在体系结构基础一书中预言:2020年左右摩尔定律迎来终结(确实有这个风声,但不知道台积电的3nm是咋搞的),说的是晶体管尺寸再难以缩小(参考晓龙888功耗翻车事件),若能再有所提升,大概率是新材料等发明

转载自blog.csdn.net/symuamua/article/details/114678333