在计算机存储结构中,存在 一个存储容量金字塔,靠近塔顶的延迟小/造价高/容量小,靠近塔底的相对延迟大/造价低/容量大,任意两级之间都存在一个映射关系。

在此,主要讨论cache和内存之间的映射关系,参考《大话处理器》5.2.3节 cache映射方式,学习总结如下。

1 直接映射

特点:主存中的一个块只能映射到Cache的某一特定块中去

好处:随便给一个地址,就知道其在哪个cacheline中

坏处:容易被踢,miss率高。如0x100先占据cacheline0,0x200来的时候就需要把0x100踢掉。

相当于是 set num = 1的 组相连映射方式

2 全相联映射

特点:主存中任何一块都可以映射到Cache中的任何一块位置

好处:效率高,miss率低

坏处:查找麻烦,需要遍历整个cache

3 组相关

特点:组间直接映射,组内全相联。现代处理中的Cache一般都采用组相关(set- associative)

好处:比 全相联 查找方便,比直接映射 miss率低

下图三和图四是一个set num = 2;way num = 4的组相关映射示意图,两者区别是,图三在映射时,memory的连续地址映射到同一个set;而图四是memory的地址交错地映射到同一个set。

如果采用图三的映射方式,会导致一个地址的tag bit位有两部分:bit[64:10] 和bit[8:6],故一般都采用图四的映射方式。

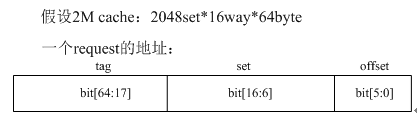

对于图四的映射方式,给定一个cache容量 = way num * set num * 1个cacheline的byte数,根据set num就可以得到set的index 地址bit。比如cache容量为2M,way num = 16,cacheline大小为64byte,则set num = 2048 = 2^11,所以set index = A[16:6]。

给定一个cache容量,Way num和set num是一个需要平衡的关系,way num太小容易被踢,而way太大 查找比对tag的逻辑就比较复杂(时序收敛问题),且set num太小也会造成miss率提高。现代处理器的way num一般为4 /8 /16/ 32等,一般不会超过32。 Way num 一般都是2的n次方,但也有非2的n次方的,很少见罢了。

图三 组相关映射示意图(一)

图四 组相关映射示意图(二)