Xilinx_JESD204B_AXI配置

说明:通过FPGA的高速数据接口JESD204B对AD9625进行高速采集。

环境:Vivado2018.3。

IP核:JESD204(7.2)。

参考手册:pg066_jesd204 v7.2。

资料以及IP_licence:JESD204B

AXI协议资料:AXI

1.JESD204B概述

JESD204B是一种新型的高速串行ADC/DAC数据传输接口,JESD204B包括3个子类,分别是子类0,子类1,子类2。三个子类主要是根据同步方式的不同划分的。

其他相关资料移至官方文档以及互联网,主要想写一下JESD204B在XilinxFPGA上的应用。

1.1 JESD204B接口术语

| S | 每个帧周期每个转换器发送的样本 |

|---|---|

| M | 每个转换器件(链路)的转换器数 |

| L | 每个转换器件(链路)的通道数 |

| N | 转换器分辨率 |

| N’ | 每个样本的总位数 |

| CF | 每个转换器件(链路)每个帧时钟周期的控制字数 |

| CS | 每个转换样本的控制位数 |

| K | 每个多帧的帧数 |

| HD | 高密度模式 |

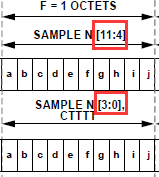

| F | 每帧的8位字数 |

| C | 控制位(超范围、时间戳) |

| T | 结束位 |

1.2 JESD204B 层

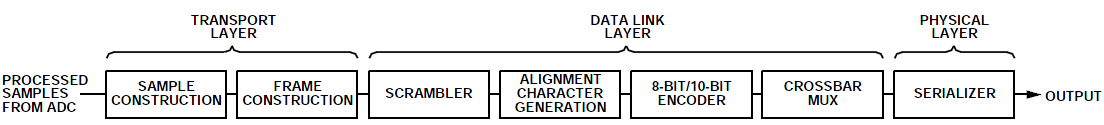

以下为AD9625通过JESD204B高速接口输出的示意图,由此示意图理解JESD204B传输过程。

传输层:

传输层将数据(由样本和可选控制位组成)包装成8位字并发送至数据链路层。传输层受链路配置数据产生的规则控制。它根据规则包装数据,需要时添加结束位以填补空隙。

数据链路层:

数据链路层负责执行通过链路传送数据的低级功能,包括加扰数据(可选),处理链路上的字符、帧和通道的同步过程,将8位数据字编码为10位字符,以及在数据输出中插入适当的控制字符。数据链路层还负责发送初始通道对齐序列(ILAS),它包含链路配置数据,接收机(Rx)利用它来验证传输层的设置。

物理层:

物理层由以串行时钟速率运行的高速电路构成,包括串行化电路和高速驱动器。

2JESD204B_AXI介绍

2.1 AXI介绍

AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。它的地址/控制和数据相位是分离的,支持不对齐的数据传输,同时在突发传输中,只需要首地址,同时分离的读写数据通道、并支持Outstanding传输访问和乱序访问,并更加容易进行时序收敛。AXI 是AMBA 中一个新的高性能协议。AXI 技术丰富了现有的AMBA 标准内容,满足超高性能和复杂的片上系统(SoC)设计的需求。

2.2 JESD204B__AXI_Lite接口

Xilinx的高速数据接口JESD204(7.2)是通过AXI-Lite总线接口配置的。打开IP核如下

2.3 AXI-Lite接口介绍

AXI4-Lite接口是AXI4接口的一个子集

AXI4-Lite特点:

1、所有的传输突发均为1。

2、所有数据访问的大小与数据总线的宽度相同。

3、支持32bit或64bit数据总线宽度。

4、所有访问等效于AWCACHE或ARCACHE等于b0000。

不支持独占访问。

AXI4-Lite不支持的信号

AWLEN,ARLEN

突发长度定义为长度1,等于AWLEN或

ARLEN等于零。

AWSIZE,ARSIZE

所有访问都定义为与数据总线的宽度相同。支持固定的32位或64位数据总线宽度。

AWBURST, ARBURST

突发类型没有意义,因为突发长度为1,因此所有的突发类型相同。

AWLOCK, ARLOCK

所有访问都定义为“普通访问”,等效于AWLOCK或 ARLOCK为b0。

AWCACHE , ARCACHE

所有访问等效于AWCACHE或 ARCACHE等于b0000。

WLAST, RLAST

所有突发长度为1,等价于WLAST, RLAST总是被断言。

RRESP, BRESP

RRESP、BRESP不支持EXOKAY响应通道。

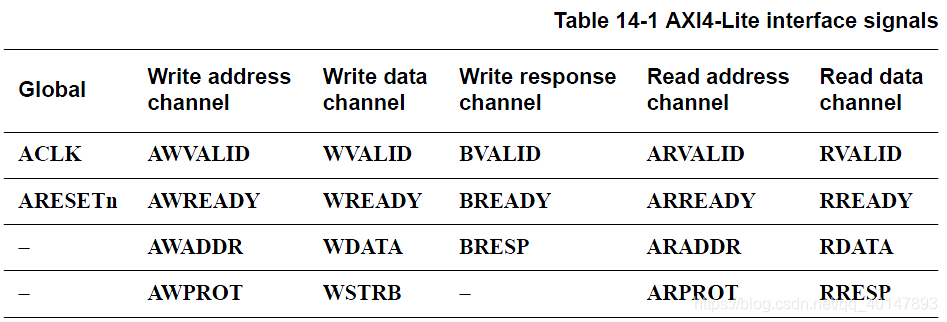

2.4 AXI-Lite接口信号

全局信号:

| ACLK | 主 | 全局时钟信号,所有的信号都在此上升沿采样 |

|---|---|---|

| ARESETn | 主 | 全局复位信号,该信号低电平有效 |

写地址通道:

| AWVALID | 主 | 写地址有效。表示有效的写地址和控制信息。1:地址可用、0:地址不可用 |

|---|---|---|

| AWREADY | 从 | 接收地址准备。表明从机已经准备好接收地址信息。1:从机准备就绪、0:从机未准备就绪 |

| AWADDR | 主 | 写地址。写地址总线给出写突发中第一次传输的地址。 |

| AWPROT | 主 | 保护类型 |

写数据通道:

| WVALID | 主 | 写有效。表明写数据有效。1:写数据可用、0:写数据不可用。 |

|---|---|---|

| WREADY | 从 | 接收数据准备。1:从机准备就绪、0:从机为准备就绪、 |

| WDATA | 主 | [31:0],写数据。写数据总线的宽度可以为8、16、32、64、128、256、512或1024。 |

| WSTRB | 主 | [3:0],写数据选择。该信号指示存储器中更新的字节通道。WSTRB[n]对应选通WDATA[8×n]+7:(8×n)。 |

写响应通道:

| BVALID | 从 | 写入响应有效。1:写响应可用、0:写响应不可用。 |

|---|---|---|

| BREADY | 主 | 接收响应准备就绪。1:主机准备接收就绪、0:主机未准备接收就绪 |

| BRESP | 从 | [1:0]写响应。该信号指示写事务的状态。允许的响应为OKAY、EXOKAY、SLVERR、DECERR |

读地址通道:

| ARVALID | 主 | 读地址有效。1:读取地址有效、0:读地址无效 |

|---|---|---|

| ARREADY | 从 | 读取地址准备就绪。1:从机地址准备就绪、0:从机地址未准备就绪。 |

| ARADDR | 主 | [31:0],读取地址。读取地址总线提供读取突发事务的初始地址 |

| ARPROT | 主 | 保护类型 |

读数据通道:

| RVALID | 从 | 读数据有效。1:读取数据可用、0:读取数据不可用 |

|---|---|---|

| RREADY | 主 | 读取数据就绪。1:主机准备就绪、0:主机为准备就绪。 |

| RDATA | 从 | [31;0],读取数据。读取数据总线的宽度可以为8、16、32、64、128、256、512或1024。 |

| RRESP | 从 | 读取响应。该信号指示读取传输的状态允许的响应为OKAY、EXOKAY、SLVERR、DECERR |

OKAY、EXOKAY、SLVERR、DECERR:

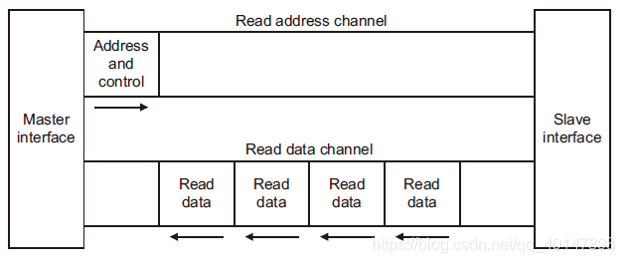

2.5 AXI-Lite读写

读地址通道:

每个读事务都有自己的地址通道。适当的地址通道携带通信所需的所有地址和控制信息。AXI协议支持以下机制:

可变的突发长度,每个突发长度从1-16个数据。

(连续传输的周期数就是突发长度。)

突发传送的大小为8-1024bit

…

读取数据通道:

读取数据通道可同时传输读取数据和来自设备从设备到主设备的响应信息。

数据总线,可以是8、16、32、64、128、256、512或1024bit。

一个指示读取事务完成状态的读取响应

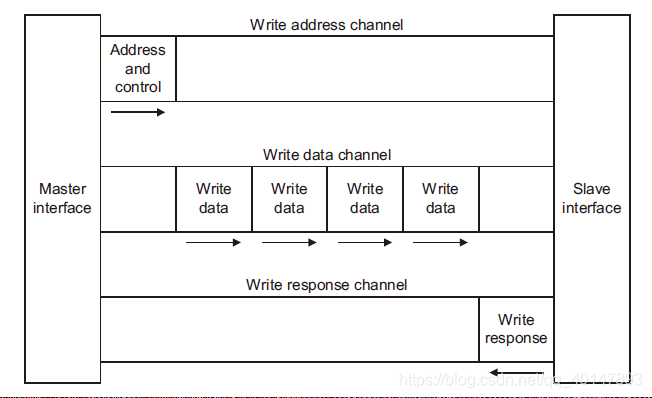

写地址通道:

每个写事务都有自己的地址通道。适当的地址通道携带通信所需的所有地址和控制信息。AXI协议支持以下机制:

可变的突发长度,每个突发长度从1-16个数据。

(连续传输的周期数就是突发长度。)

突发传送的大小为8-1024bit

…

写数据通道:

将写数据从主机传送到从机

数据总线,可以是8、16、32、64、128、256、512或1024bit。

每八个数据位的一个字节通道选通脉冲,指示数据总线的哪个字节有效。

写响应通道:

写通道响应为从设备提供了一种响应事务的方法。所有写事务使用完成信令。

完成信号对于每个脉冲串仅发生一次,而不是针对其中的每个单独的数据传输发生一次突变。

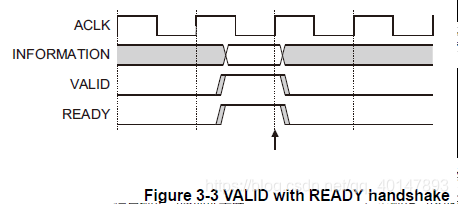

2.6 AXI-Lite握手过程

所有五个通道都使用相同的VLAID/READY握手机制来传输和控制信息。这种双向流量控制机制使主机和从机都可以控制数据和信息的移动速率。主机,指示何时有数据或控制信息。从机,产生READY信号,以指示它接收数据或控制信息。传输仅当VALID和READY信号均为高时。

通道握手信号之间的依赖:

为避免出现死锁情况,您必须观察到两者之间存在的依赖关系。

握手信号。

在任何传输中:

●一个AXI组件的VALID信号不得取决于READY信号。

●READY信号可以等待VALID信号的断言。

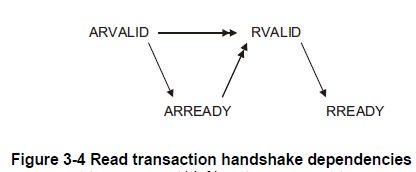

读取握手依赖关系:

| 读取握手信号 | 发起者 | 说明 |

|---|---|---|

| ARVALID | 主 | 读地址有效。1:读取地址有效、0:读地址无效 |

| RVALID | 从 | 读数据有效。1:读取数据可用、0:读取数据不可用 |

| ARREADY | 从 | 读取地址准备就绪。1:从机地址准备就绪、0:从机地址未准备就绪。 |

| RREADY | 主 | 读取数据就绪。1:主机准备就绪、0:主机为准备就绪。 |

从机可以在声明ARREADY之前等待ARVALID声明

从设备必须等待ARVALID和ARREADY都被声明后才能开始

通过声明RVALID返回读取的数据。

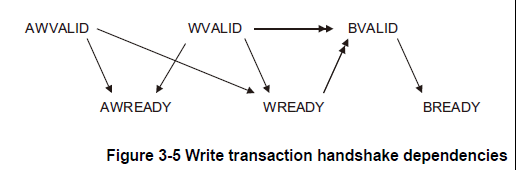

写入握手依赖关系:

| 写入握手信号 | 发起者 | 说明 |

|---|---|---|

| AWVALID | 主 | 写地址有效。表示有效的写地址和控制信息。1:地址可用、0:地址不可用 |

| AWREADY | 从 | 接收地址准备。表明从机已经准备好接收地址信息。1:从机准备就绪、0:从机未准备就绪 |

| WVALID | 主 | 写有效。表明写数据有效。1:写数据可用、0:写数据不可用。 |

| WREADY | 从 | 接收数据准备。1:从机准备就绪、0:从机为准备就绪、 |

| BVALID | 从 | 写入响应有效。1:写响应可用、0:写响应不可用。 |

| BREADY | 主 | 接收响应准备就绪。1:主机准备接收就绪、0:主机未准备接收就绪 |

主机不得在等待从机断言AWREADY或WREADY之前断言AWVALID或WVALID

从机可以在声明AWREADY之前等待AWVALID或WVALID或两者

从机可以在声明WREADY之前等待AWVALID或WVALID或两者

从机必须在声明前等待WVALID和WREADY在BVALID断言之前声明。

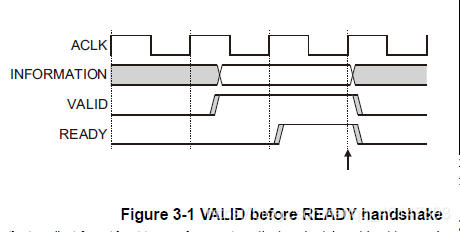

握手方式:

VALID在READY之前:

主机放置数据或控制信号,并将VALID信号驱动为高电平。

来自主机的数据或控制信息保持稳定,直到目标驱动READY信号为高电平,表示它接受数据或控制信息,箭头显示何时开始传输。

在声明VALID之前,不允许等待READY声明。一旦VALID被

断言它必须保持断言直到握手发生。

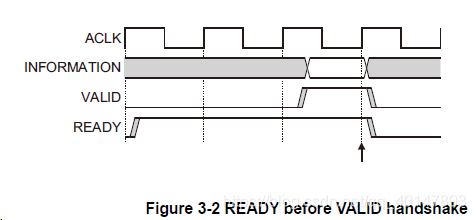

READY在VALID之前:

目标驱动器在数据或控制信息被写入之前就驱动READY为高,这表明从机可以在一个接收器中接受数据或控制信息生效后立即循环。允许在声明相应的READY之前等待VALID声明。 如果声明了READY ,则允许在声明VALID之前取消声明READY 。

VALID和READY同时:

主机和从机恰好在同一周期内指示他们可以传输数据或控制信息。

2.7 AXI-Lite读写时序

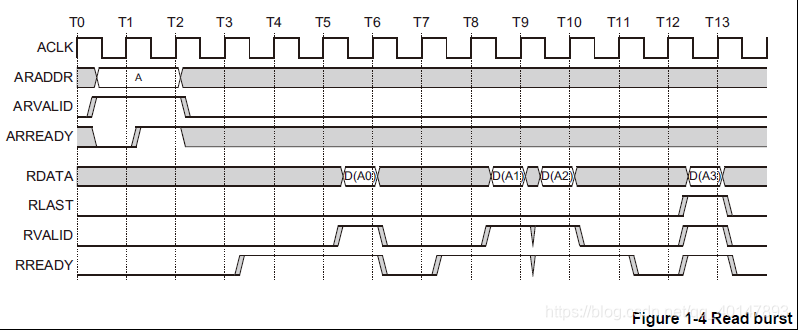

AXI-Lite读:

地址出现在地址总线上后,数据传输将在读取的数据通道上进行。从机将VALID信号保持为低电平,直到读取数据可用为止。对于最终数据传输突发时,从机将RLAST信号置位,表明正在传输最后一个数据项。

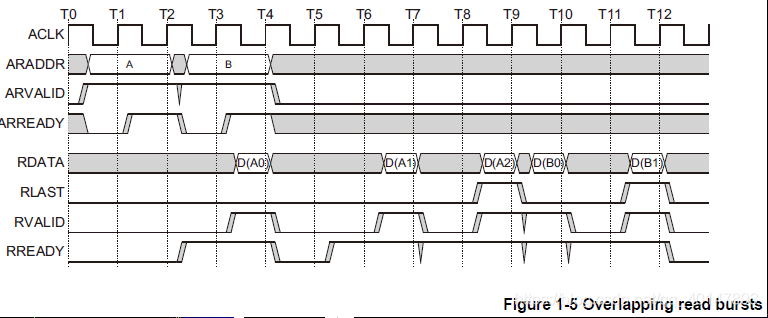

AXI-Lite重叠突发读取:

显示了从机接收到第一个突发地址后,主机如何驱动另一个突发地址使得从机能够与第二个突发并行的开始处理第二个突发数据,一次完成传输。

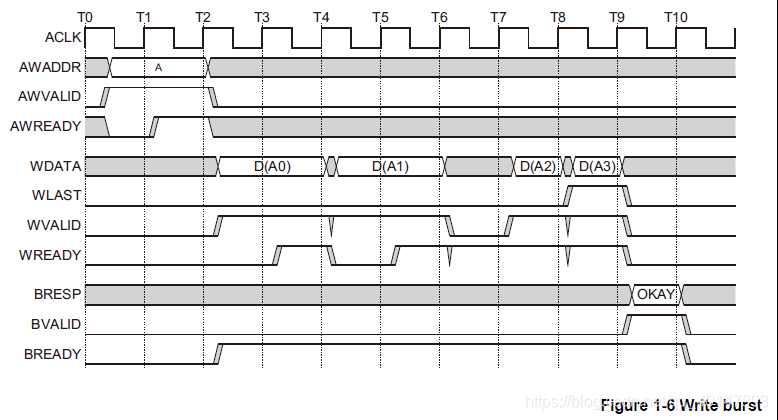

AXI-Lite写:

当主机发送地址和和控制信息至写地址通道,然后主机发送每个数据至写数据通道。当主机发送最后一个数据项时,WLAST信号变为高。当从机接收了所有数据项后,它将写响应返回至主机表示写操作完成。

3.JESD204B_AXI配置

JESD204B IP核配置:

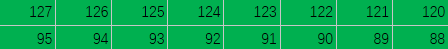

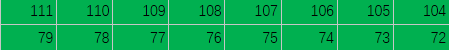

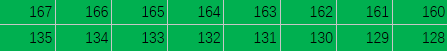

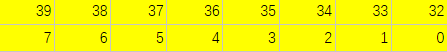

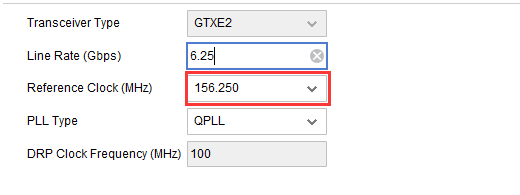

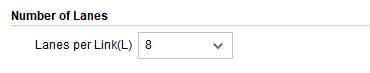

Page1

Page2

Page3

Page4

说明:

AXI4-Lite配置时钟: 默认为100MHz。对于ultrascale器件,频率范围为10MHz~200MHz,对于7系列器件,如果IP核的模式为“Include Shared Logic in example design” ,则频率范围为10MHz~200MHz;如果IP核的模式为“Include Shared Logic in core” ,则频率范围和Transceiver DRP时钟频率范围相同。

传输线速率: 6.25Gbps

ADC采样速率为2.5Gsps。

(2.5G×16bit×8/10B)/8Lane=6.25Gbps。

参考时钟: 156.25Mhz

6.25G/(32×8/10B)=156.25M

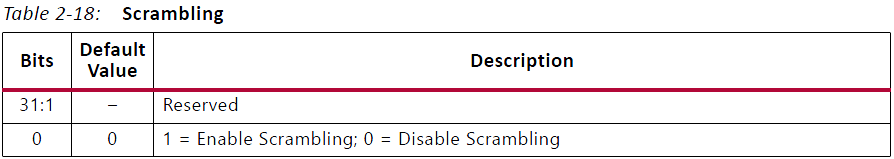

JESD204B 寄存器配置:

用户在使用JESD204 IP核时需要通过AXI_Lite4协议对内部的寄存器进行配置,正确配置IP核的工作参数,以及在调试过程中读某些状态寄存器的参数,以便确定IP核的工作状态,寄存器详情查看文档pg066。

例如:

0X000: JESD204版本

0x00C:扰码开关

0x020:F

0x024:K

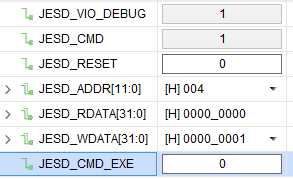

3.1 JESD204B配置驱动示例_寄存器配置

方便调试,将AXI_Lite接口接入VIO调试。调试过程如下:

JESD_VIO_DEBUG:

1:通过Vavido的VIO模式就可以对JESD204 IP进行配置。

0:通过代码配置。

JESD_CMD

1:读寄存器

0:写寄存器

JESD_RESET

1:复位

0:取消复位

JESD_ADDR

进行读写的地址。

JESD_RDATA

读取JESD_ADDR地址的数据。

JESD_WDATA

写入JESD_ADDR地址的数据。

JESD_CMD_EXE

1:触发一次读写操作。

0:默认为0,1时触发一次读写操作。

读写试例:

读寄存器0x000 版本号:

读寄存器0x038 锁定状态:

读写寄存器0x024 K值:

3.2 JESD204B AXI驱动波形

驱动波形:

AXI读

读地址:主机只有在驱动有效地址和控制时才能声明ARVALID信号 信息。在从机接受地址和控制信息之前,它必须保持置位状态并声明关联的ARREADY信号。

读数据:从机只有在驱动有效的读取数据时才能声明RVALID信号。RVALID必须 保持置位,直到主机接受数据并置位RREADY信号为止。

AXI写

写地址:主机只有在驱动有效地址和控制时才能声明AWVALID信号。从机接收地址和控制信号之前,它必须保持置位状态,直到AWREADY信号置位。

写数据:在写突发期间,主机只有在驱动有效写操作时才能声明WVALID信号数据。WVALID必须保持置位,直到从机接受写入数据并置位WREADY信号。

写响应:从机只有在驱动有效的写响应时才能声明BVALID信号。BVALID在主机接受写响应并声明BREADY之前,必须保持声明状态。

BREADY的默认值可以为高,但前提是主机始终可以接受写入在一个周期内做出响应。

3.3 JESD204B AXI驱动代码

4. AD9625调试注意事项

测试模式可以按照下图以及下图寄存器的配置执行:

对接AD9625导致SYNC无法拉高或者间接性拉高原因:

1、两边模式配置不一样。

检查AD9625与FPGA的JESD204B的配置模式是否匹配。

2、AD9625写完寄存器没更新。

查看手册:

AD9625的寄存器地址被屏蔽。寄存器写入不影响器件操作,直到通过将0x01写入地址0x0FF发出传输命令,从而设置传输位。 这允许寄存器在传输位置位时内部同时更新。当传输位被置位时,内部更新发生,然后该位自动清零。

4.1 AD9625数据提取

官方给的数据产生图:

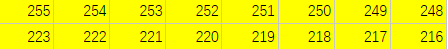

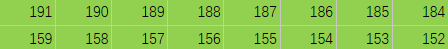

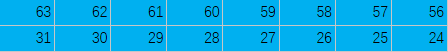

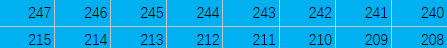

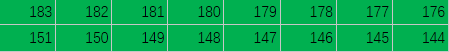

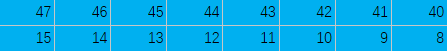

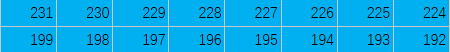

256 bit数据详述:

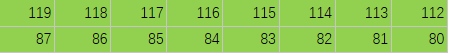

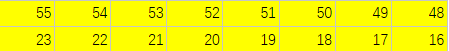

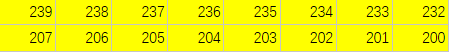

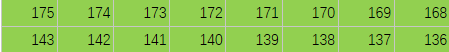

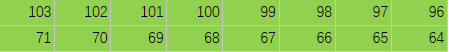

256bit数据按照以下方式表示,8行就是8Lane数据,数据从高到低位(D256-D0)如下所示:

8Lane数据里包含了16个采样点,每个采样点里有12bit有效数据。

从下面的16个采样点里均提取12bit有效数据即得到采集的有效值。

(括号了的数值代表D256-D0)。

SAMPLE0:

SAMPLE1:

SAMPLE2:

SAMPLE3:

SAMPLE4:

SAMPLE5:

SAMPLE6:

SAMPLE7:

SAMPLE8:

SAMPLE9:

SAMPLE10:

SAMPLE11:

SAMPLE12:

SAMPLE13:

SAMPLE14:

SAMPLE15:

为什么会有16个SAMPLE,有什么用怎么得到最终结果?

观察下面SMPLE0的波形为正弦波(AD端施加的事正弦信号),其实SMPLE0-SMPLE15是看起来几乎一样的波形,因为设备有限,之前截图直截了一个,现在没有信号源…凑活看。

为什么16个SAMPLE是相同的波形,解释如下图,AD端我们施加一个正弦信号,图中四种颜色的点代表4个SAMPLE,所以每个SAMPLE波形都是看着一样的,其实相邻的SAMPLE是正弦信号上相邻的采样点,可以说每个SAMPLE都表示AD输入端信号的轮廓,最终将16个SAMPLE合成一个信号将会变成比SAMPLE信号密集16倍的最终信号。

4.2 FPGA JESD204B配置156.25M时钟为什么能采集2.5GSPS的AD数据

JESD204B参考时钟为156.25MHz

采集通道Lane=8

8Lane在一个参考时钟出16个采样点。

采集速率:16*156.25=2500M=2.5G。

4.3 调试结果

写的有点匆忙。

★★★如有错误欢迎指导!!!