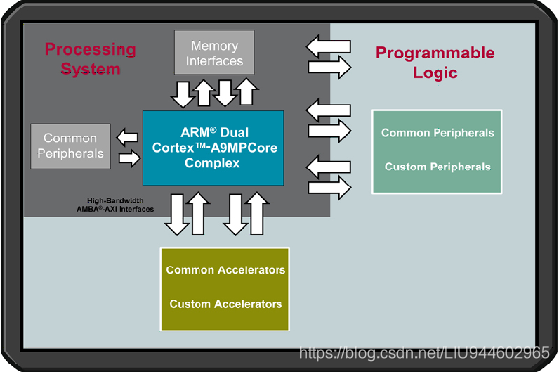

Zynq 7000 SoC 是业界首款All Programmable SoC

组成:

PL(FPGA部分)

PS(ARM部分)

PL和PS数据传输的

高效接口:AXI和ACP

PS: 处理系统(Processing System),与FPGA无关的ARM的SOC的部分。

PL: 可编程逻辑 (Progarmmable Logic),FPGA部分。

APU: 应用处理器单元(Application Processor Unit)。位于PS里面的中心位置。

SCU: Snoop Control Unit,用来保持双核之间的数据Cache的一致性。

主要工具:Vivado(PL部分实现)

常用步骤:

1、Create New Project,选择芯片

2、Create Block Design

3、Add IP,并按照硬件原理图进行配置、连线

4、右击 .bd文件, 单击Generate Output Products

5、右击 .bd文件, 选择Create HDL Wrapper ,产生顶层文件

6、左侧导航栏点击Run Synthesis

7、左侧导航栏点击Run Implementation

8、左侧导航栏点击Generate Bitstream

9、File–Export–Export Hardware,注意选中Include bitstream※

10、File–Launch SDK

主要工具:SDK(PS部分实现,代码调试和工程下载)

常用步骤:

1、在Vivado建立的工程基础上,File – New --Application Project,建立一个FSBL工程

2、File – New --Application Project,建立一个项目工程,并编写代码

3、点击Xilinx Tools – Create Zynq Boot Image, 依次添加三个文件【fsbl.elf、PL.bit、usercode.elf】,再点击Create Image即可生成可下载bin文件。

4、板子通电,连接JTAG。点击Xilinx Tools – Program Flash,选择上一步生成的.bin文件,再点击Program等待烧写结束即可。

实际操作可点击:双CPU试验