不变的坐姿令他脊椎变形,

精确到毫米的工艺使他视力受损,

但不容丝毫分心的专注让他获得了心灵的平静。

马尔克斯《百年孤独》

\qquad

\qquad 开发CYC-GPS接收机前后花了1年半时间,最终获得了预定结果,但留下了一大缺憾,使用的射频板不是自己开发的。为弥补此缺憾,我按自己的思路设计和制作了一系列射频板,进而开发了新底板HD-GR-1,与新开发的双模射频板HD-MAX2769-2RF-2组成了我硬件学习的最后一件制作,一台GPS+BDS双模接收机,命名为HD-GR。由于已经轻车熟路,整个设计、制作和测试只用了约3个月时间。

(1) 射频板HD-MAX2769-2RF-2

\qquad 对于射频板,我之前未能制作出能够正常工作的,现在我要参照HG-RF02-C,尝试再次进行开发。为此,我以MAX2769为前端芯片,设计、制作了一系列射频板,主要包括:

- HD-MAX2769-RFFE – 单模射频板

- HD-MAX2769-2RF-2 – 双模射频板(第2版)

- HD-MAX2769-LNA-2 –“单模+中频低噪输出”射频板(第2版)

它们都能正常工作,其中最被看重的是双模板HD-MAX2769-2RF-2,它尽管明显烙上了HG-RF02-C的印记,但具有自己的特点。它将与底板HD-GR-1一道,组成一台GNSS双模接收机,下面对它予以简介。

\qquad HD-MAX2769-2RF-2为一单/双模兼容射频板,板上预留了焊接两颗MAX2769芯片的位置,适合于GPS、BDS、Galieo、Glonass单频、单/双系统开发。当配置为支持单系统时,只需焊接一片MAX2769(称为MAX2769-1)及其外围电路。当希望支持双系统或支持单/双兼容系统时,则需额外焊接一片MAX2769(称为MAX2769-2)及其外围电路。支持双系统时,也只需接入一个天线,它当然需要支持两个相应频点,比如:1575.42 MHz的GPS L1信号和1561.098MHz的BDS B1I信号。

\qquad 图1显示了射频板HD-MAX2769-2RF-2的正面器件和布局:

- 两个射频头MMCXs,分别用于连接有源天线和无源天线;

- 来自一个射频头的信号经过一个低噪放大器MAX2659,引入到MAX2769-1的LNA1或LNA2引脚;

- MAX2769-1的低噪放输出(LNAOUT引脚)分别引入MAX2769-1和MAX2769-2的混频输入(MIXIN引脚)。通过使用MAX2769芯片的SPI接口,可以在导航软件中对MAX2769-1和MAX2769-2进行编程,让它们分别将所拟处理的GNSS射频信号下变频为基带信号。

- 外围滤波电路,为MAX2769-1和MAX2769-2提供滤波;

- 一片温补晶振TCXO(背面),为MAX2769-1和MAX2769-2提供时钟信号;

- 两个通用I/O插槽,用于连接HD-GR-1底板。

\qquad 另外,模块需要外部提供3.3V和5V电源,以及保证电源稳定性。

(2) 底板HD-GR-1

\qquad 底板HD-GR-1的基本设计目标是与射频板HD-MAX2769-2RF-2紧密配合,组成一台双模接收机。为此,相对底板CYC-GPS-3,它做了以下调整:

- 核心器件恢复使用尺寸较小的FPGA EP4CE22(TQFP-144封装);

- 扩充射频接口定义,以支持接收来自射频板的双模数字IF信号;

- 去掉多余的通用接口;

- 在PCB板顶层布局所有器件,仔细调整器件位置和优化信号走线。

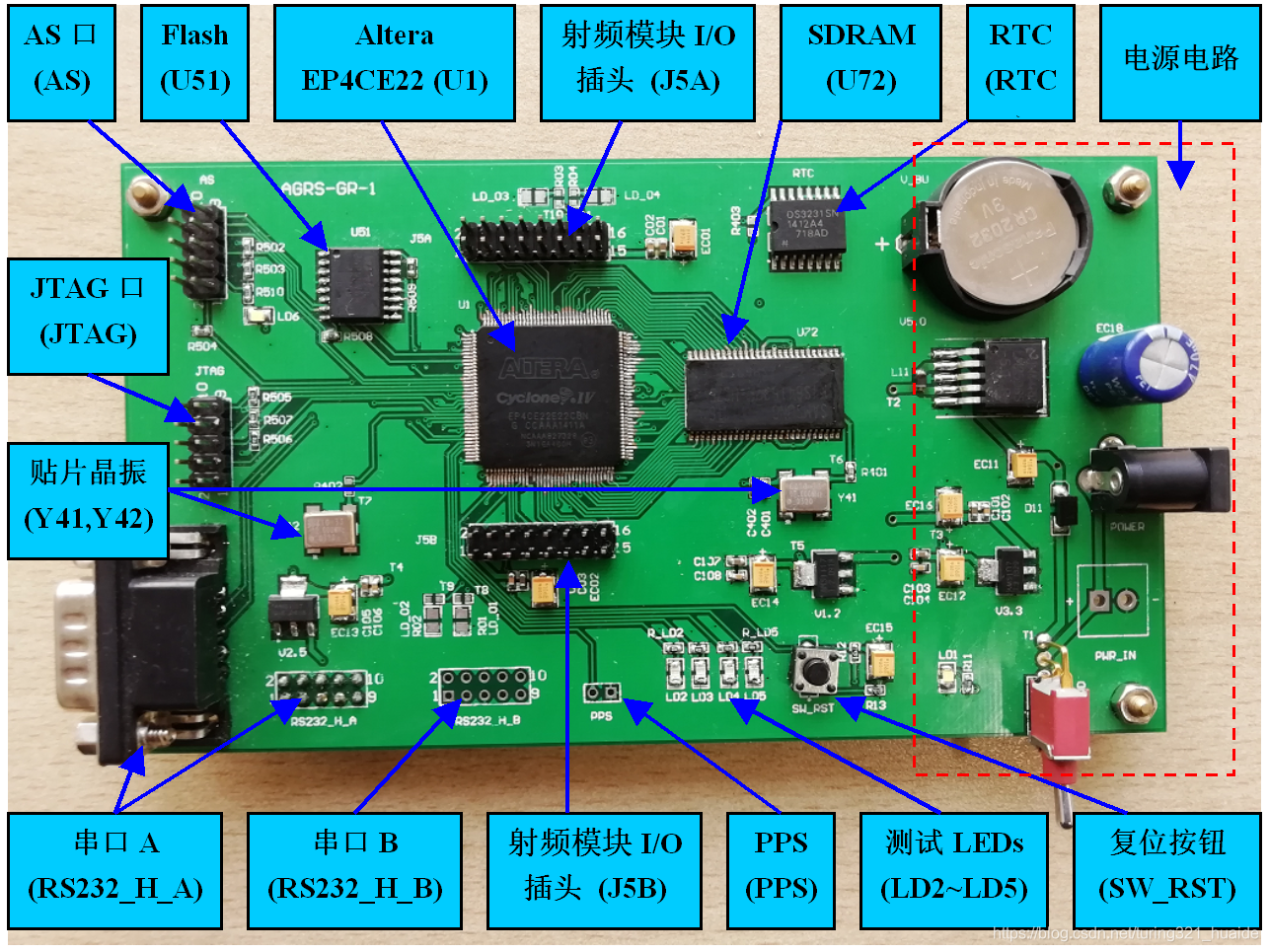

\qquad 底板HD-GR-1的主要特性如下(参见图2):

- FPGA芯片:Altera Cyclone® IV EP4CE22E144 FPGA

- 配置设备:Numonyx M25P64(兼容EPCS64)

- 射频接口:两个16-针插头(GPIOs)提供32个I/O引脚,用于接收射频前端信号(包括时钟信号),以及提供5V/3.3V电源和用于接地。

- 内存芯片:8-MByte SDRAM

- RTC芯片:Maxim DS32X35

- 时钟系统

- 两个底板时钟振荡器(可选焊接)

- 两个外部时钟信号(通过射频前端接口引入)

(3) HD-GR接收机

\qquad 之前,只要涉及到硬件逻辑设计和导航固件开发,基本上一笔带过,这次更会如此。以这种态度对待它们,并非它们不重要,而是它们太过繁琐、专业,不便过分触及。在结束我的硬件学习总结之前,将会谈谈对于它们的一般认识。不过,在这里先说一说,相比于CYC-GPS-3接收机,底板HD-GR-1完成了哪些进一步工作。

\qquad CYC-GPS-2接收机已经在架构、功能、语法层面验证了硬件逻辑设计和导航固件开发的可行性,CYC-GPS-3接收机则完成了大量调整、纠错、优化、提速工作,并最终使开发的导航固件能够通过跟踪GPS卫星或BDS卫星,正确、稳定、实时地解算出静态接收机的PVT。

\qquad 要将CYC-GPS-3单模接收机升级、改造为HD-GR双模接收机,需在底板FPGA芯片一级完成的任务主要是调整、合并和优化基带模块和导航固件的代码。只要底板HD-GR-1上的FPGA芯片有足够多逻辑单元、NIOS II软核时钟频率足够快、FPGA逻辑的时序信号满足约束要求,则这一过程是直截了当的:

- 调整、合并CYC-GPS-3接收机中支持处理GPS和BDS信号的基带模块,修改基带模块的顶层接口,让它能接收和处理来自射频板HD-MAX2769-2RF-2的双中频信号;根据FPGA芯片所能分配使用的逻辑资源,合理地选择跟踪通道总数;调整和实现与导航固件之间交换数据的接口定义;

- 设计和实现混合系统导航解算的模型和算法;调整、合并CYC-GPS-3接收机中支持处理GPS和BDS信号的导航固件代码;以各种方式最大限度地提高导航固件和NIOS II软核运行速度,例如:

- 选择快速模型构建NIOS II软核;

- 提高NIOS II软核时钟频率;

- 使用FPGA紧耦合片上存储器加速导航固件代码执行和数据存取速度;

- 使用定点运算代替浮点运算加速导航固件执行;

- 优化特定算法加速导航固件执行。

\qquad 在完成以上任务后,终于从某一天起,达到了HD-GR接收机的开发目标,通过同时跟踪和利用GPS卫星和BDS卫星信号,正确、稳定、实时地解算出静态接收机的PVT。图3显示了这台多少有点模样的GPS+BDS双模接收机(板卡)的外观。