一个勤劳的知识搬运工小蜜蜂。

目录

3.2.2多电压设计(Multi-Voltage Domain)

一、功耗的类型

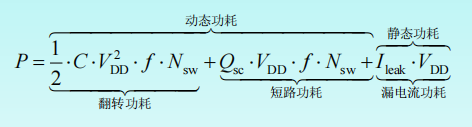

功耗由动态功耗和静态功耗构成。

随着工艺的进步,深亚微米下,静态功耗在总功耗中占的比例上升。

式中,C为结点电容,Nsw为单时钟内翻转晶体管数目,f为系统工作时钟频率,VDD为供电电压,Qsc为翻转过程中的短路电量,I_leak为漏电流。

1.1动态功耗

负载电容充放电时引起的功耗,称为动态功耗。

动态功耗又有翻转功耗和短路功耗。翻转功耗在当前的设计电路中仍然占主要部分,短路功耗在动态功耗中所占比例较小。

翻转功耗是数字电路要完成功能计算所必须消耗的功耗,称为有效功耗;如下图所示:

短路功耗是由于CMOS在翻转过程中PMOS管和NMOS管同时导通时消耗的功耗,称为无效功耗。如下图所示:

1.2静态功耗

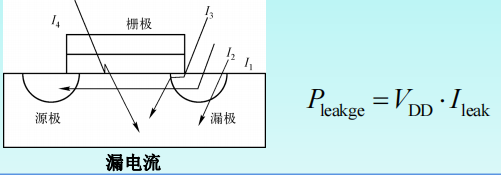

漏电流引起的功耗,称为静态功耗。

如上图所示,漏电流主要由以下几部分组成:

- PN结反向电流I1(PN-junction Reverse Current);

- 源极和漏极之间的亚阈值电流I2(Sub-threshold Current);

- 栅极漏电流,包含栅极和漏极之间的感应漏电流I3(Gate Induced Drain Leakage);

- 栅极和衬底之间的隧道漏电流I4(Gate Tunneling)。

为了满足工作频率越来越高的需求,就会降低晶体管的阈值电压Vt,使得晶体管能够高速翻转。但是,如果Vt太低,晶体管不能完全关断,这将产生很大的静态功耗。

1.3 CMOS工艺的发展与功耗的变化

不同电压、不同工艺、不同频率及不同晶体管数目下CMOS电路的功耗实例:

(1)随着工艺的进步,电源电压随之减小以降低动态功耗,同时降低了阈值电压Vt,导致了系统静态功耗的增加;

(2)随着工艺的进步,系统的工作电压降更低,同时带来更低的晶体管动态功耗,但是由于时钟频率的提高和晶体管数目的增多,导致系统的总功耗将越来越大;

(3)随着工艺的改进,系统的功耗在不断增加,同时待机功耗和工作功耗越来越相近,这主要是由电路中漏电流增大引起的。

随着工艺的进步,晶体管的尺寸将越来越小,同时带来的是更低的工作电压和更大的漏电流。工作电压的降低减小了晶体管的动态功耗,但是由于主频的提高及晶体管数目的增多,系统的总功耗越来越大。由于漏电流的增大,静态功耗在系统总功耗中所占比例不断增大。

1.4 SoC中的主要功耗

两个典型的SoC系统中的功耗组成:

二、低功耗设计方法

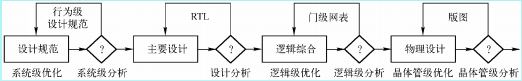

低功耗反馈的前向设计方法:

各层次优化方法及优化效果:

三、低功耗技术

3.1 工艺优化

3.1.1多阈值工艺(Multi-Vt Design)方法

低阈值的标准逻辑单元:速度快、漏电流大;

高阈值的标准逻辑单元:速度慢、漏电流小。

在设计中可以在关键路径上使用低阈值的标准逻辑单元来优化时序,在非关键路径上使用高阈值的标准逻辑单元来优化漏电流。

3.1.2电源门控(Power Gating)方法

在正常工作状态,Sleep信号为低电平,高阈值MOS管处于导通状态;当处于睡眠状态时,Sleep信号为高电平,切断电源,并且由于采用了高阈值MOS管作为开关,可以有效地减少漏电流。

3.2 电压优化

3.2.1体偏置(Body Bias)

晶体管阈值电压随体偏置而变化。在工作模式下,MOS管的体偏置为0,MOS管处于低阈值状态,翻转速度快。在等待模式下,MOS管的体偏置为反向偏置,处于高阈值状态,漏电小。

注意:MOS管的体偏转需要时间,电路有等待模式转为工作模式的时间较长。

3.2.2多电压设计(Multi-Voltage Domain)

对于多电压域设计,要在不同的电压域之间使用一些电平转换单元(Level Shifter),将输入电压范围转换成输出需要的不同电压范围。

如果不同电压与之间的驱动信号与接受信号之间的距离很长,需要插入特殊的驱动单元(Repenter)来增强信号的驱动能力;如果不同的电压域可以单独断电(MV with Power Gating),还要考虑添加保持寄存器(Retention Register)和电压隔离单元(Isolation Cell)。

3.3 门控时钟技术(clock gating)

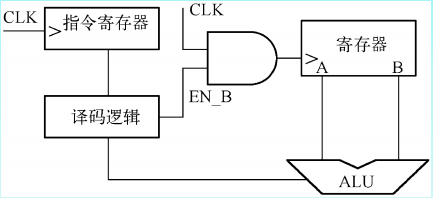

3.3.1预计算

预计算是指通过判断输入向量在满足一些特定条件时将输入释放或屏蔽。

上图所示为一个简单的停时钟电路的例子。在遇到不需要计算的指令的时候,译码逻辑单元就会使输出EN_B信号为0,时钟将会被关闭,寄存器的值保持不变,ALU不需要进行无用的计算,因而减少了系统的功耗。

3.3.2门控时钟

门控时钟即用逻辑门电路控制模块时钟的停或开。

但是直接使用使能信号en与时钟信号进行相与操作会产生毛刺:

优化:使用锁存器停时钟

3.4 门级优化技术

3.4.1毛刺的消除

这里的毛刺是指由于电路中信号的传输延迟引起的不必要的翻转,下图为两个消除毛刺前后的电路示意图。由于信号A和信号B的传输延迟不同,信号C上将会产生毛刺,插入缓冲器后,信号C上面的毛刺被消除了。

3.4.2逻辑级优化

这里讨论门级优化,也就是基于网表的优化。基于网表的功耗优化是一种与工艺无关的优化。

- 调整门的大小

可以在那些非关键路径上使用一些比较小的门,这样可以减小输入电容,从而减小他们前驱的翻转电流,降低了电路的翻转功耗。也可以增大负载比较大的门,这样可以增加他们的输出斜率,减少短路电流,降低了电路的短路功耗。

- 引脚的重分配

可以使用负载电容低的引脚去连接快速翻转的一些信号。这样可以减少高翻转信号的负载电容,降低了系统的动态功耗。

- 重排序操作

电路中b信号是翻转率比较大的信号,在排序前的电路中,b的每次翻转要驱动4个门,在排序后的电路中,b的每次翻转只需要驱动2个门,显然有效地降低了系统的动态功耗。下图所示为排序前后的两个电路模块。

- 重新映射

对于电路中的信号a,重新映射之前要驱动两级的与非门,在重新映射之后,只需要驱动一级优化的逻辑门AOI,显然降低了系统的动态功耗。下图所示为重新映射前后的两个电路模块。

3.4.3 物理级优化

物理级优化主要通过减少翻转和减少负载电容来降低系统的功耗。

物理级优化主要有以下几种方法:

- 使用低功耗的库

- 设计低功耗的布局规划

- 基于功耗优化的布局规划

- 通过布局布线来减少毛刺

- 在优化布局的时候调整缓冲器和连线的大小

- 调整晶体管的大小减少负载电容

3.4.4 控制输入向量

系统在睡眠状态下,控制输入向量可以明显减少系统的漏电流(选择最小漏电流的向量作为组合逻辑的输入)。

四、低功耗设计趋势

- 静态功耗优化

在编译时充分考虑指令的功耗特性,合理配置数据段和指令段在内存中的位置,并调整寄存器的分配;提高算法的执行效率;合理实现任务调度,减少由于频繁的上下文切换所造成的功耗。

- 动态功耗优化

操作系统支持下的动态功耗管理和动态电压频率缩放前者是指将处于空闲状态或非满负荷运转状态的系统单元有选择的关闭或减慢运行速度。这主要有几种方式:基于超时(Timeout-based)的关闭策略、基于预测的关闭策略和基于Markov链的随机动态功耗管理策略。

更多内容,请查阅《SoC设计方法与实现》。

想白嫖可留邮箱。