竞争与冒险:

所谓竞争与冒险,就是在组合电路中,信号经不同途径传输后,达到电路中某一汇合点的时间有先有后,这种现象成为竞争。由于竞争而使电路输出发生瞬间错误的现象,称为冒险。

在时序逻辑电路中,产生次态的电路和输出电路是组合逻辑电路。组合逻辑电路存在竞争与冒险,可能导致时序系统进入不正确的状态。

使用同步时序逻辑电路可以克服次态逻辑存在竞争与冒险的问题。

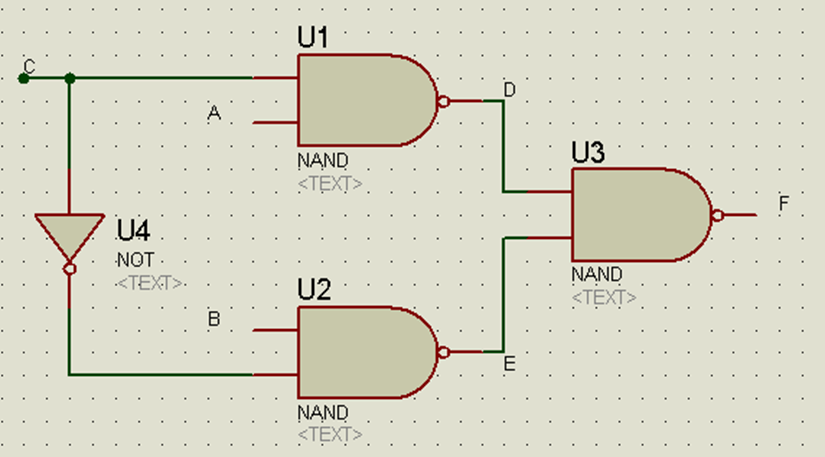

竞争与冒险的例子:

由于延迟时间的存在,当信号C经过多条路径传送后又重新会合到U3上,由于C-D路径上门的级数与C-E路径不同,导致到达会合点U3的时间有先有后,从而产生瞬间的错误输出。

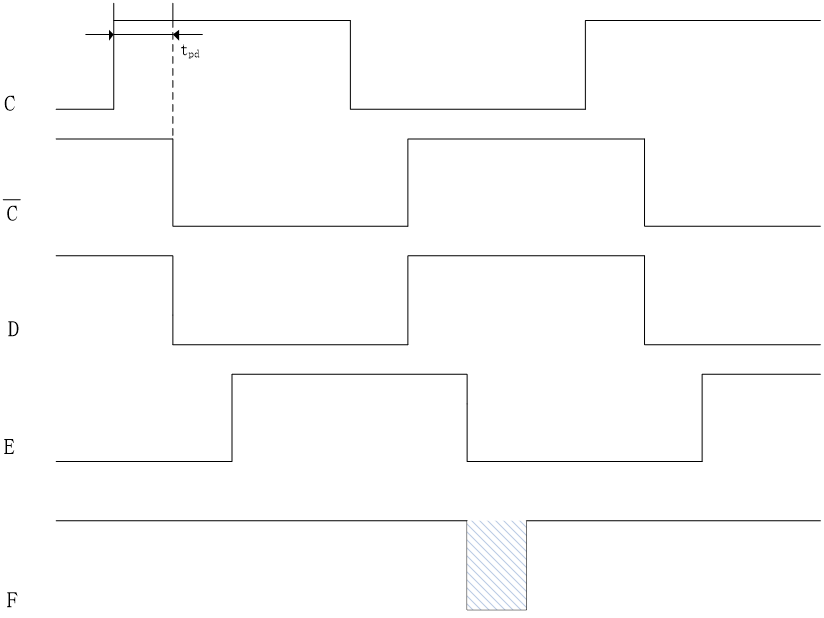

上例中的时序如图:

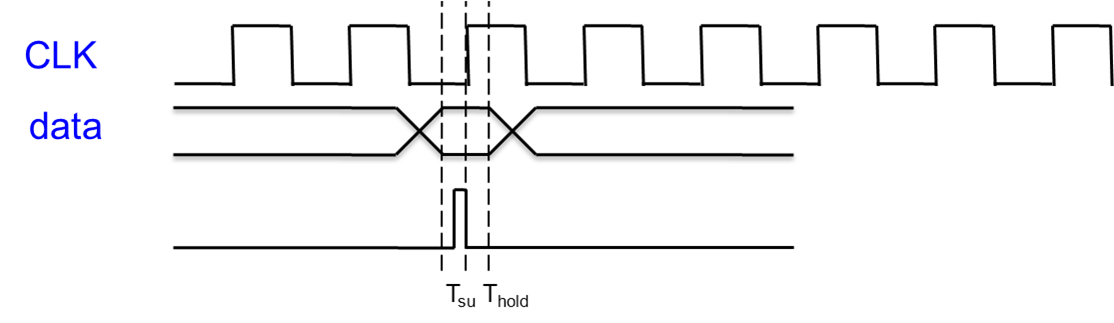

状态机克服竞争冒险的方法:

在次态产生组合逻辑电路中,可以通过时序逻辑消除毛刺,从而克服竞争冒险。

通过输出端时序同步的方法消除竞争与冒险(即使用同步时序逻辑电路设计方法。详细实例见后面介绍)。