之前混着参加了很多次面试,几乎每次面试我都会问,你怎么理解AXI的Outstanding能力嘛?乱七八糟的回答都有,几乎没有准确回答的。这个Outstanding能力在SOC设计中应该是一个非常常见的性能指标呀,很多IP的配置都会牵涉到,比如PCIe,DMA

什么是Outstanding?

什么是Outstanding?

如果你想知道什么是Outstanding的话

那我就带你研究

大家都知道AXI是ARM AMBA协议家族的一员,AXI的很多特性,例如分离的读写通道、Burst传输,Interleaving、乱序返回等特,显著提升了SOC互连的性能。其中,Oustanding能力就是一个非常重要的参数。

对AXI而言,因为读写分离,所以Outstanding能力分为读Outstanding和写Outstanding。

如何理解Outstanding呢?

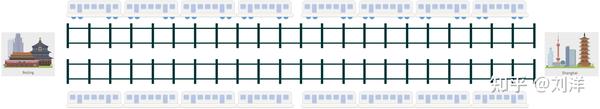

我们可以想象SOC的互连犹如中国高铁网络,那么

- 八纵八横的铁轨就是SOC的总线,有京沪高铁,有武广高铁,错综复杂

- 总线上的数据传输就是一列列的高铁班车

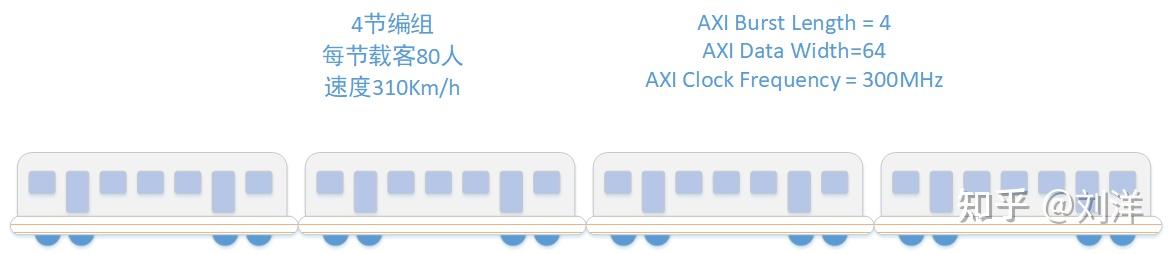

- Burst传输的长度就是一列高铁的节数,有的高铁是8节,就是Burst Length=8,有的高铁是16节,就是Burst Length=18

- 1节高铁带的人数就是AXI的数据位宽,有的高铁1节载人80个,有的高铁一节载人可能160个(假设哈),就好比有的AXI 数据位宽为64bit,有的AXI数据位宽为128bit

- 高铁的速度就是AXI的总线的时钟频率,有的高铁速度为310Km/h,比如京沪高铁;有的高铁线路标准比较差,那就只能跑250Km/h,比如合宁城际。这就好比AXI的频率有的是200MHz,有的是300MHz

- 从高铁站出发,到终点的线路长度就是AXI的总线延迟。京沪高铁全长1318 KM,那么这个线路长度就固定死了,就好比SOC的AXI Interconnect网络设计好了后,那么AXI的Master到Slave的延迟的拍数(Clock Cycle)也就固定了。所以一节高铁可以等效为AXI的一个Cycle

好,我们一一对应上之后,我们以上海到北京的高铁为例,假设全上海的人都要坐高铁去北京,为了达到最高效率,那就是上海到北京的铁轨上高铁首尾相接,从上海虹桥排到北京南站,这些首位相接的高铁还都以310Km/h的速度前进(这里我们不考虑高铁停在北京南站下客减速的时间哈)。高铁到北京南站后,立即以相同速度折返回到上海虹桥,回到上海虹桥的高铁又继续满客开往北京南站。我们都使用16节编组的高铁的话,那么问题来了,我们至少需要运行多少列高铁才能达到京沪高铁的最大效率呢?

简单计算,我们需要X列高铁,

- X=高铁线路总长度*2/ 16节高铁长度

经过变换

- X=(高铁线路总长度/1节高铁长度)*2/16

由于一节高铁可以等效为AXI的一个Cycle,所以(高铁线路总长度/1节高铁长度)就是该线路的延迟Cycle数目

故

- X=线路延迟Cycle数目*2/16

这里X就是AXI Outstanding的概念,而“线路延迟Cycle数目*2”就是往返总延迟,也就是Round Trip Latency。

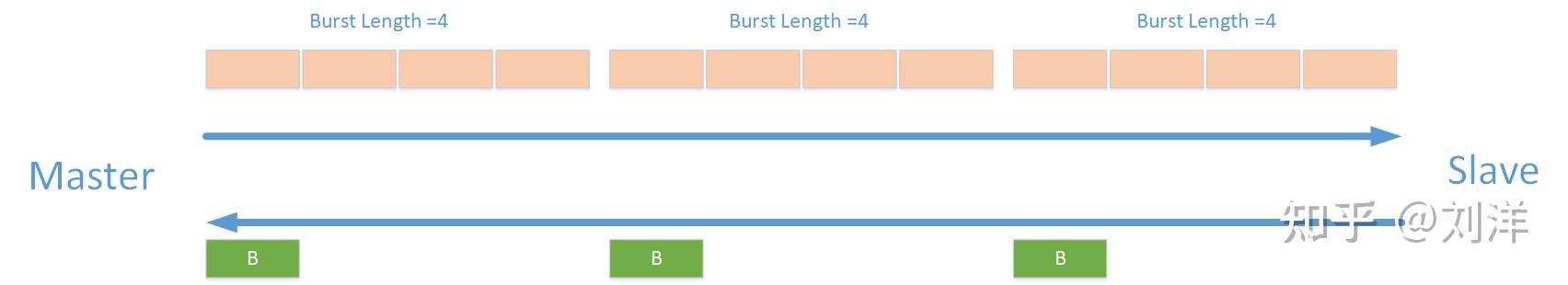

这时,让我们回到AXI协议,以AXI写为例,AXI Master每次发写命令(包括AW和W),都需要Slave返回Response(B通道),犹如上面高铁的例子里面,上海虹桥(Master)发出的列车,只有到达北京南站(Slave)下客后(处理后),北京南站才能将该列车折返返回上海虹桥(Response)。

Outstanding的能力即AXI Master不需要等到Response,就可以持续发写命令的个数。

那AXI Master 的Outstanding能力越大越好吗?

也不是,因为当高铁的轨道上头尾相连堆满高铁的时候,即使有再多的高铁也没法放进轨道了。

那AXI Master的Outstanding能力如何才能设置得到合理值呢?

和高铁列数的计算类似,我们首先需要确定AXI Master 在需要的场景

- AXI Burst Length 是多大,也就是高铁是8节编组还是16节编组。

- 期待的带宽 (Expected Bandwidth)要能达到多少。这里最大带宽是AXI Clock Frequency x AXI Data Width,也有可能根据实际应用需求低于这个值。我们就按照最大值计算。

- AXI的Round Trip Latency是多少个Cycle,或者多少nanosecond

所以最佳Outstanding能力(Best Outstanding)计算公式如下Best Outstanding =Round Trip Latency(cycle) \div AXI Burst Length