HDLBits: 在线学习 SystemVerilog(二十四)-Problem 163-177(TestBench)

HDLBits 是一组小型电路设计习题集,使用 Verilog/SystemVerilog 硬件描述语言 (HDL) 练习数字硬件设计~

网址如下:

https://hdlbits.01xz.net/

关于HDLBits的Verilog实现可以查看下面专栏:

https://www.zhihu.com/column/c_1131528588117385216

缩略词索引:

SV:SystemVerilog

从今天开始新的一章-时序电路,包括触发器、计数器、移位寄存器、状态机等。

今天的题目163-172主要是根据仿真图还原逻辑,题目没什么好说的,直接到下面链接看源码吧~

https://github.com/suisuisi/SystemVerilog/tree/main/SystemVerilogHDLBits

剩下的几道题是自己写testbench,也比较简单,就简单说一下。

Problem 163-circuit1

Problem 164-circuit2

Problem 165-circuit3

Problem 166-circuit4

Problem 167-circuit5

Problem 168-circuit6

Problem 169-circuit7

Problem 170-circuit8

Problem 171-circuit9

Problem 172-circuit10

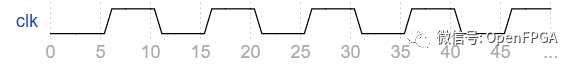

Problem 173-Clock

题目说明

编写一个创建模块dut实例(具有任何实例名称)的测试平台,并创建一个时钟信号来驱动模块的clk输入。时钟周期为 10 ps。时钟应初始化为零,其第一个转换为 0 到 1。

模块端口声明

module top_module ( );题目解析

生成clock有很多种方式,常见的就是forever和always。

timeunit 1ps ;

timeprecision 1ps ;

module top_module ( );

logic clk ;

dut u1_dut(

.clk(clk)

);

initial begin

clk <= 1'b0 ;

end

always #5 clk <= ~clk ;

endmodule

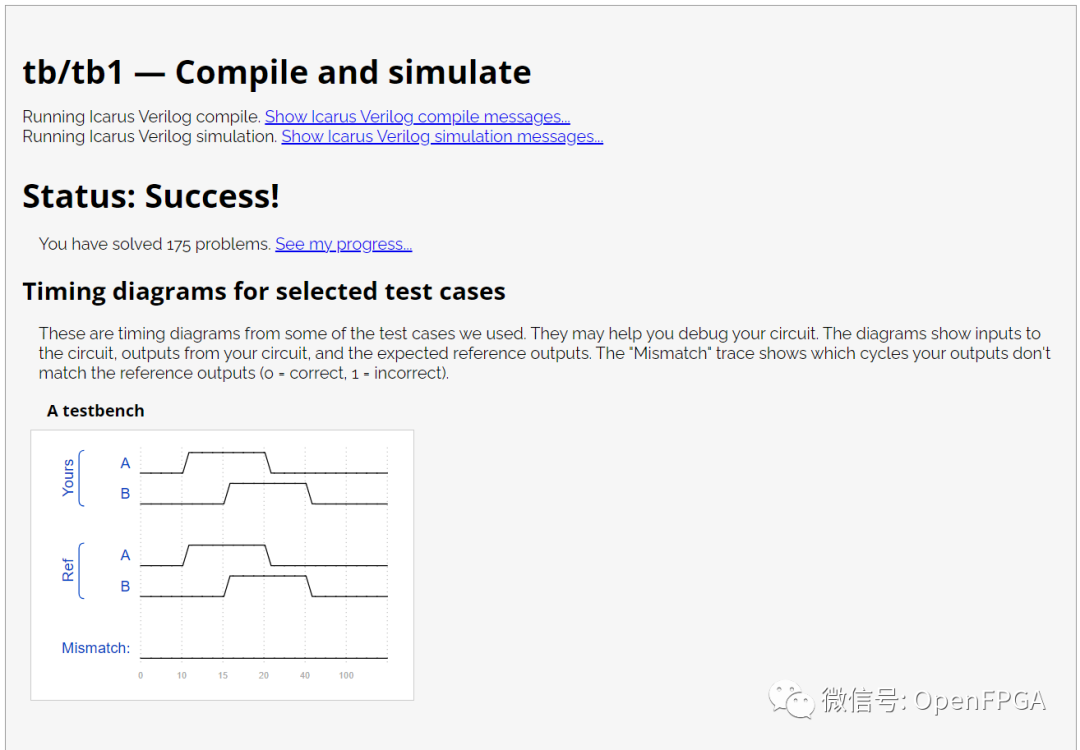

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

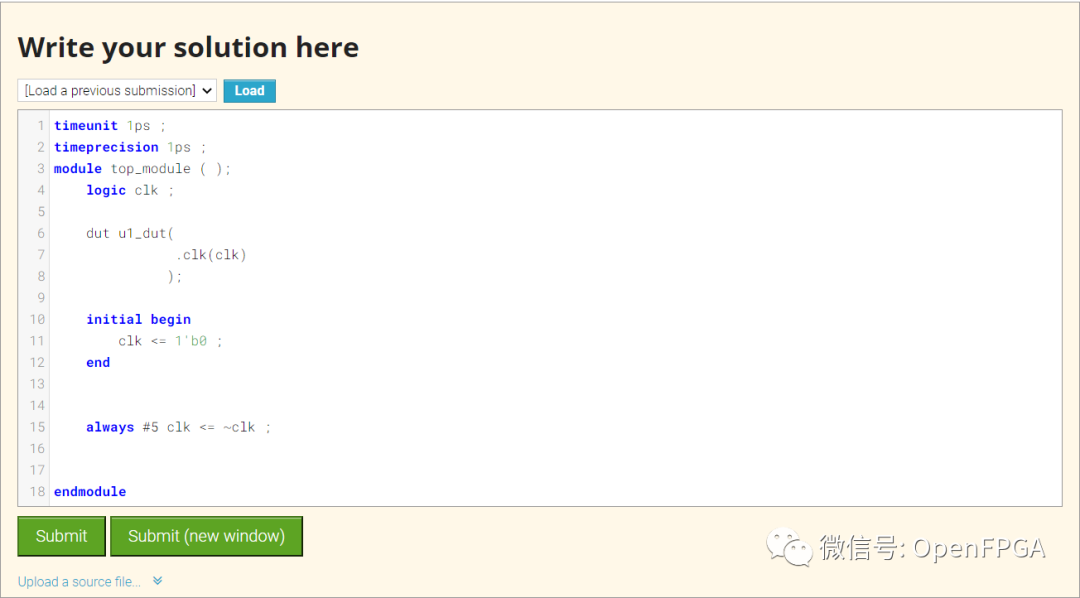

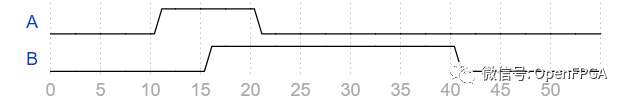

Problem 174-tb1

题目说明

创建一个 Verilog 测试台,它将为输出 A 和 B 生成以下波形

模块端口声明

module top_module ( output reg A, output reg B );题目解析

initial+# n即可。

timeunit 1ps ;

timeprecision 1ps ;

module top_module ( output logic A,

output logic B );//

// generate input patterns here

initial begin

A <=1'b0 ;

B <=1'b0 ;

#10 ;

A <= 1'b1 ;

B <= 1'b0 ;

#5 ;

A <= 1'b1 ;

B <= 1'b1 ;

#5 ;

A <= 1'b0 ;

B <= 1'b1 ;

#20 ;

A <= 1'b0 ;

B <= 1'b0 ;

end

endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

Problem 175-and

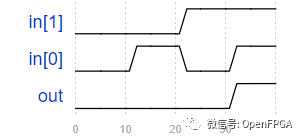

题目说明

给给定的与门写测试文件,波形参考下图。

模块端口声明

module top_module();题目解析

和上一题类似。

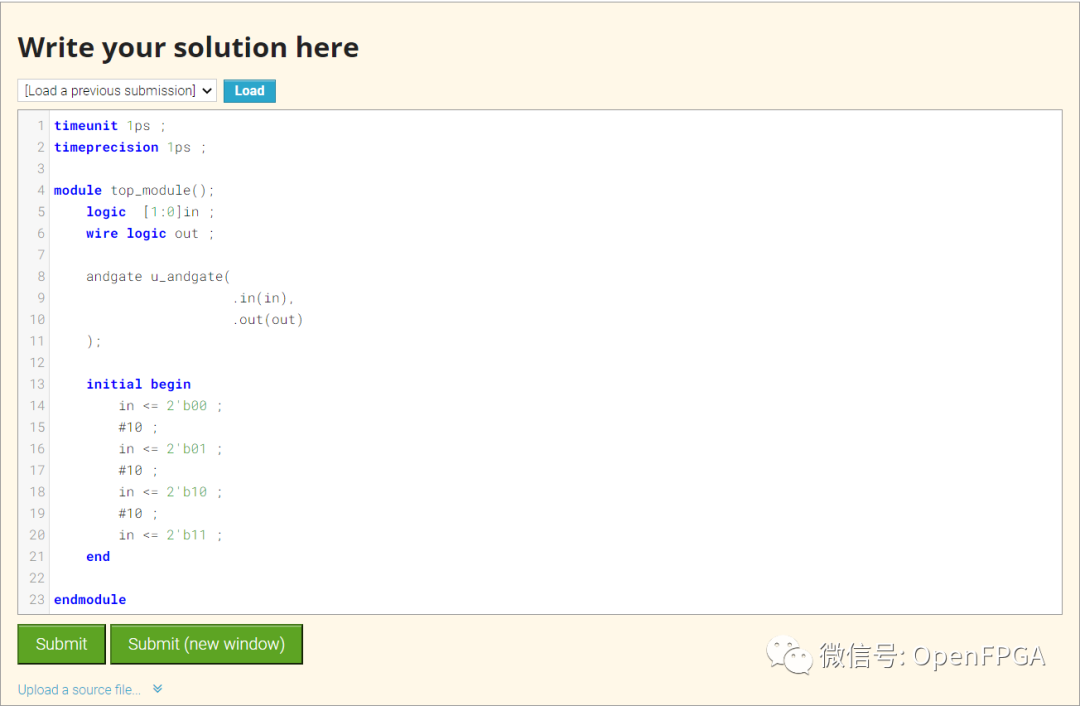

timeunit 1ps ;

timeprecision 1ps ;

module top_module();

logic [1:0]in ;

wire logic out ;

andgate u_andgate(

.in(in),

.out(out)

);

initial begin

in <= 2'b00 ;

#10 ;

in <= 2'b01 ;

#10 ;

in <= 2'b10 ;

#10 ;

in <= 2'b11 ;

end

endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

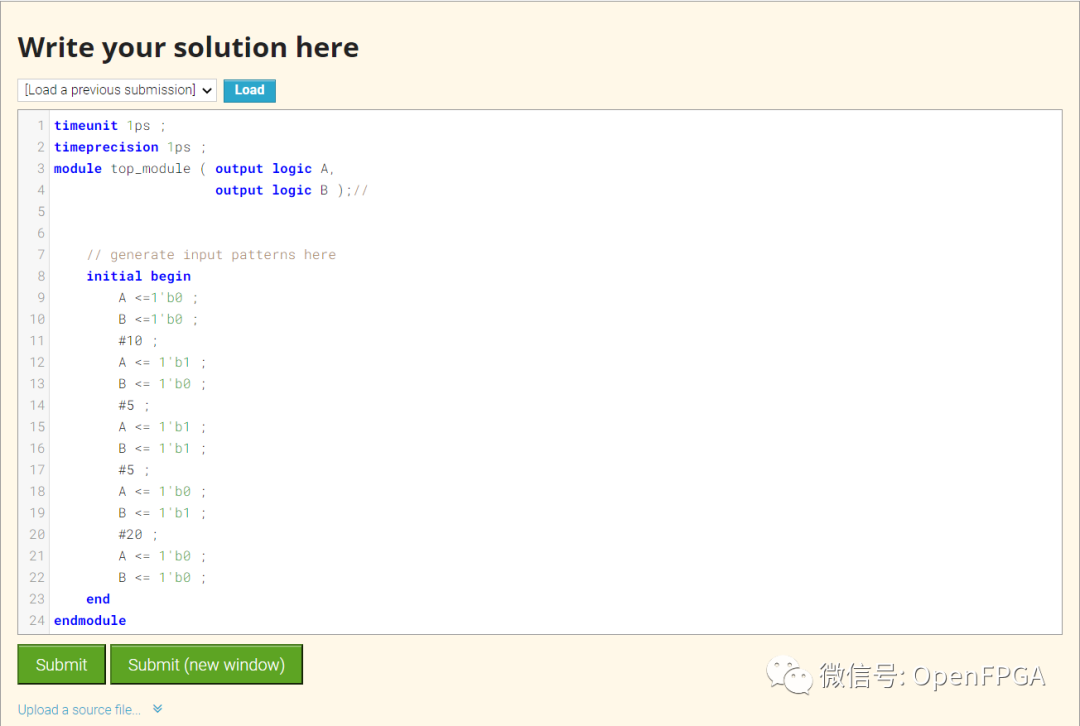

Problem 176-tb2

题目说明

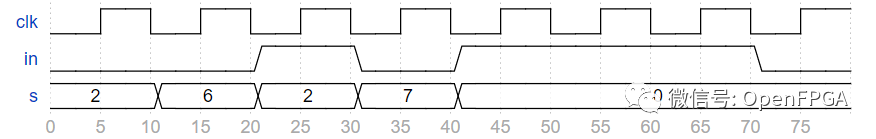

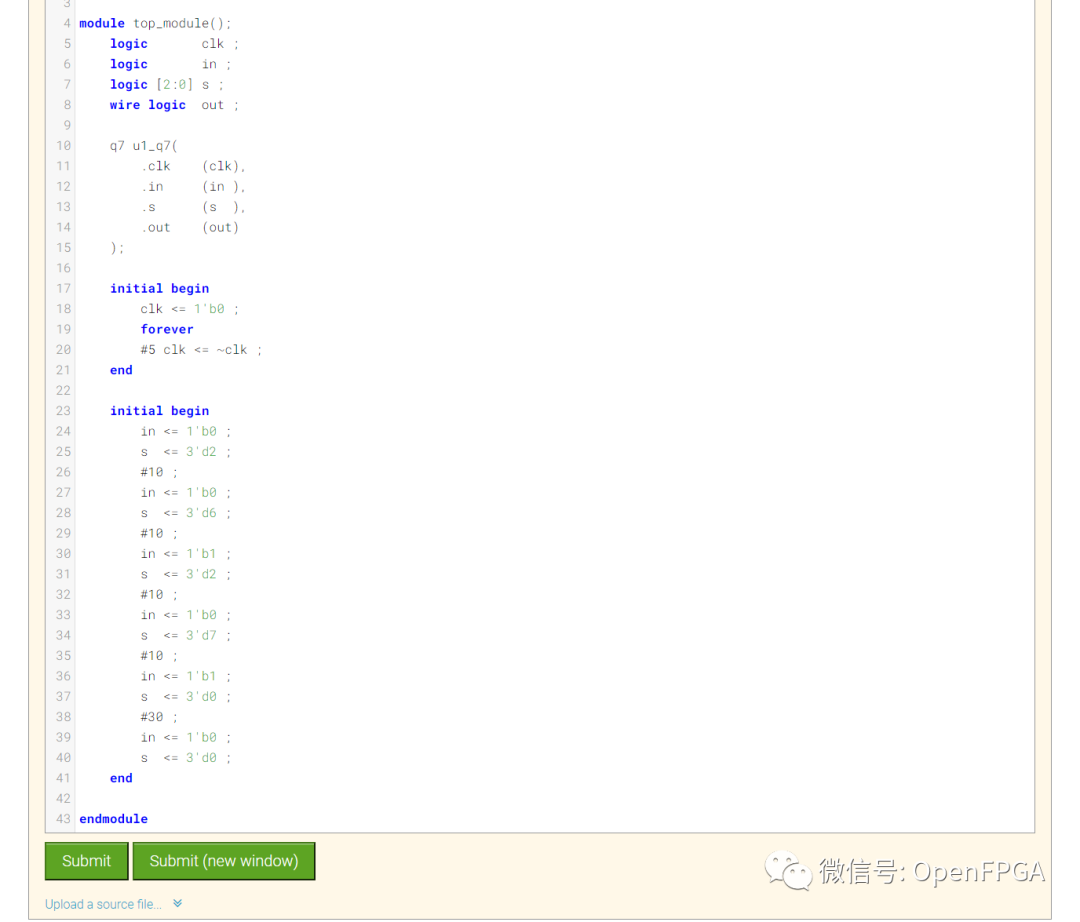

给定一个q7电路,按照下图编写testbench:

图片来自HDLBits

图片来自HDLBits

模块端口声明

module top_module();题目解析

timeunit 1ps ;

timeprecision 1ps ;

module top_module();

logic clk ;

logic in ;

logic [2:0] s ;

wire logic out ;

q7 u1_q7(

.clk (clk),

.in (in ),

.s (s ),

.out (out)

);

initial begin

clk <= 1'b0 ;

forever

#5 clk <= ~clk ;

end

initial begin

in <= 1'b0 ;

s <= 3'd2 ;

#10 ;

in <= 1'b0 ;

s <= 3'd6 ;

#10 ;

in <= 1'b1 ;

s <= 3'd2 ;

#10 ;

in <= 1'b0 ;

s <= 3'd7 ;

#10 ;

in <= 1'b1 ;

s <= 3'd0 ;

#30 ;

in <= 1'b0 ;

s <= 3'd0 ;

end

endmodule

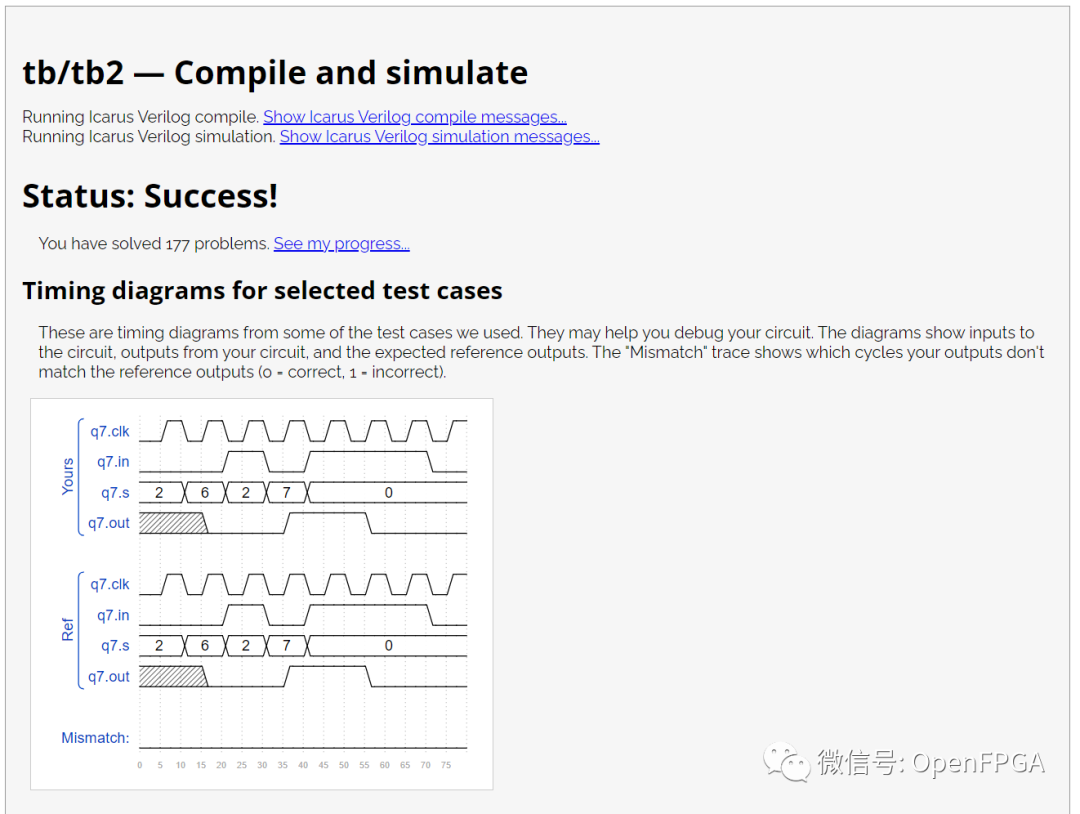

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

Problem 177-tff

题目说明

给题目中给定的tff编写测试文件。

模块端口声明

module top_module ();题目解析

timeunit 1ps ;

timeprecision 1ps ;

module top_module ();

logic clk ;

logic reset ;

logic t ;

wire logic q ;

tff u_tff(

.clk (clk ),

.reset (reset),

.t (t ),

.q (q )

);

initial begin

clk <= 1'b0 ;

forever

#5

clk <= ~clk ;

end

initial begin

reset <= 1'b0 ;

t <= 1'b0 ;

#3;

reset <= 1'b1 ;

t <= 1'b1 ;

#10;

reset <= 1'b0 ;

t <= 1'b1 ;

end

endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

总结

今天的几道题就结束了,难度不大,但是是基本~

最后我这边做题的代码也是个人理解使用,有错误欢迎大家批评指正,祝大家学习愉快~

代码链接:

https://github.com/suisuisi/SystemVerilog/tree/main/SystemVerilogHDLBits