本文是针对 rk3566 / rk3568 LCD dtsi文件配置选项的含义进行学习。

1、power-supply = <&vcc3v3_lcd0_n>;

配置LCD供电源,指向电源的dts配置节点。

2、LCD控制引脚

reset-gpios = <&gpio3 RK_PD1 GPIO_ACTIVE_LOW>;

enable-gpios = <&gpio0 RK_PD5 GPIO_ACTIVE_HIGH>;

backlight = <&backlight>;//指向背光的dts配置节点

分别为LCD复位引脚、LCD使能引脚、背光控制。该选项配置需要结合实际硬件。

格式说明:<gpio_group gpio_pin 有效电平值>

3、LCD的时延

reset-delay-ms = <60>;//配置reset的脉冲时延

enable-delay-ms = <60>;//配置panel显示前的延时值

prepare-delay-ms = <60>;//配置panel接收图像数据前的延时值

unprepare-delay-ms = <60>;//配置panel黑屏前的延时值

disable-delay-ms = <60>;//配置panel关闭前的延时值

init-delay-ms = <60>;//配置panel在初始化前的延时值

各阶段的不同时延,具体含义需要结合实际代码理解。相应的值以屏规格书/屏时序为依据。

4、dsi配置

dsi,flags = <(MIPI_DSI_MODE_VIDEO | MIPI_DSI_MODE_VIDEO_BURST | MIPI_DSI_MODE_LPM | MIPI_DSI_MODE_EOT_PACKET)>;//配置panel的使用的模式

dsi,format = <MIPI_DSI_FMT_RGB888>;//配置panel像素格式

dsi,lanes = <4>; //MIPI数据传输需要使用的lane数量

5、上下电初始化序列

panel-init-sequence = [

39 00 04 B9 F1 12 83

39 00 04 B2 C8 12 30

39 00 0B B3 10 10 28 28 03 FF 00 00 00 00

...

39 00 02 51 8F

39 00 02 53 24

39 00 02 C7 B8

39 00 03 C8 10 01

13 FA 02 11 00

13 32 02 29 00

];

panel-exit-sequence = [

05 32 01 28

05 FA 01 10

];

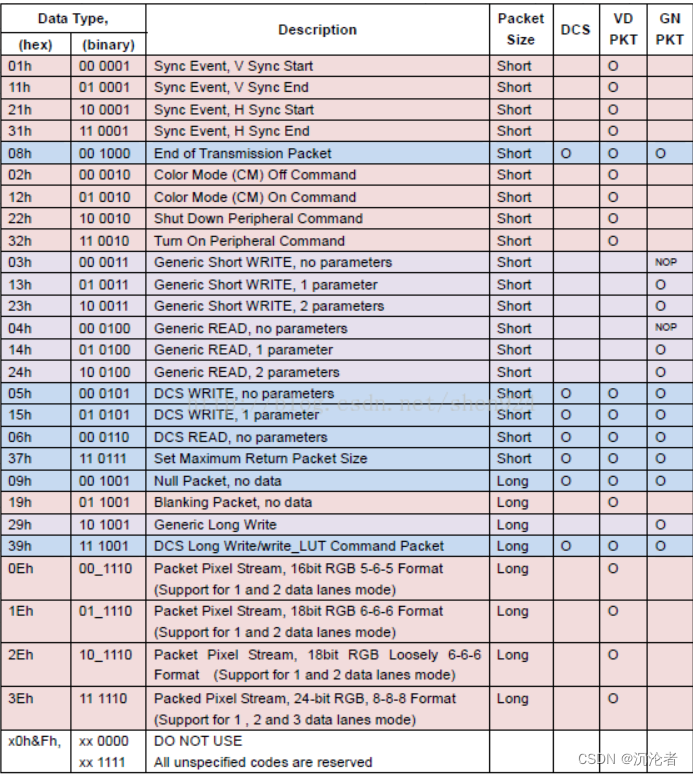

格式说明:

byte 0: dcs data type

byte 1: wait number of specified ms after dcs command transmitted

byte 2: packet payload length

byte 3 and beyond: number byte of payload

数据类型如下:

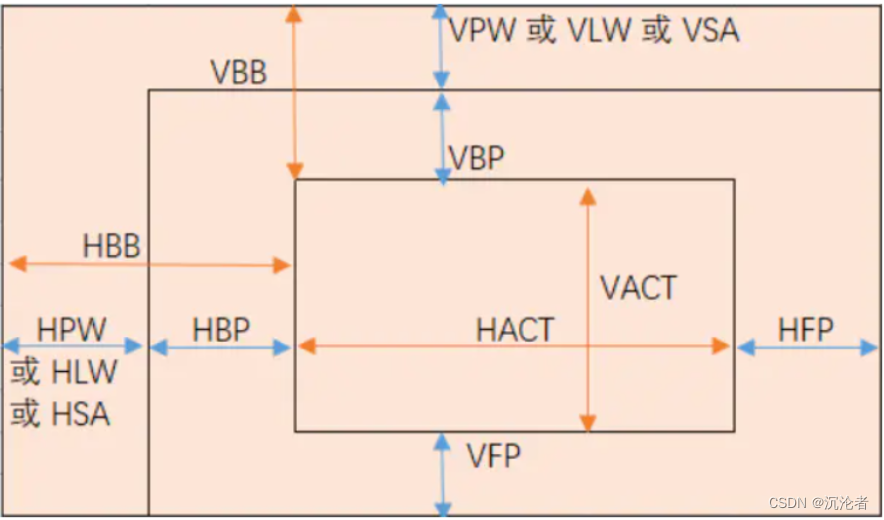

6、LCD时序、面板参数

display-timings {

native-mode = <&dsi0_timing0>; //显示器的当地模式,当存在多种模式下提供

dsi0_timing0: timing0 {

clock-frequency = <66276000>; //配置显示时钟,DCLK频率,单位HZ

hactive = <720>; //水平分辨率

vactive = <1280>; //垂直分辨率

hfront-porch = <50>; //水平前沿,以像素为单位

hsync-len = <20>; //水平脉冲宽度,以像素为单位

hback-porch = <50>; //水平后沿,以像素为单位

vfront-porch = <15>; //垂直前沿,以像素为单位

vsync-len = <5>; //垂直脉冲宽度,以像素为单位

vback-porch = <15>; //垂直后沿,以像素为单位

hsync-active = <0>; //hync、vsync、DEN、dclk 的极性控制。置 1 将对极性进行翻转

//配置hsync pluse(垂直同步脉冲)的有效电平是高/低/忽略

vsync-active = <0>;

//配置vsync pluse(垂直同步脉冲)的有效电平是高/低/忽略

de-active = <0>;

//配置data-enable脉冲的有效电平是高/低/忽略

pixelclk-active = <1>;

//数据采样的方式,该参数控制有效的pixel data数据在rising edge还是falling edge显示

//1:上升沿驱动像素数据/下降沿采样数据

//0:下降沿驱动像素数据/上升沿采样数据

//忽略

};

};

时序图如下:

7、ports端点配置

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

panel2_in_dsi: endpoint {

remote-endpoint = <&dsi_out_panel2>;

};

};

};

一个端口可以配置为与同一总线上的多个远程设备一起工作,则必须为每个端口提供一个“endpoint”子节点。

两个“endpoint” 节点通过它们的“remote-endpoint’”相互链接。设备的端点子节点包含配置此设备所需的所有属性,以便与其他设备进行数据交换。

8、其他

width-mm //配置panel的物理宽度尺寸[mm]

height-mm //配置panel的物理高度尺寸[mm]

power-invert //配置电源反转

bpc //配置像素点位深

swap-rb、swap-rg、swap-gb //置 1 将对对应的颜色进行翻转。

clocks //mipi的clock,与clock-names 一一对应。

clock-names //设置clock的名称

9、mipi LCD 的CLK时钟频率与显示分辨率及帧率的关系

Mipiclock = [ (width+hsync+hfp+hbp) x (height+vsync+vfp+vbp) ] x(bus_width) x fps/ (lane_num)/2

即mipi 屏的传输时钟频率(CLKN,CLKP)等于(屏幕分辨率宽width+hsync+hfp+hbp)x ( 屏幕分辨率高height+vsync+vfp+vbp) x(RGB显示数据宽度) x 帧率/ (lane_num)/2

公式说明:

一帧画面需要的数据量为(单位bit):FRAME_BIT = (屏幕有效显示宽度+hsync+hfp+hbp) x ( 屏幕有效显示高度+vsync+vfp+vbp) x(RGB显示数据宽度24)。

一秒钟内需要传输的数据量为(单位bps):FRAME_BIT x fps(帧率)

除以lane_num----因为mipi通讯协议中,一个CLOCK几个lane是可以同时传输数据的

除以2----因为根据mipi通讯协议,CLK_N、CLK_P这两根时钟线的上升沿/下降沿可以获取到数据。