一、什么是make

make是一个命令工具,是一个解释makefile中指令的命令工具。

二、为什么要学习make命令

举例子:我们平时在linux上使用的编译器gcc,现有5个.c文件( a.c b.c c.c d.c e.c)

编译指令: gcc a.c b.c c.c d.c e.c -o test

当我们进入工作时,需要编译很多.c文件,比如编译上百上千的文件,我们用上述方法,不好。

原因如下:

1、容易漏敲某个.c文件,导致编译失败,排查费时间

2、当我们没有漏敲,并且成功生成可执行文件。但我们需要修改某个文件,得重新编译每一个.c

3、工作时,我们很多写的代码都需要跨平台使用,比如写进ARM 需要使用 arm-linux-gcc指令

总结:编译麻烦——为了方便编译,因此我们需要学习make指令与用法

三、make很好解决了上述问题

(1)大量代码关系维护

大项中源代码比较多,手工维护、编译时间长而且编译命令复杂,难以记亿及维护。因此

把代码维护命今及编译命今写在makefile文件中,然后再用make工具解析此文件自动执行相应命令,可实现代码的合理编译。

(2)减少重复编译时间

在改动其中一个文件的时,能判断哪些文件被修改过,可以只对该文件进行重新新编,然后重新链所有的目标文件,节省编译时间

四、什么是Makefile

Makefile是一个文件,这个文件中描述了我们程序的编译规则——类似脚本

当我们执行make命令时,make命令就在当前目录下找Makefile文件,根据文件里面的执行规则,编译程序。

注意:Makefile规则文件是我们程序员根据自己的程序,编写的编译规则。

五、使用Makefile的好处

1、简化编译程序的时候输入命令,如上述的 gcc a.c b.c c.c d.c e.c -o test

直接 输入一个 make 即可完成编译

2、节省编译时间,提高编译效率

六、Makefile的语法规则

目标文件:依赖文件列表

<tab>编译命令 //<tab> 这是tab键

clear:

<tab>rm 目标文件 -rf //使用make clear 命令:删除生成的目标等文件

1、目标文件:

通常是我们最后编译得出可执行文件

2、依赖文件

是用来输入而产生的目标文件的文件

一个目标文件通常有几个依赖文件(也可以只有一个)

gcc 依赖文件 依赖文件 -o 目标文件 (多个依赖文件)

gcc 依赖文件 -o 目标文件 (一个依赖文件)

除此以外:目标文件的依赖文件,可为.c文件 也可为 .o文件

举个例子: 现有三个.c文件 一个头文件,分别为 : main.c a.c b.c head.h

(1)平时用的编译模式

(2)使用make指令,完成编译

第一步:在当前位置,创建一个Makefile文件

指令: vim Makefile

第二步:根据编译程序.c 文件指定编译规则

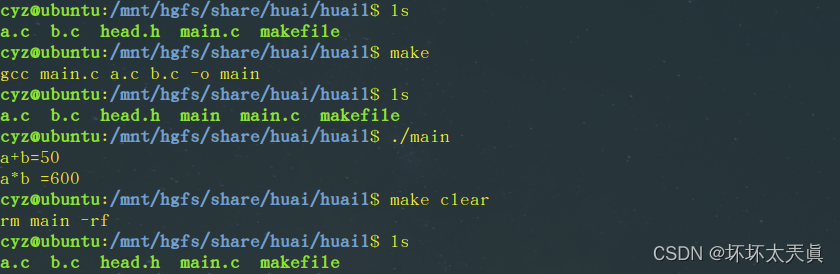

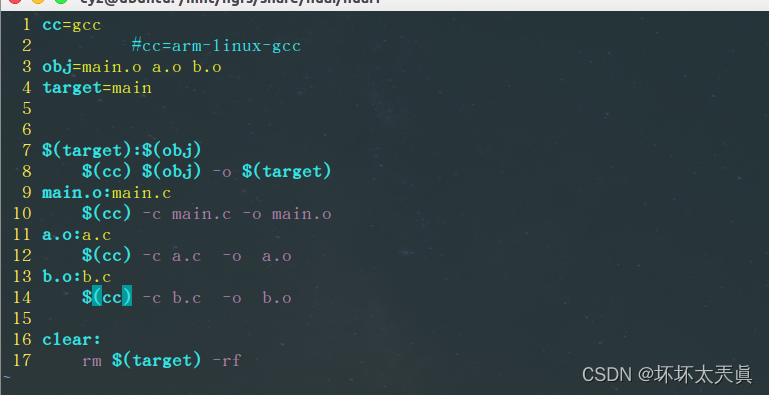

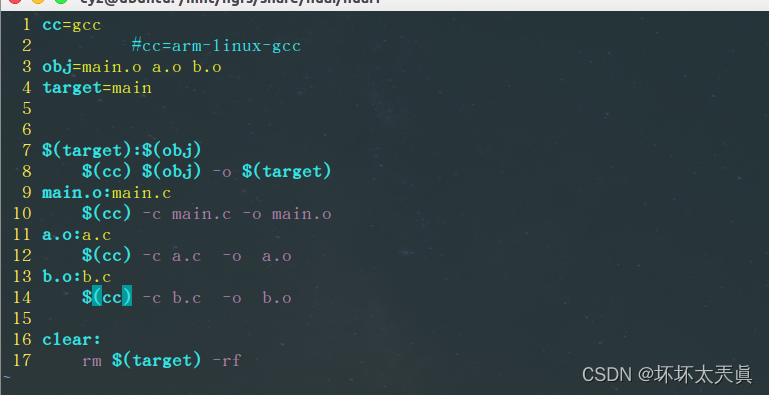

第一种编写(不常用且无法查看哪个文件被修改过,跨平台无法使用——编译会失败)

输入make命令并且执行文件

输出结果与删除操作演示

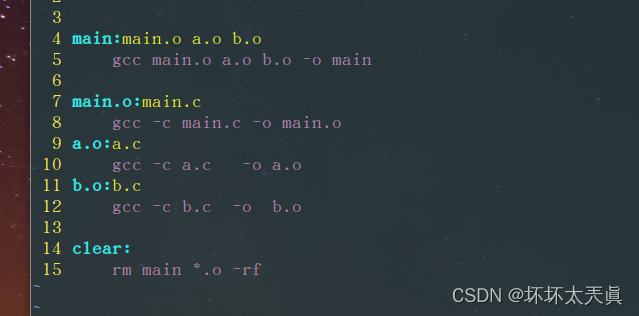

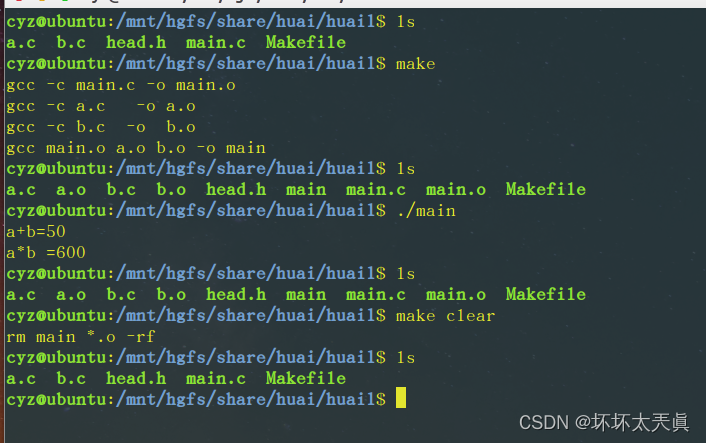

第二种编写(可查看哪个文件被修改,但跨平台无法使用——编译会失败)

输入make命令并且执行文件

输出结果与删除操作演示

第三种编写(即可查看文件修改,也可跨平台使用)基于第二种编写改编得到——不懂看第八节

七、make命令格式

前面所使用的都是单独 make ,难道不都全是使用单独 make ? 答案:不是的

简单来讲,单独使用 make 与创建的Makefile名称有关。

单独的 make 默认在工作目录下寻找名为 : GNUmakefile 、Makefile 、makefile文件作为makefile输入文件。

简单来讲,就是创建名为: GNUmakefile 、Makefile 、makefile 其中一个,

就可以 使用单独的 make 指令

如果创建的 不是 上面3种 的其中一种,必须使用 make -f 文件名

比如:创建一个 Makefile1 (此 Makefile1 不是 上面的三种)

就不能使用单独 make指令 而是使用 make -f Makefile1

八、Makefile的自定义变量(学会了此节,你已经基本掌握了)

定义变量:

变量名=变量值

引用变量:

$(变量名) 或者 ${变量名}

makefile的变量名:可以用数字开头。

8.1举例子:如下图(此举的例子是第一种编写方式)

变为如下图

解析:$(cc) 就是gcc 但此$(cc)是可以跨平台编译

$(obj) 就是 main.c a.c b.c

同理: $(target) 就是 main

总之就是换个名字,跟原图的意思是一样的。

为什么要这样,方便,快捷,

当我们有上千个.c文件的时候,直接可以把上千个.c文件,用一个名字代替,引用它 $(名字)

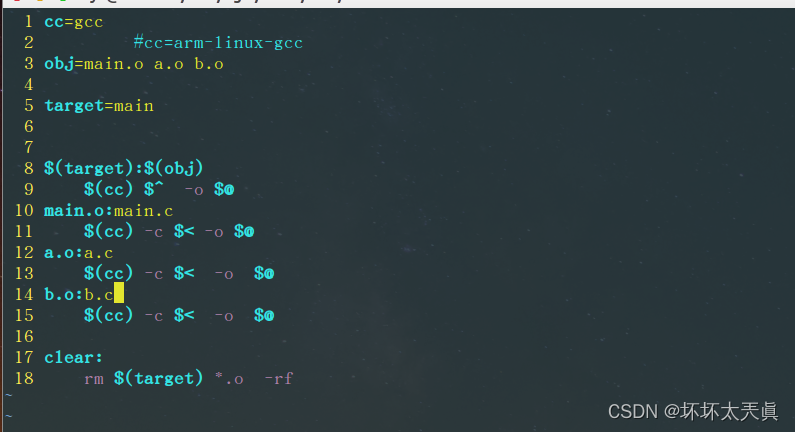

8.2举例子:如下图(此举的例子是第二种编写方式)

突然发现,当我们.c文件存在上百的时候,用此方法写的代码也很多,因此,看第九节,如何写更简便的代码。

九、预定义变量

makefile中有许多预定义变量,这些变量具有特殊的含义,可在makefile中直接使用。

常用的有:

$@ 目标名 (即 “ :” 左边的就是目标名)如 main:main.c (main为目标名)

$< 依赖文件列表的第一个文件 如; main:main.c a.c b.c ($< 即为红色字体第一个 main.c)

$ ^ 所有的依赖文件 如; main:main.c a.c b.c ($^ 即为红色字体)

CC C编译器的名称,默认值为cc

CFLAGS C编译器的选项

完善规则如下图

学会,双击点个赞 !!!