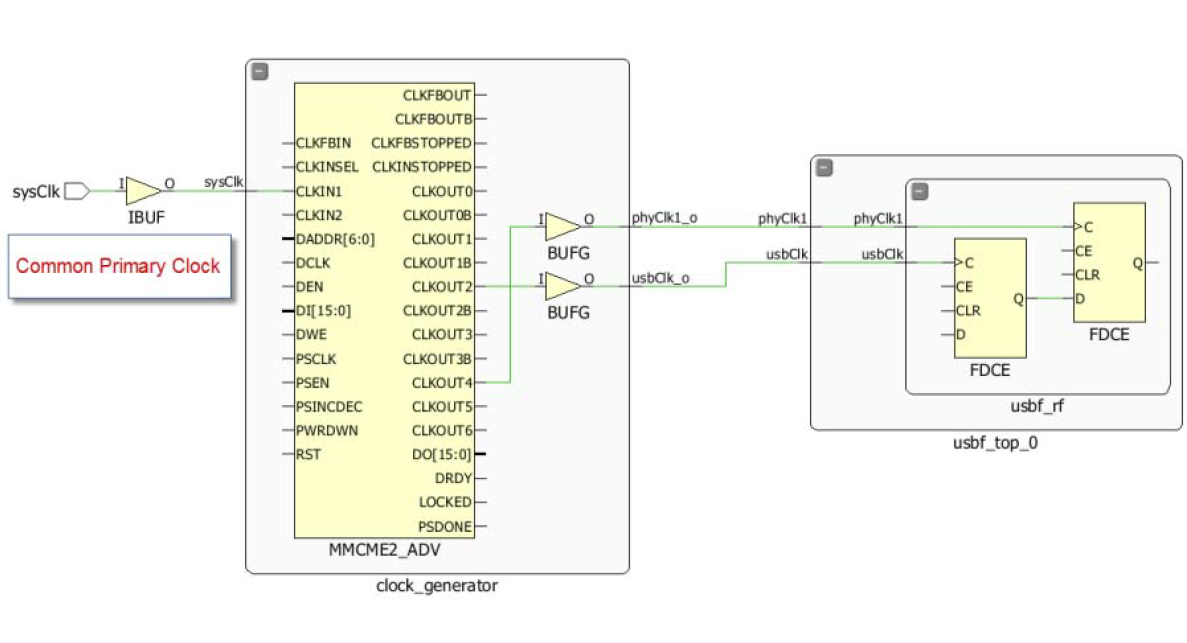

图1 安全的CDC路径

安全的CDC路径是指源时钟和目标时钟有相同的来源,在FPGA内部共享部分时钟网络的时序路径。具体来说就是系统时钟sys_clk经过IBUF后进入MMCM原语块经过倍频、分频处理输出多个目标时钟,目标时钟BUFG增强驱动能力后输入到用户模块或IP核内部使用。

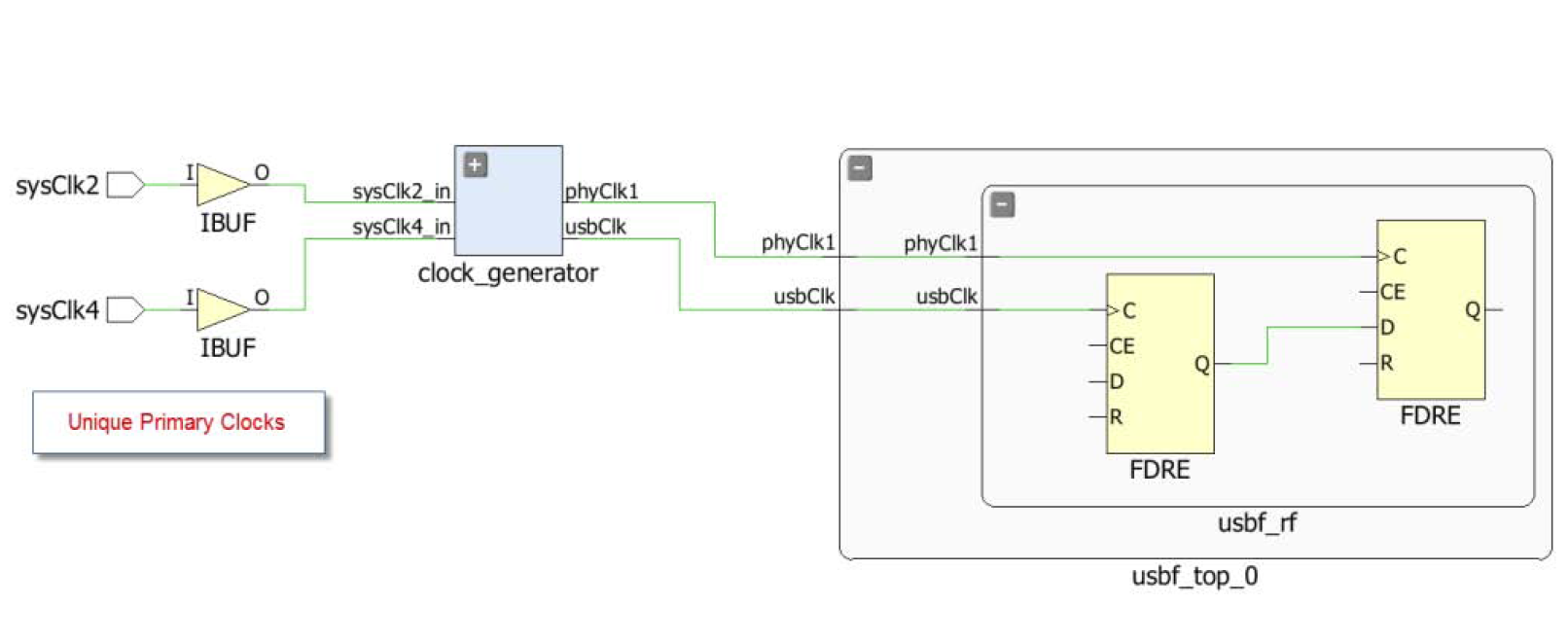

图2 不安全的CDC路径

不安全的CDC路径是指源时钟和目标时钟不同,且有不同的端口进入FPGA,在芯片内部不共享时钟网络。具体来说,就是多个系统时钟源经过倍频后产生不同模块使用的时钟,再拉进相应的用户模块使用。

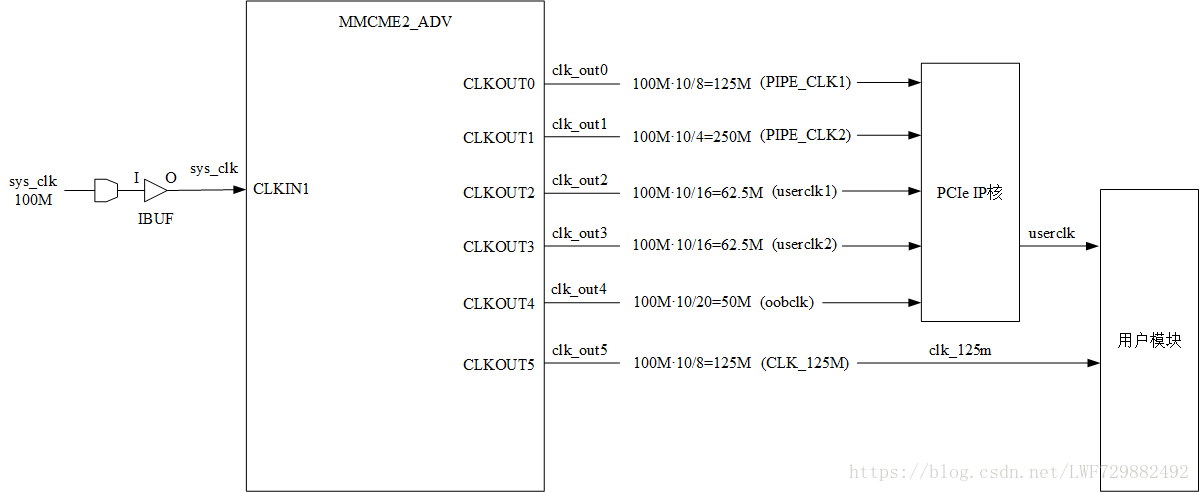

下面我就单独看PCIe的时钟模块,发现其CDC路径和图1是一样的,PCIe时钟模块见下图3:

系统时钟sys_clk过IBUF后进入MMCM原语块,经过倍频、分配处理输出6种时钟:第0路和第1路时钟分别为125M和250M,用于PCIe IP核底层,PHY有一个PCLK时钟输出线,用来同步MAC/PHY接口(见下图4)的数据传输,当数据位宽为16bit时PCLK为125M,当数据位宽是8bit时PCLK为250M;第2路和第3路输出的是一样的时钟频率62.5M,将CLKOUT3输出的clk_out3进入IP核转了一圈,再输出给用户模块,用于PCIe总线控制器的逻辑处理时钟;第4路时钟是oobclk,模块未用到,接入IP核;第5路时钟是125M的用户模块存储读/写时钟,主要用在上行、下行FIFO的读写时钟上,62.5M*64bit=125M*32bit。

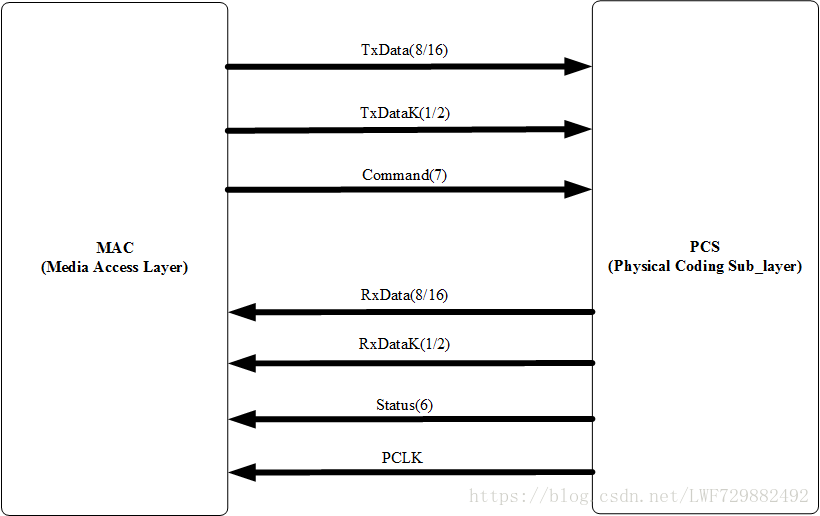

图4 PHY/MAC接口图

后续有内容再补充!

参考Reference:

1." VIVADO 使用误区与进阶":https://wenku.baidu.com/view/450aa92ddd3383c4bb4cd2e9.html

2.“细看PCIe接口PIPE规范”:https://wenku.baidu.com/view/d6d281b3b9d528ea81c779d5.html

3.“DWC PCIE学习笔记(一) PCIE PHY接口”:https://blog.csdn.net/bcs_01/article/details/65626801

/*End for Ver. 1.0 2018-6-6 11:42:35*/