关于最常用的跨时钟域处理方法,前人总结一大堆,诸如双寄存处理、fifo、握手协议等,几近完善,在此不予赘述。

此外,更有xilinx官方时序设计指导文档UG906,读者可自行阅读分析。在此,给出一个例子,介绍本人进行的跨时域处理的方式。

此次的例子是一个hdmi显示测试的例子。将手动生成的彩条像素数据通过hdmi发送,连接显示器的hdmi接口进行显示测试。

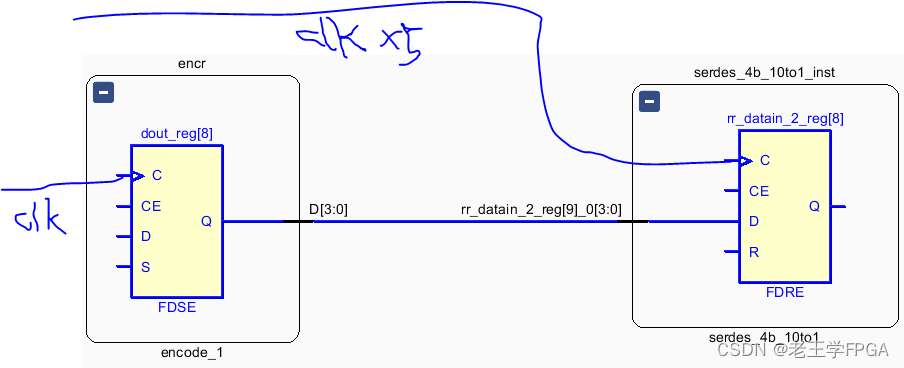

设计的核心部分是编码模块和串行发送模块。dout[9:0]是由pixelclk时钟驱动的编码数据,这些数据被串行发送模块以5倍于pixelclk速度的时钟(clkx5)采样接收。这样就涉及到两个时钟的跨时钟域问题。

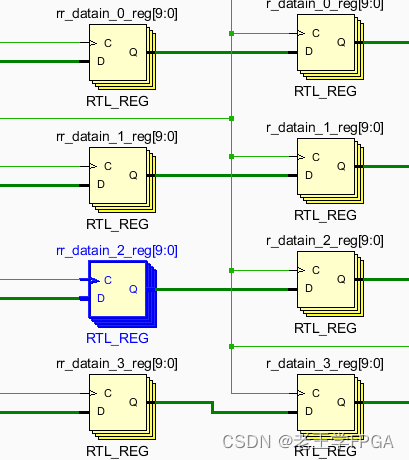

在数据接收端进行了双寄存处理,这样可以解决采样的亚稳态问题,确保数据接收准确。

然而只做这样的处理还不够,综合布线后,时序报告显示了几处时序违例。

时序显示,某些路径的建立时间不满足:

扫描二维码关注公众号,回复:

15850463 查看本文章

具体分析,就是在跨时钟采样时,建立时间不满足,也就是对于高速时钟来说,从低速时钟来的数据稳定的太慢。这样,就有两种处理思路,减少数据路径上的延时、延缓高速时钟的到来。

基于这些思路,对这两路时钟分别进行减少/增加延时的处理。

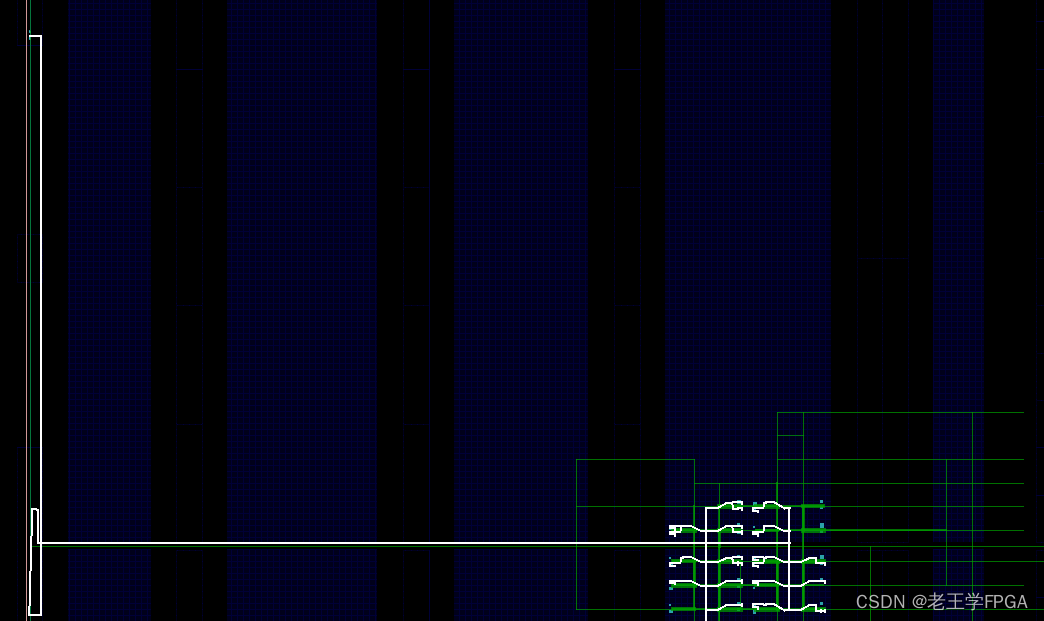

来看设计的布线图:

可以看出,PLL出来的两路时钟被连接到了全局时钟缓冲器上。

可以看出,PLL出来的两路时钟被连接到了全局时钟缓冲器上。

这样只要我们将clk的走线改变使其直连到更近的BUFR区域缓冲器上,可以减少时钟到逻辑的延时。

再给clkx5这个时钟增加一些延时,将其连接到BUFH缓冲器上。经过这些操作就可以达到时序收敛的结果。

处理后,clk时钟与逻辑区域的距离更近了,减少了延时。

最后,时序收敛问题得到解决。

这是一种时序处理的思路,希望能帮到大家!