I2S/PCM是典型的低速串口,在两个方向上分别有两组信号,我们已soc为视角分为soc-adif和外设audio-codec。

那么adif输入:

sclk_i, ws_i, sdi

当然并不是三个输入信号同时有效,只有adif RX slave时,三个输入都会有效

adif输出:

sclk_o, ws_o, sdo

也只有adif TX master时,三个输出才会有效。

下面要解释两个问题

1.TX master和RX slave时说明 adif与codec怎么完成的bitsync;

2.TX slave和RX master时说明 怎么保证RX输出的ws/fs sclk到了TX端产生sdo之后,再到RX端用ws/fs sclk能够正确采样

其实第一个问题对应的时信号间的skew;第二个问题对应的时信号传输的latency。

首先我们给出一些参数的量级:

adif和codec的寄存器setup和hold时间都在 几个ns

adif和codec的工作时钟都是sclk的十几到上百倍

sclk(bitclk采样时钟)最大十几MHz,所以sclk的周期在100ns量级 【所有音频采样率及采样深度请见另一文章 TODO】

1.I2S/PCM 同步

I2S/PCM自带帧同步信号,对于I2S来说ws的下降沿就是帧起始;对于PCM来说fs的上升沿就是帧起始。

那么如何保证bit同步呢?不同于高速串行接口有复杂的bit同步电路,I2S/PCM的bit同步很简单,主要由以下几个机制来完成:

- 对信号组设置skew约束,skew都约束在5ns以下【见过约束为1ns,3ns的。这个skew阈值和工艺以及IO电压有关】约束包括soc端和codec端。-----见图1

- 用高频adifclk采样信号,并对信号进行adifclk打拍---调整相位

- sclk的上升沿改变信号,下降沿采样数据,这样有足够的采样窗口----见图4

设T(sclk) ,T(fs) 和 T(sdo)分别是TX master时 从adif TX到芯片IO的延迟时间,或者Rx slave时从芯片IO到adif RX的延迟时间。

其中对于I2S这种需要输出sclk+控制信号+data的接口,通常会有以下的延时要求

T(sclk) <= T(fs) <= T(sdo)------这种约束的前提就是setup、hold、Tco远小于sclk周期

当然如果采用sclk上升沿改变信号,下降沿采样信号的处理下,上面的约束可以不用设置。

下面就以数据从adif TX 到芯片IO这一段来分析时序:

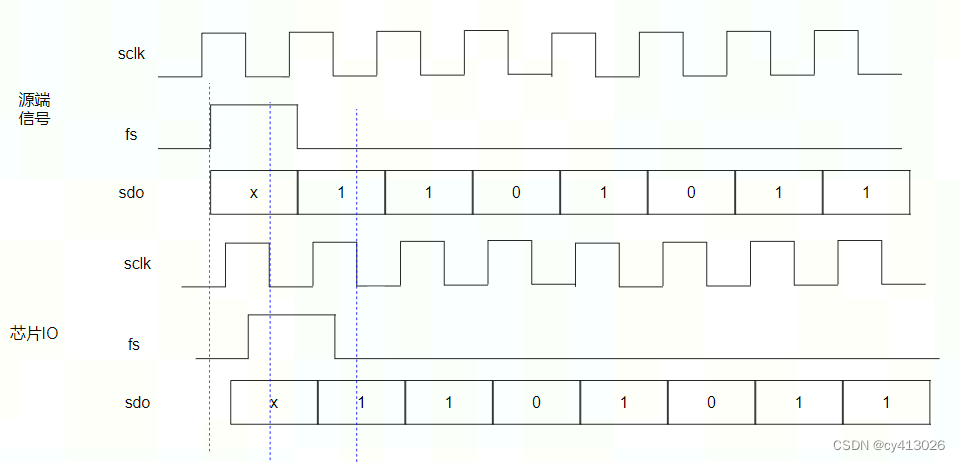

NOTE:下图源端信号中 fs和sdo都是在上升沿改变,且与上升沿的delay很小,这个delay就是寄存器的内部延迟Tco,是符合实际情况的。

图 1

上图中看出T(sclk), T(fs)和T(sdi) 差别较大,在源端三个信号的关系是 用sclk上升沿采样fs和sdo数据,其中sdo第一个数据‘1’与fs有一拍间隔;而在IO处,用sclk采样fs和sdo时,会发现fs和sdo第一笔数据差了两拍,明显出现了错误,所以尽量约束信号在传输过程中的skew,理想情况下,三根信号skew为0,必然在收端是可以正确采样的。

图 2

图2显示了上升沿变换,上升沿采样的情况下 T(fs)< T(sclk) < T(sdo)的情况,虽然三则之间skew不大【只要T(sclk)>T(fs)+Tco】,就出现了fs和sdo第一笔数据差了2各sclk的情况。

其他不满足T(sclk) <= T(fs) <= T(sdo)的情况,也很容易出现时序错误,根因在于Tco太小,T(fs)和T(sdo)延迟小了就会被提前采样。

图 3

图3就给出了T(sclk) <= T(fs) <= T(sdo)情况下的时序图,明显看出各信号都在正确的沿被采样。

图 4

图4给出了上升沿源端改变信号,芯片IO处用下降沿采样的时序图,T(fs) > T(sdo),但任然能够正确的采样数据。而且可以看到相对于下降沿,采样窗口左右两边都大了很多。

2.I2S/PCM的板间latency

在TX slave 和Rx master的工作模式下,TX接收Rx输出的ws/fs和sclk信号并进行同步,这个同步的过程需要TX 两个adifclk时间,再加上沿检测只有变化后沿【即翻转后一个脉冲宽度的信号】又晚了一个adifclk,然后用ws/fs、sclk的变化后沿输出sdo,sdo经过板间延迟T(sdo),到达RX,而此时要用RX的ws/fs和sclk来正确采样sdo,这就要求3adifclk+T(sdo)不要超过一个sclk的周期,这个也可以画时序图来分析,这里不在赘述。

在实际的项目中由于sclk在100ns量级,adifclk在10ns~0.xns的量级,T(sdo)也在几十ns【不确定】的范围,所以是很容易达到的,有些项目就没有对latency设置约束。

如果sdo在RX master端和ws/fs间隔太远超过1个sclk,有没有设计上的手段来保证不影响音频接收?

这时RX会检测到错误,比如sdata的bit数左右声道不一致,或整帧的bit数和配置值不一样。这时上报错误,然后控制Rx端的ws/fs向后delay n个sclk,直到软件检测不到错误。