I2S(Inter-IC Sound)是一种广泛应用于数字音频传输的串行接口标准。它最初由飞利浦(Philips)公司开发,用于解决在集成电路之间传输音频数据的问题。I2S协议定义了音频数据的传输格式、时序和控制信号。

I2S信号定义

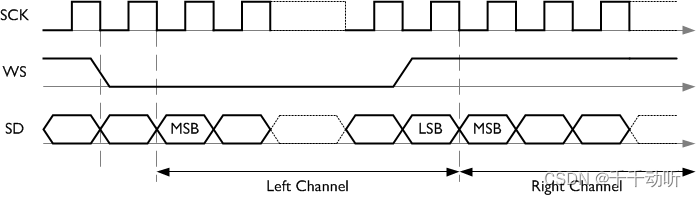

如上图I2S接口通常由三类信号线组成

- 时钟线(Continuous Serial clock ,SCK):SCK线提供了同步音频数据传输的时钟信号。它确定了数据传输的速度和时序。也称Bit Clock (BCLK)。

- 左/右声道线(Word Select,WS):WS线指示了当前传输的是左声道还是右声道的音频数据。它也被称为帧同步信号。也称Frame Sync (FS), Word Clock (WCLK), Left-Right Clock (LRCLK)。

- 数据线(Serial Data,SD):SD线用于传输实际的音频数据。数据的位宽可以根据具体应用而变化,通常是16位或32位。也称Serial Data Out/In (SDOUT, SDIN)

I2S协议定义了一些参数,用于描述音频数据的传输方式和格式。以下是I2S协议中常见的参数:

- 位宽(Word Length):位宽指定每个采样数据的位数,通常为16位或32位。较大的位宽可以提供更高的分辨率和动态范围。

- 时钟极性(Clock Polarity):时钟极性确定了数据位传输的时钟沿。根据具体的I2S设备和系统设置,可以定义时钟沿的上升沿或下降沿作为数据传输的起始点。

- 帧同步极性(Frame Sync Polarity):帧同步极性确定了帧同步信号的有效电平。帧同步信号指示了音频数据的帧起始和结束位置。可以根据具体需求设置帧同步信号的极性。

- 传输格式(Data Format):传输格式定义了音频数据的编码方式,例如PCM(脉冲编码调制)或压缩编码。传输格式还可以指定数据的顺序,如左声道先传输还是右声道先传输。

主从工作模式

I2S工作模式可以是主模式(Master Mode)或从模式(Slave Mode)。在主模式下,主设备负责提供时钟信号和帧同步信号,控制音频数据的传输。在从模式下,从设备接收来自主设备的时钟和帧同步信号,并接收或发送音频数据。

如上图:

- TRANSMITTER(发射器)= CONTROLLER(控制器):发射器在I2S通信中扮演主设备的角色。它负责生成和传输音频数据,控制通信的时序和时钟信号。发射器通过发送时钟信号(如帧时钟BCLK和字选择时钟LRCLK/WS)来控制数据传输。因此,发射器可以看作是主控制器,负责主导数据传输过程。

- RECEIVER(接收器)= CONTROLLER(控制器):当接收器充当控制器时,它工作在主模式,负责接收和处理来自发射器的音频数据,并提供时钟信号以进行同步。接收器作为控制器时,它会生成时钟信号,包括帧时钟BCLK和字选择时钟LRCLK/WS,并控制数据接收和处理过程。

- 独立的CONTROLLER(控制器):额外的控制器在I2S通信系统中起到主控制的角色。它负责协调TRANSMITTER和RECEIVER之间的数据传输和时序控制。控制器生成时钟信号(如帧时钟BCLK和字选择时钟LRCLK/WS)。

数据传输模式

I2S接口标准中,除了飞利浦标准模式之外,还存在左对齐(Left Justified)和右对齐(Right Justified)两种传输模式。它们的区别主要体现在数据帧的对齐方式和同步信号的位置上。

标准模式

I2S philips标准

对于I2S飞利浦标准模式,数据的传输和同步如下:

- LRCLK(左右声道选择信号,WS):LRCLK信号用于指示当前数据帧是左声道还是右声道的数据。当LRCLK为逻辑0时,表示当前传输的数据是左声道的有效数据;当LRCLK为逻辑1时,表示当前传输的数据是右声道的有效数据。

- BCLK(位时钟):BCLK信号是数据传输的时钟信号。发送方在BCLK的下降沿更新数据,而接收方在BCLK的上升沿读取数据。BCLK的频率通常是采样频率的倍数,用于同步数据的传输。

- 数据延迟:发送的有效数据相对于LRCLK的变化沿(从0到1或从1到0)延迟一个时钟周期。也就是说,数据的变化在LRCLK变化之后的下一个BCLK周期发生。

- 综合起来,当LRCLK信号变化时,指示当前传输的数据是左声道还是右声道。发送方在BCLK的下降沿变化时更新数据,而接收方在BCLK的上升沿变化时读取数据。这样可以确保数据的同步和正确的采样顺序。

左对齐模式

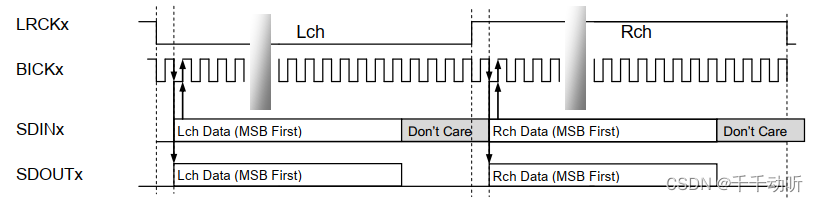

左对齐(Left Justified)

对于左对齐标准(Left-Justified Standard),LRCLK信号的含义与飞利浦标准相反。在左对齐标准下,LRCLK为逻辑1表示传输的是左声道数据,LRCLK为逻辑0表示传输的是右声道数据。

- 左声道数据的MSB在LRCLK上升沿之后的第一个SCK/BCLK(Bit Clock)上升沿有效。

- 右声道数据的MSB在WS下降沿之后的第一个SCK/BCLK上升沿有效。

- 左对齐格式的优点在于,它不需要关心左右声道数据的字长,只要LRCLK的时钟周期足够长,左对齐的方式就能支持16-32位字长格式。

右对齐(Right Justified)

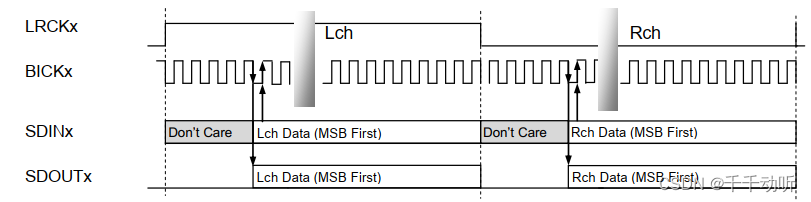

右对齐模式

同样,对于右对齐标准(Right-Justified Standard),LRCLK信号的含义与飞利浦标准相反。在右对齐标准下,LRCLK为逻辑1表示传输的是左声道数据,LRCLK为逻辑0表示传输的是右声道数据。

- 左声道数据的LSB在LRCLK下降沿的前一个SCK/BCLK上升沿有效。

- 右声道数据的LSB在LRCLK上升沿的前一个SCK/BCLK上升沿有效。

- 相比左对齐格式,右对齐的不足在于接收设备必须事先知道待传数据的字长。