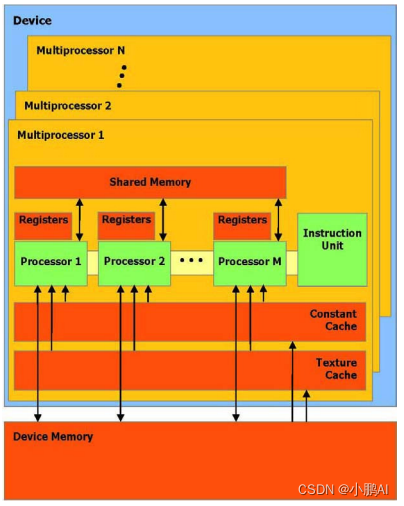

一组带有on-chip 共享内存的SIMD多处理器

GPU可以被看作一组多处理器, 每个多处理器使用单一指令,多数据架构(SIMD)【单指令流多数据流】

在任何给定的时钟周期内,多处理器的每个处理器执行同一指令,但操作不同的数据

每个多处理器使用以下四种类型的on-chip(集成的)内存:

- 每个处理器一组本地32位寄存器

- 并行数据缓存或共享内存,被所有处理器共享实现内存空间共享

- 通过设备内存的一个只读区域,一个只读常量缓冲器被所有处理器共享

- 通过设备内存的一个只读区域,一个只读纹理缓冲器被所有处理器共享

本地和全局内存空间作为设备内存的读写区域,而不被缓冲

每个多处理器通过纹理单元访问纹理缓冲器,它执行各种各样的寻址模式和数据过滤

执行模式

一个线程块栅格是通过多处理器规划执行的

一个块只被一个多处理器处理,因此可以对驻留在on-chip 共享内存中的共享内存空间形成非常快速的访问

一个批处理中每一个多处理器可以处理多少个块,取决于每个线程中分配了多少个寄存器和已知内核中每个时钟需要多少的共享内存

因为多处理器的寄存器和内存在所有的线程中是分开的

如果在至少一个块中,每个多处理器没有足够的寄存器或共享内存可用,那么内核将无法启动

线程块在一个批处理中被一个多处理器执行,被称作active

每个active 块被划分成为SIMD 线程组,称为warps

每一条这样的warp 包含数量相同的线程,叫做warp 大小,并且在SIMD 方式下通过多处理器执行

线程调度程序周期性地从一条warp 切换到另一条warp,以达到多处理器计算资源使用的最大化!

块被划分成为warp 的方式是相同的

每条warp 包含连续的线程,线程索引从第一个warp 包含着的线程0 开始递增

一个多处理器可以处理并发地几个块,通过划分在它们之中的寄存器和共享内存

更准确地说,每条线程可使用的寄存器数量,等于每个多处理器寄存器总数除以并发的线程数量

并发线程的数量等于并发块的数量乘以每块线程的数量

在一个块内的warp 次序是未定义的,但通过协调全局或者共享内存的存取,它们可以同步的执行

如果一个通过warp 线程执行的指令写入全局或共享内存的同一位置,写的次序是未定义的

在一个线程块栅格内的块次序是未定义的,并且在块之间不存在同步机制

因此来自同一个栅格的二个不同块的线程不能通过全局内存彼此安全地通讯

计算兼容性

设备的计算兼容性由两个参数定义,主要版本号和次要版本号

设备拥有相同的主要版本号代表相同的核心架构

次要版本号代表一些改进的核心架构,比如新的特性

多设备

为一个应用程序使用多GPU 作为CUDA 设备,必须保证这些GPU 是一样的类型

如果系统工作在SLI 模式下,那么只有一个GPU 可以作为CUDA 设备

因为所有的GPU 在驱动堆栈中被底层的融合了

SLI 模式需要在关闭,这样才能使用多个GPU 作为CUDA设备

模式切换

GPU 指定一些DRAM 来存储被称作primary surface 的内容,这些内容被用于显示输出

如果用户改变显示的分辨率或者色差,那么primary surface 的存储需求量将改变

如果用户将显示分辨率从1280x1024x32bit 到1600x1200x32bit

那么,系统必须指定7.68MB 的primary surface 而不在是5.24MB

(使全屏抗锯齿的应用程序需要更多的primary surface空间)

如果模式切换增加了primary surface 的内存空间,系统将会占用CUDA 所指定的内存空间,导致OOM。

什么是纹理缓冲器

纹理存储器(texture memory)是一种只读存储器,由GPU用于纹理渲染的的图形专用单元发展而来,因此也提供了一些特殊功能。

纹理缓存的优势:

纹理缓存具备硬件插值特性,可以实现最近邻插值和线性插值。纹理缓存针对二维空间的局部性访问进行了优化,所以通过纹理缓存访问二维矩阵的邻域会获得加速。纹理缓存不需要满足全局内存的合并访问条件。

纹理可以是一段连续的设备内存,也可以是一个CUDA数组。但是CUDA数组对局部寻址有优化,称为“块线性”,原理是将邻域元素缓存在同一条cache线上,这将加快邻域内的寻址,但是对于设备内存,并没有“块线性”。所以,选择采用CUDA数组,还是设备内存,需要根据实际情况决定,将数据copy至CUDA数组是很耗时的。