前言

零基础初学数字IC,学会什么写什么,与大家一起进步。

最近面试过程中经常被问到有关功耗的问题,回答的不是很好,所以本篇中主要总结一下与功耗相关的问题,以便后续复习。

一、数字芯片的功耗定义

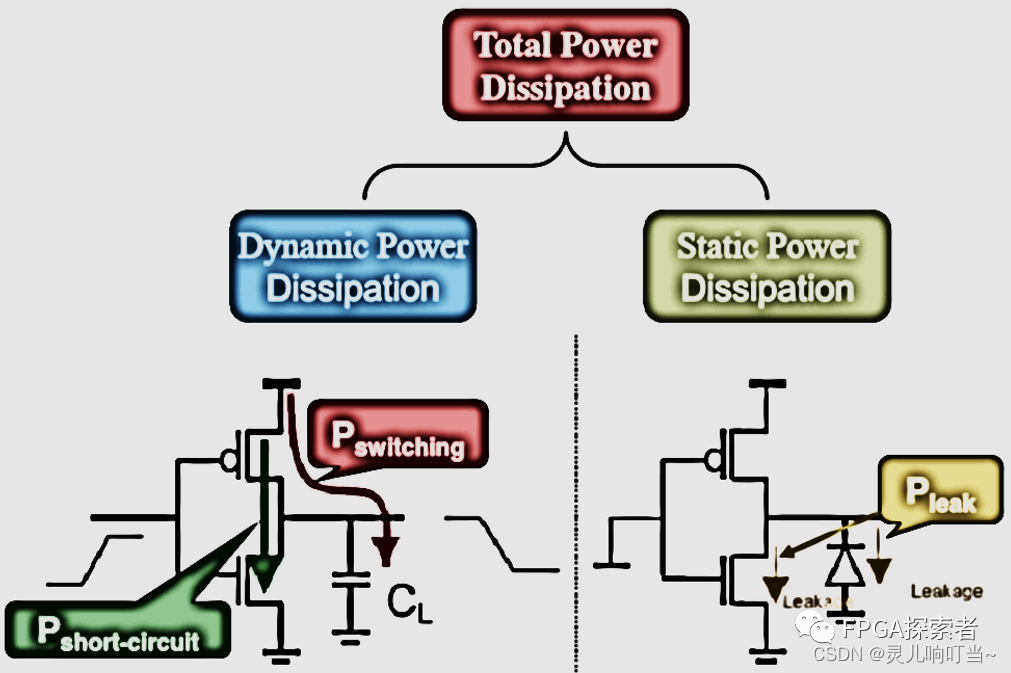

数字芯片的功耗可以分为两个部分:动态功耗和静态功耗。动态功耗是芯片正常工作时由于信号翻转产生的功耗,静态功耗是电路在通电但是不工作时产生的功耗。

动态功耗

动态功耗(Dynamic Power)= 翻转功耗(Switch Power) + 短路功耗(Internal Power)

翻转功耗:芯片在工作过程中,由于负载电容进行充放电导致的功耗;

短路功耗(Internal Power):信号的翻转不是在瞬时完成的,那么在翻转的过程中总有一段时间会导致NMOS和PMOS同时导通,那么相当于在VDD和GND之间形成了短路,由此产生的功耗就是短路功耗;

静态功耗

静态功耗(Leakage Power)主要是由于泄露电流而导致的功耗,在CMOS 门中,漏电流主要来自4个源头:

- 亚阈值漏电流(Sub-threshold Leakage, ISUB): 亚阈值泄漏电流是晶体管应当截止时流过的电流;

- 栅极漏电流(Gate Leakage, Igate): 由于栅极氧化物隧穿和热载流子注入,从栅极直接通过氧化物流到衬底的电流;

- 栅极感应漏电流(Gate Induced Drain Leakage, IGIDL): 结泄漏电流发生在源或漏扩散区处在与衬底不同电位的情况下。结泄漏电流与其他泄漏电流相比时通常都很小。

- 反向偏置结泄漏(Reverse Bias Junction Leakage ,IREV):由少数载流子漂移和在耗尽区产生电子/空穴对引起。

静态功耗可以看作是 电压,阈值电压 和 晶体管尺寸的函数。

二、如何降低功耗?

2.1 降低动态功耗

电压角度:

- 降低工作电压;

- 使用多电压域:对于不同 function 的 blocks 和 modules 提供不同的电压;例如,对于存储器采用高电源电压来保证存储单元的稳定性,对于处理器采用中等大小的电压,对运行速度较低的IO外围电路采用低电压;决跨电压域信号传输的方法是使用电平转换器;

- 动态电压缩放技术 DVS(Dynamic voltage scaling):芯片在运行的过程中动态的调整某些部分的电压;例如:处理器可以在不同的工作模式下使用不同的电压;

- 动态电压频率缩放技术 DVFS(Dynamic voltage frequency scaling):芯片在运行的过程中动态的调整某些部分的电压和频率;这种技术需要软硬件协同处理;

- 电源关断 Power-gating;

负载电容角度:

- 合理的布局布线;

- 等比例缩小晶体管尺寸;

- 多芯片系统中可以考虑使用多芯片封装技术,降低接口电容;

- 减小逻辑深度;

数据翻转角度:

- 减少不必要的数据翻转;

- 当不需要操作时,数据保持不变,不强制置0或者置1;

- 使用格雷码等状态翻转较少的编码;

频率角度:

- 降低工作频率;

- 多时钟域;

- DVFS 动态电压频率缩放技术;

- 使用门控时钟,clock gating;

2.2 降低静态功耗

电压角度:

- 降低工作电压;

- 使用多电压域;

- 动态电压缩放技术 DVS(Dynamic voltage scaling);

- 动态电压频率缩放技术 DVFS(Dynamic voltage frequency scaling);

- 电源关断 Power-gating;

泄露电流角度:

- 提高使用高阈值电压的晶体管 HVT 的比例;

- 使用多种阈值电压的晶体管:对于不同的 blocks,modules 安排使用不同阈值电压的晶体管,实现 performance 和 power 的balance;

- 使用多栅氧厚度晶体管;

- 调节衬底电压,使晶体管处于反向体偏置;

总结

以上就是今天学习的数字芯片中功耗相关的内容,欢迎大家一起讨论交流~

参考资料:

IC设计中节省静态功耗和动态功耗的方法_降低动态功耗的方法_一点一点的进步的博客-CSDN博客数字IC笔试题(7)——低功耗设计【静态功耗】【动态功耗】