文章目录

前言

CPLD(Complex Programmable Logic Device)是一种可编程逻辑器件,可以用于实现数字逻辑电路的功能。CPLD通常包含可编程逻辑单元(如逻辑门阵列)和可编程的连接资源(如可编程互连)。CPLD的在线升级是指在运行时对CPLD进行固件升级,以更新其逻辑功能或修复错误。

要进行CPLD的在线升级,通常需要以下步骤:

-

准备升级文件:首先,需要准备包含新固件的升级文件。这个文件通常是由CPLD供应商提供的。升级文件可以是二进制文件、Intel HEX文件或其他特定格式的文件。

-

连接CPLD:将CPLD与升级工具连接起来。连接方式可以是通过JTAG接口、SPI接口或其他特定的接口。

-

启动升级工具:启动CPLD的升级工具。这个工具可以是供应商提供的专用工具,也可以是通用的编程工具,如Quartus Prime(用于Altera CPLD)或Xilinx ISE(用于Xilinx CPLD)。

-

选择目标设备:在升级工具中选择要升级的目标CPLD设备。这通常涉及选择正确的设备型号和连接接口。

-

导入升级文件:将升级文件导入升级工具。工具将解析文件并准备进行升级。

-

执行升级:执行升级操作。这通常涉及擦除CPLD的当前固件,然后将新固件编程到CPLD中。

-

验证升级:升级完成后,可以使用升级工具进行验证,以确保新固件已正确编程到CPLD中。

一、JTAG芯片介绍

具有JTAG口的芯片都有如下JTAG引脚定义:

TCK——测试时钟输入;TCK为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的。

TDI——测试数据输入接口,数据通过TDI输入JTAG口;所有要输入到特定寄存器的数据都是通过TDI接口一位一位串行输入的(由TCK驱动)

TDO——测试数据输出接口,数据通过TDO从JTAG口输出;所有要从特定的寄存器中输出的数据都是通过TDO接口一位一位串行输出的(由TCK驱动)。

TMS——测试模式选择,TMS用来设置JTAG口处于某种特定的测试模式。TMS信号在TCK的上升沿有效。TMS信号用来控制TAP状态机的转换。通过TMS信号,可以控制TAP在不同的状态间相互转换。

MCPLD升级使能信号

RCPLD升级使能信号

二、JTAG协议分析

JTAG(Joint Test Action Group)是一种用于测试和调试电子设备的标准接口和协议。它提供了一种在芯片级别上进行测试、调试和编程的能力。JTAG协议定义了一组命令和信号,用于在芯片上进行测试、配置和调试操作。

JTAG协议包括以下几个主要组成部分:

-

TAP(Test Access Port)控制器:TAP控制器是JTAG协议的核心组件,它负责控制JTAG操作的执行。TAP控制器包含一个状态机,用于管理JTAG操作的状态转换。它还提供了与外部设备(如处理器、调试器或测试设备)进行通信的接口。

-

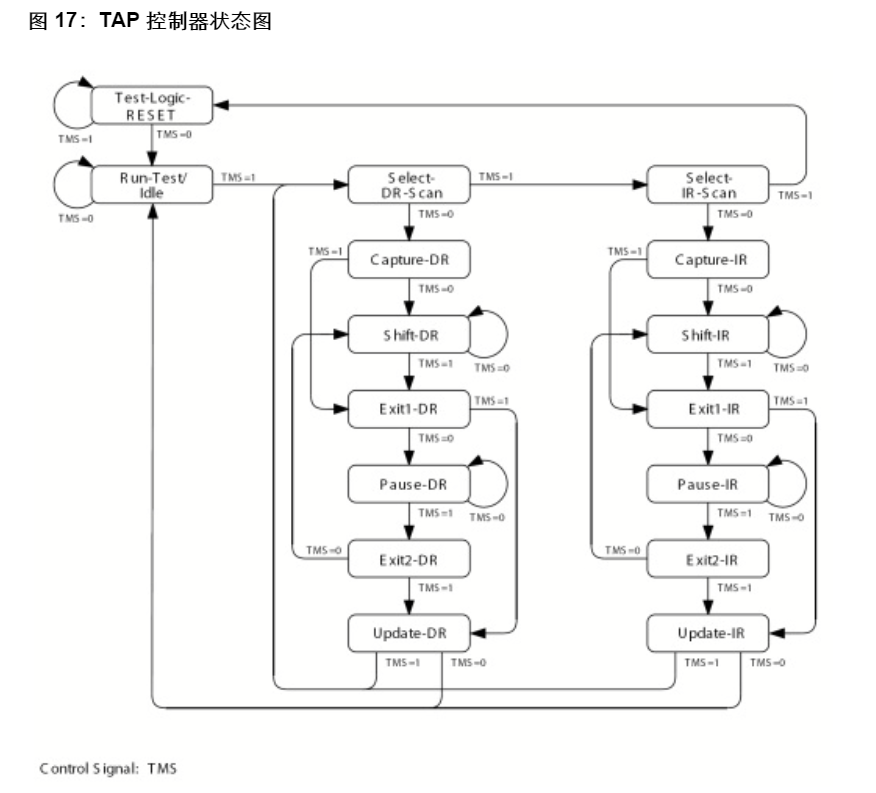

TAP控制器状态机:TAP控制器的状态机定义了JTAG操作的不同状态和状态之间的转换规则。常见的状态包括测试逻辑重置(Test Logic Reset,TLR)、运行-测试/配置(Run-Test/Idle,RTI)、选择-测试/配置(Select-DR-Scan/IR-Scan,SDR/SIR)等。

-

数据寄存器链(DR):数据寄存器链是一系列连接在JTAG链上的寄存器,用于进行数据的输入和输出。DR链可以包含多个寄存器,每个寄存器可以存储一定数量的数据。

-

指令寄存器链(IR):指令寄存器链是用于加载和执行JTAG指令的寄存器链。它类似于数据寄存器链,但用于传输和处理指令数据。

在使用JTAG进行测试、调试或编程时,通常遵循以下步骤:

-

初始化:通过TAP控制器将JTAG链上的所有设备初始化到一个已知状态。

-

选择设备:选择要与之通信的目标设备,将其与TAP控制器连接。

-

选择-测试/配置(SDR/SIR):将TAP控制器切换到选择-测试/配置状态,以选择要进行测试或配置的寄存器链(DR或IR)。

-

数据传输:在选择-测试/配置状态下,通过TAP控制器进行数据的输入和输出。可以通过DR链传输测试数据或配置数据,通过IR链传输指令数据。

-

状态转换:根据需要,通过TAP控制器在不同的状态之间进行转换,以执行特定的操作,如测试、配置或调试。

JTAG协议分析可以涉及对JTAG信号和命令的解析、状态机的分析以及数据传输的分析等。这通常需要使用JTAG分析工具或逻辑分析仪等设备来捕获和分析JTAG信号,并使用相关的协议分析软件进行解析和分析。

需要注意的是,JTAG协议在不同的芯片和设备之间可能会有一些差异,因此在进行JTAG协议分析时,需要参考相关芯片或设备的文档和规范,以了解其特定的JTAG实现和功能。

1.TAP状态机

TMS、TCK、TDI、TDO

JTAG数据操作是基于移位寄存器的

状态机每一个状态有两个状态触发——TCK上升沿和TMS电平决定跳转分支

TAP 控制器是一个基于 TMS 的同步状态机 (Test Mode Select) 和 TCK (Test Clock) 信号并控制 TAP IEEE 1149.1 标准定义的电路操作序列。 对于当前莱迪思,TCK 信号可以以最大 25 MHz 的频率驱动 符合 IEEE 1532 标准的设备。

在 Shift-DR 状态下,存在一个解码器来选择哪个移位寄存器是 启用并将其连接在 TDI 和 TDO 之间。以下是移 寄存器:地址移位寄存器、数据移位寄存器、32位移位寄存器、 和旁路。32 位移位寄存器用于存储 ID 代码和 用户代码。输入任何寄存器的第一位被放入 MSB,随着附加位的计时,数据向 TDO 移动一位。

1. SIR case 语句首先提取寄存器的大小。规模 稍后将用于指示将发送或读回多少位数据 从设备。然后处理器将设备转换为安全状态 IRPAUSE,然后到状态 SHIFTIR。如果 HIR 存在(参见 HIR 案例 语句),那么处理器将绕过 HIR。SIR 子开关是一个 基于字节码的开关,之后可能会找到 SIR 字节码。

2. TDI字节码表示有数据需要移入设备。处理器将设置 TDI 索引变量指向该位置 TDI 数据在算法缓冲区中开始的位置。

3. DTDI字节码表示有数据需要移入装置。与 TDI 字节码不同,DTDI 字节码表示数据 将来自数据缓冲区。如果数据缓冲区已压缩 上,将检查数据帧的第一个字节以查看该帧是否为 确实可以压缩。

4. TDO字节码表示有数据需要读取,从设备验证。处理器会将 TDO 索引变量设置为指向算法缓冲区中 TDO 数据开始的位置。

5. DTDO字节码表示有数据需要读取 从设备验证。与 TDO 字节码不同,DTDO 字节码 表示数据将来自数据缓冲区。如果数据缓冲区有压缩开启,会检查数据帧的第一个字节看 如果框架确实是可压缩的。

6. MASK字节码表示有需要使用的掩码数据 将 TDO 值与扫描出的实际值进行比较时 设备。处理器将设置 MASK 索引变量指向该位置 MASK 数据在算法缓冲区中的起始位置。

7. UNKNOWN case 语句是无法识别的字节码的默认值。 这种情况会返回错误代码 ERR_ALGO_FILE_ERROR 或 -5,以指示 算法中的错误。

8. CONTINUE 字节代码终止 SIR 指令。当这个字节是 遇到,表示TDI、DTDI、TDO、DTDO、MASK索引 指向它们的正确位置并且处理器已准备好发送或 从设备读取和验证数据。

如果尚未设置 CASCADE,则处理器将设备转移到 安全状态 IRPAUSE,然后到 SHIFTIR。如果 HIR 存在(参见 HIR 案例 语句),那么处理器将绕过 HIR。SIR 子开关是一个 基于字节码的开关,之后可能会找到 SIR 字节码。

字节码 CONTINUE 出现在每个 SIR 和 SDR 的末尾 指令作为终结者。

字节码 END_FRAME 出现在 VME 中每一帧的末尾 数据作为终结符。

使用的压缩方案基于连续出现 帧中的0xFF字节。这个字节无处不在,因为一个全0xFF 的数据文件 是一个空白模式。当连续数的Ñ 0xFF的字节是 遇到,VME 数据文件将有字节0xFF后跟 数字n转换为十六进制,其中n不能超过255。对于 例如,如果以下是部分数据框 FFFFFFFFFFFFFFFFFFFF12FFFFFF 结果压缩数据将是 0xFF 0x0A 0x12 0xFF 0x03 当处理器遇到第一个字节0xFF 时,它会获取下一个字节 确定0xFF被压缩了多少次。下一个字节是0x0A , 这是十六进制的十。这指示处理器0xFF是 压缩十次。接下来的字节是0x12 ,按原样处理。 下一个字节再次是0xFF后跟0x03 ,它指示处理器 该0xFF的被压缩的三倍。