数码管动态扫描显示例程讲解

根据多年工作经验,总结出的FPGA的设计流程,概括起来总共有以上12步,其中根据项目难易度可省去其中一些步骤。比如非常简单的项目,我们可以省去虚线框里面的步骤,但是我们的入门级课程,即使再简单,也按照这12个步骤来进行讲解。

1. 需求解读

1.1 需求

在六位数码管上稳定的显示123456

1.2 知识背景

数码管是由多个 LED 发光二极管组成的一个“8”字型的器件,根据极性不同,分为共阳极和共阴极,我们开发板上采用的是共阳数码管。数码管内部结构如下图:

通过图上可以看出,共阳极和共阴极的区别。共阳极公共端接电源正极,共阴极公共端接地。选用共阳极数码管时,我们只需将对应的 abcdefgdq 给低电平便可点亮对应的数码管。共阴极与之相反,需要将 abcdefgdq 接入电源正极便可点亮对应的数码管。数码管示意图如下:

我们选用的开发板使用的是共阳极数码管,如果要显示 2,那么我们应该点亮

A,B,G,E,D 段发光二极管。如果要显示 5,大家可以自行分析,应该点亮哪些段,这样我们便可以得出共阳数码管 0 到 9 的编码。为了节约大家的时间,我将共阳数码管对应的编码整理出来,如下图,可以直接调用。共阴数码管的编码只用按位取反即可。

开发板共阳数码管段选编码表如下:

1.3 硬件设计

开发板上选用的是PNP三极管,当给三极管基极输入低电平,三极管的集电极与发射极便导通,3.3V 的电压便加在了数码管的位选管脚上,那么我们要点亮第一位数码管则需要给SMG_W0 输入低电平,并按数码管编码表给数码管的段选赋值。原理掌握了,我们可以开始编写代码

1.4 接口说明

| 信号名 | 方向 | FPGA管脚号 | 说明 |

|---|---|---|---|

| SMG_W0 | 输出 | E12 | 位选控制信号,低电平可导通三极管,使其给数码管位选供电 |

| SMG_W1 | 输出 | B15 | 位选控制信号,低电平可导通三极管,使其给数码管位选供电 |

| SMG_W2 | 输出 | E15 | 位选控制信号,低电平可导通三极管,使其给数码管位选供电 |

| SMG_W3 | 输出 | H11 | 位选控制信号,低电平可导通三极管,使其给数码管位选供电 |

| SMG_W4 | 输出 | K16 | 位选控制信号,低电平可导通三极管,使其给数码管位选供电 |

| SMG_W5 | 输出 | K14 | 位选控制信号,低电平可导通三极管,使其给数码管位选供电 |

| SMG_A | 输出 | F13 | 数码管段选控制信号,低电平点亮该段 |

| SMG_B | 输出 | B16 | 数码管段选控制信号,低电平点亮该段 |

| SMG_C | 输出 | J16 | 数码管段选控制信号,低电平点亮该段 |

| SMG_D | 输出 | J13 | 数码管段选控制信号,低电平点亮该段 |

| SMG_E | 输出 | G14 | 数码管段选控制信号,低电平点亮该段 |

| SMG_F | 输出 | E13 | 数码管段选控制信号,低电平点亮该段 |

| SMG_G | 输出 | G12 | 数码管段选控制信号,低电平点亮该段 |

| SMG_DP | 输出 | J14 | 数码管段选控制信号,低电平点亮该段 |

总结:通过上述说明,可以将需求解读成:当点亮第一位数码管时,位选为6’h1f,此时数码管段选的编码为8’h9f;当点亮第二位数码管时,位选为6’h2f,数码管段选的编码为8’h25;当点亮第三位数码管时,位选为6’h37,数码管段选的编码为8’h0d;当点亮第四位数码管时,位选为6’h3b,数码管段选的编码为8’h99;当点亮第五位数码管时,位选为6’h3d,数码管段选的编码为8’h49;当点亮第六位数码管时,位选为6’h3e,数码管段选的编码为8’h41;

2. 绘制理论波形图

3.新建TD工程

为了让工程看起来整洁,同时方便工程移植。我们新建4个文件夹,分别是Project,Source,Sim,Doc。

Project — 工程文件夹,里面放的TD工程

Source — 源代码文件夹,里面放的工程源码(.v文件或.vhd文件)

Sim — 仿真文件夹,里面放的仿真相关的文件

Doc — 存放相关资料,比如数据手册,需求文档等

4.编写代码

///

//QQ:3181961725

//TEL/WX:13540738439

//工程师:Mr Wang

//模块介绍:数据管动态扫描,显示123456

module smg_drv(

input clk ,

input rst_n ,

output reg [5:0] smg_bit ,

output reg [7:0] smg_seg

);

parameter refresh_time=50000;

reg [3:0] cnt;

reg [19:0] refresh_cnt;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

refresh_cnt<=0;

else if(refresh_cnt==refresh_time-1)

refresh_cnt<=0;

else

refresh_cnt<=refresh_cnt+1;

end

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

cnt<=4'hf;

else if(refresh_cnt==0)begin

if(cnt==5)

cnt<=0;

else

cnt<=cnt+1;

end else;

end

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

smg_bit<=0;

smg_seg<=0;

end else case(cnt)

0:begin smg_bit<=8'h3e; smg_seg<=8'h9f;end

1:begin smg_bit<=8'h3d; smg_seg<=8'h25;end

2:begin smg_bit<=8'h3b; smg_seg<=8'h0d;end

3:begin smg_bit<=8'h37; smg_seg<=8'h99;end

4:begin smg_bit<=8'h2f; smg_seg<=8'h49;end

5:begin smg_bit<=8'h1f; smg_seg<=8'h41;end

default:;

endcase

end

endmodule

5.编写仿真测试激励文件

`timescale 1ns/1ns

module smg_drv_tb;

reg clk ;

reg rst_n ;

initial

begin

clk = 0;

rst_n=0;

#1000

rst_n=1;

end

always #10 clk=~clk;

smg_drv Usmg_drv(

.clk (clk),

.rst_n (rst_n),

.smg_bit (),

.smg_seg ()

);

endmodule

6.Modelsim仿真

Modelsim仿真一般有两种方法

-

图形化界面仿真,即所有的操作都是在Modelsim软件界面上来完成,该方式的优点是,简单易学,适用于简单的项目,缺点是操作步骤繁琐。

-

批处理仿真,这种方式在仿真前需要编写相应的脚本文件,该方式的优点是,一键即可完成仿真,省时省力,缺点是前期需要编写脚本文件。前两讲采用的是图形化界面仿真的方式;为了更贴近工程实际,从这一讲开始,我们就采用批处理方式仿真。具体操作步骤可参考我们的视频教程

仿真出的波形如下图所示:

7.对比波形图

将第二步绘制的理论波形图与第六步Modelsim仿真出来的波形图进行对比,结果一致,说明我们的逻辑设计是正确的。如果发现比对结果不一致,就需要找到不一致的原因,最终要保证对比结果一致。通过对比,理论波形与仿真波形一致,说明功能符合设计要求。

8 添加.v文件

9 绑定管脚并保存约束文件(.adc)

10 编译综合生成BIT文件

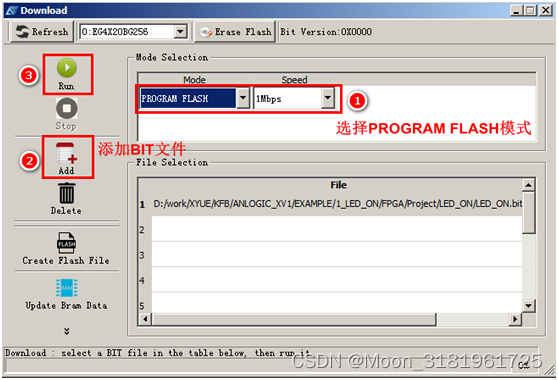

11.下载BIT文件

下载成功后,便可以观察到开发板上的实验现象,如果实验现象与设计需求相符,那说明我们的设计是没有问题的,即可进行下一步固化配置文件。

12 固化配置文件

FPGA有一个特性,就是掉电后配置信息会丢失,所以我们需要将配置信息存储在配置芯片(FLASH)中,待开发板上电后,FPGA便会读取配置芯片中的配置信息,这样开发板掉电再上电后同样可正常工作

固化成功后,开发板断电再重新上电,可以观察到开发板仍然可以执行刚刚的功能。