查询Xilinx官网关于GT Transceiver的用户手册找到了UG476,该文档以7 Series FPGA芯片举例进行说明。

简介

7系列FPGA GTX和GTH收发器是一款节能的收发器,支持线路速率从500Mb /s到12.5 Gb/s的GTX收发器和13.1 Gb/s的GTH收发器高等收发器。GTX/GTH收发器具有高度可配置性,并与FPGA的可编程逻辑资源紧密集成。由此可以看出GTH的速率比GTX的速率更高。

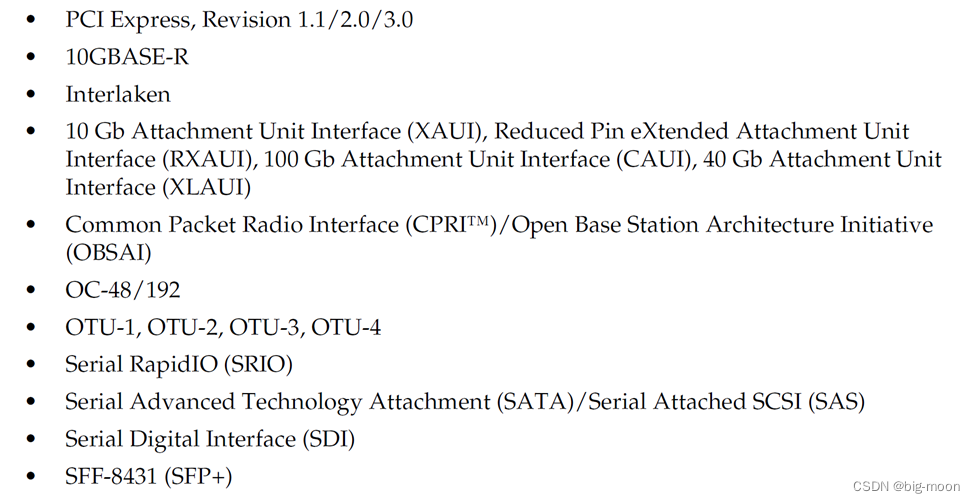

GTX和GTH所支持的使用模式如下:

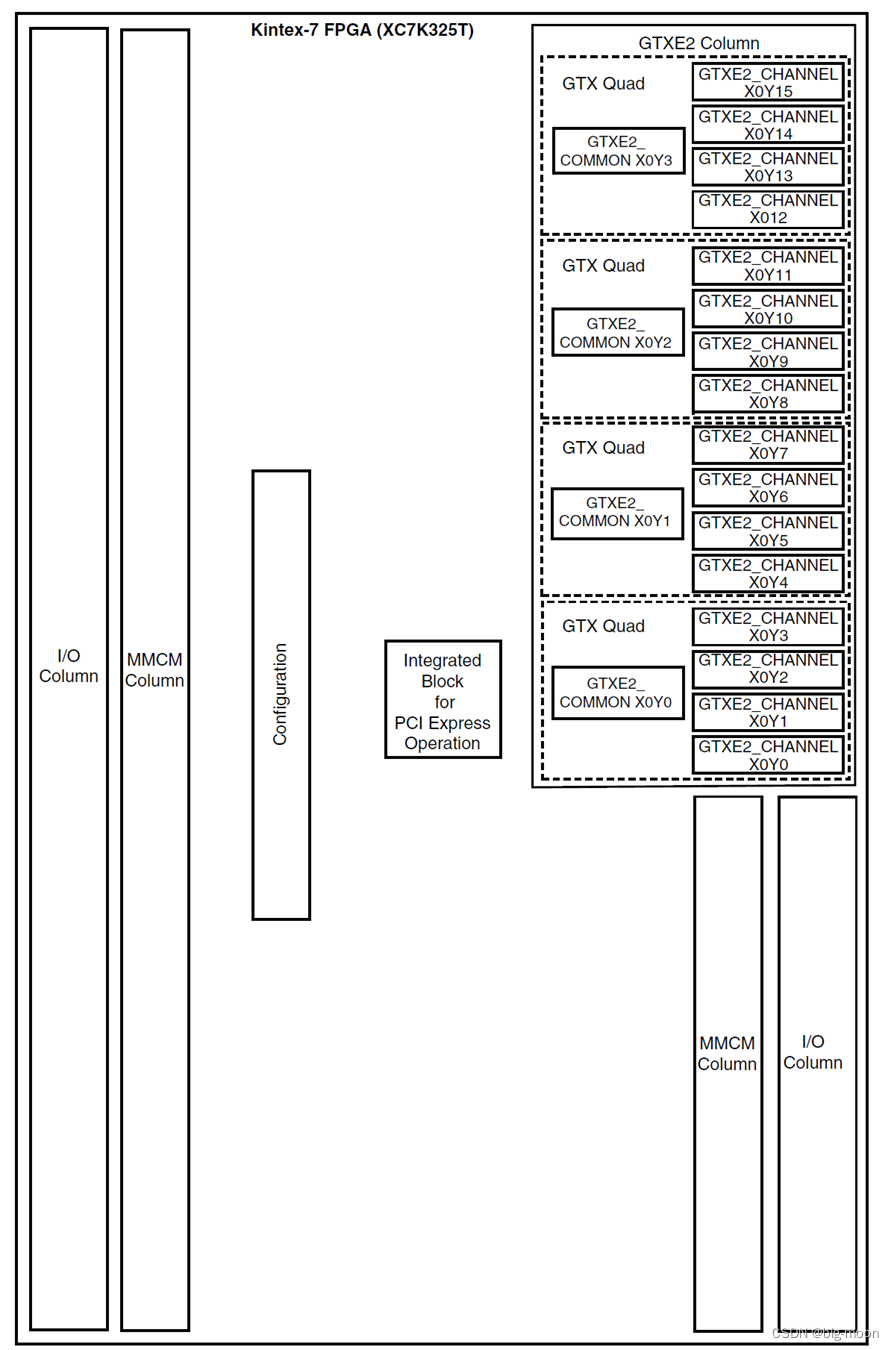

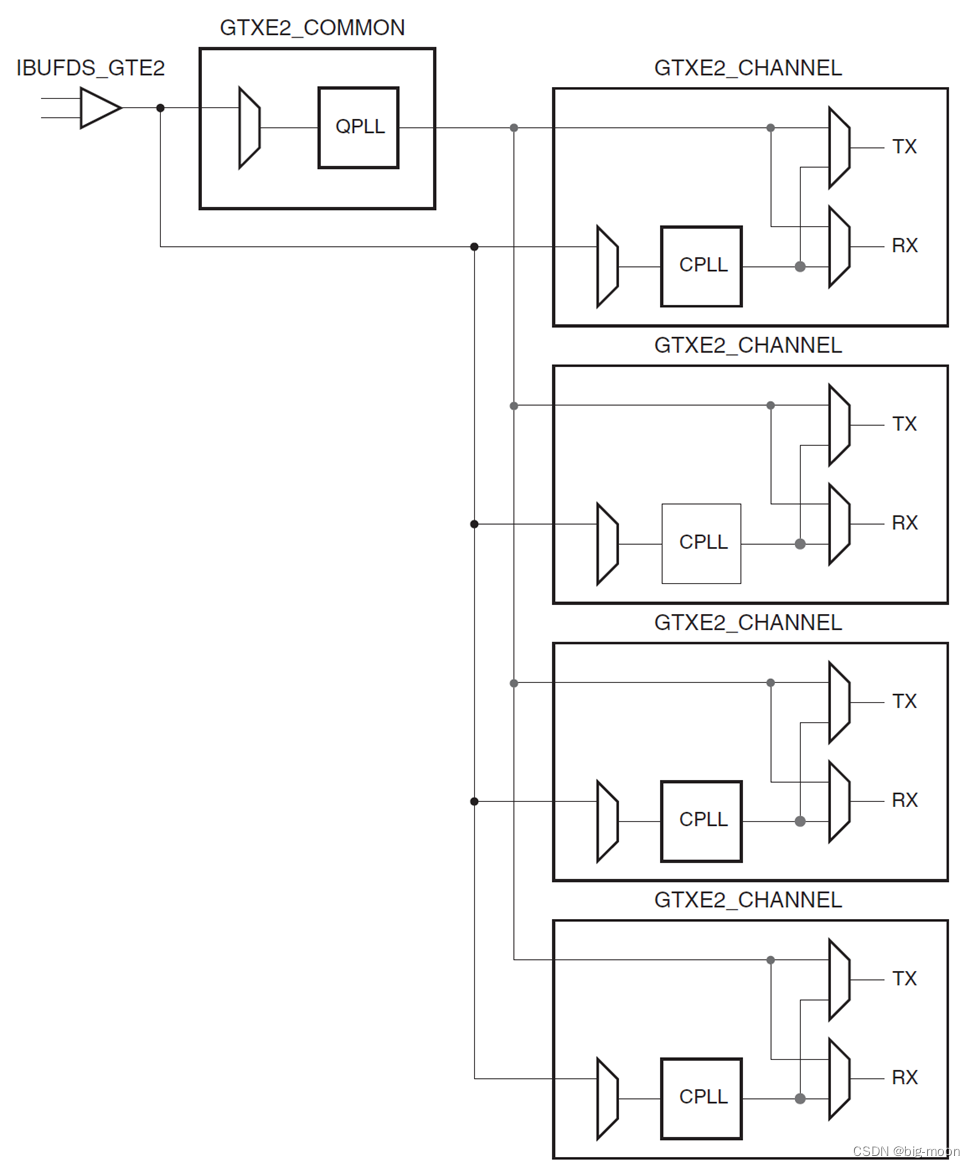

为了更方便理解,本文通过UG476中的芯片XC7K325T来进行举例,该芯片中收发器的内部结构如下图所示。

从图中可以看出,该器件具备

4个Quad(GTXE2_COMMON X0Y0~ GTXE2_COMMON X0Y3),

每个Quad中具有四个通道。共16个通道(GTXE2_CHANNEL X0Y0~ GTXE2_CHANNEL X0Y3,

GTXE2_CHANNEL X0Y4~ GTXE2_CHANNEL X0Y7,

GTXE2_CHANNEL X0Y8~ GTXE2_CHANNEL X0Y11,

GTXE2_CHANNEL X0Y12~ GTXE2_CHANNEL X0Y15),

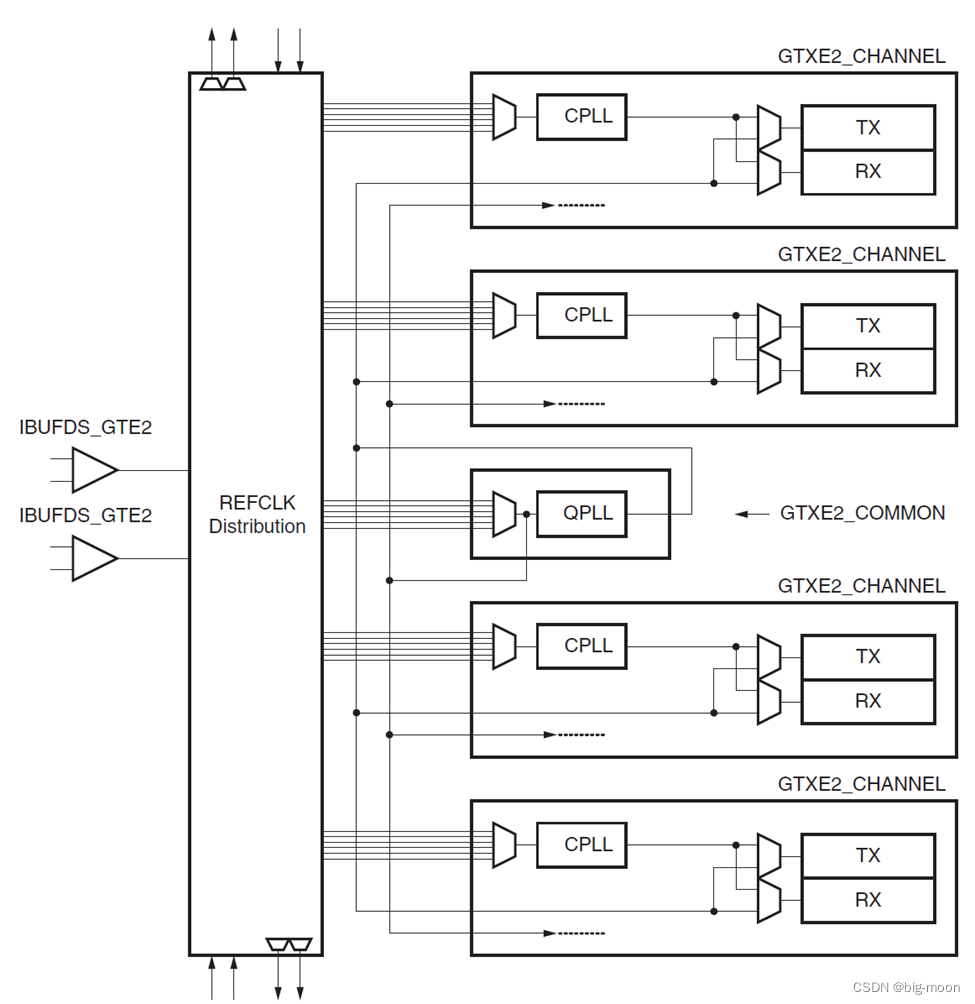

选择其中一个Quad来进行详细说明,单个的Quad如下图所示。

由图可以看出,每个Quad中包含了四组GTXE2_CHANNEL原语和一个GTXE2_COMMON原语。从连接关系上可以看出,CPLL分别对应一个收发模块,对应Channel PLL,而QPLL可以为该Quad中的所有收发提供PLL,对应Quad PLL(这样理解起来应该会容易很多)。由于涉及到原语操作,首先对GTXE2_CHANNEL的原语结构进行剖析,结构图如下所示。

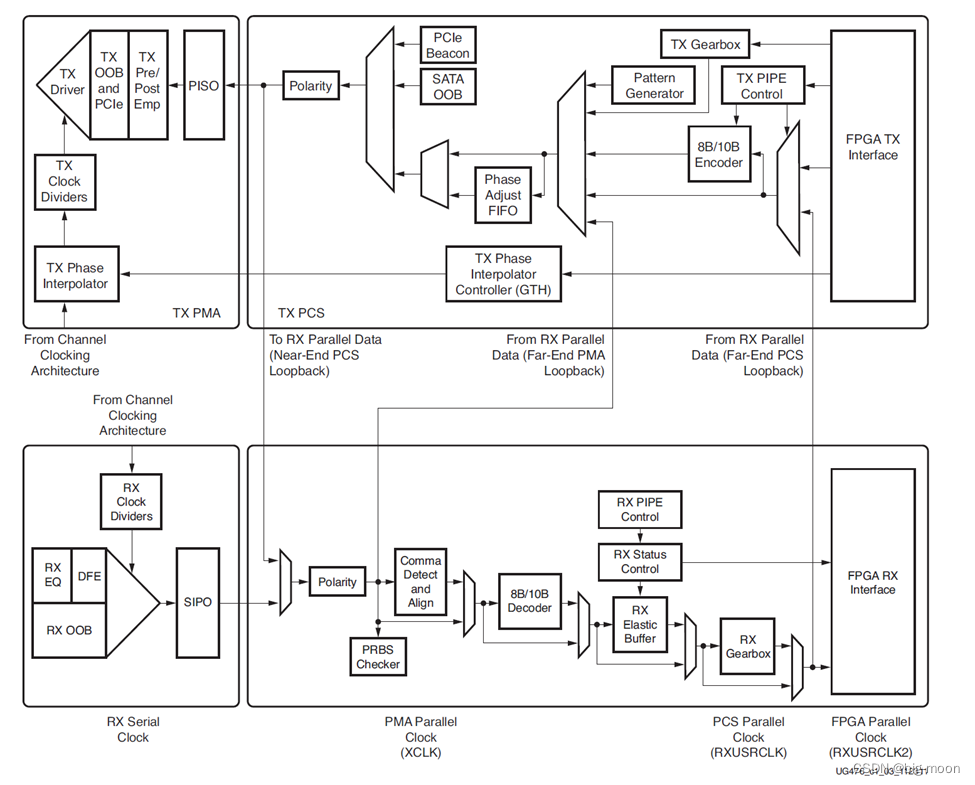

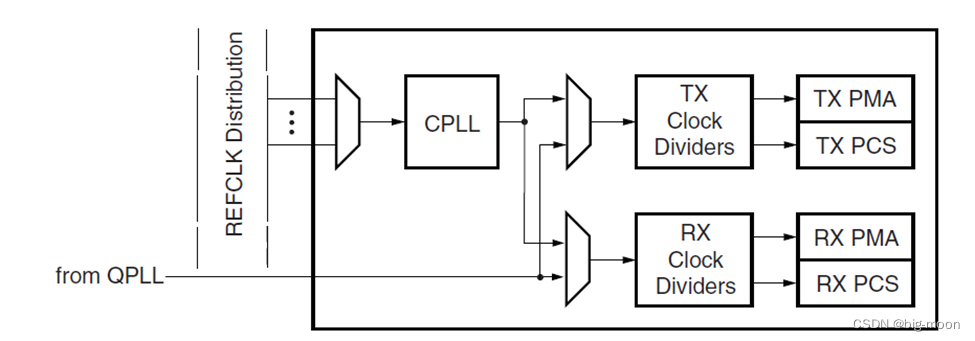

由图可以看出,每个GTXE2_CHANNEL原语由FPGA发射接口、FPGA接收接口以及通道PLL组成。从数据流向可以看出,此时的FPGA发送端口将数据发送出来后先经过PCS(物理编码子层)——>PMA(物理媒介适配层),FPGA接收端口的接收顺序是PMA——>PCS。其中PCS主要包括线路编码和CRC校验编码,PMA主要用于串行化和解串。对于单个Quad来说,原语例化时的示意图如下图所示。

由图可以看出,通过QPLL或者CPLL提供PLL均可,根据不同的原语设置即可。

由于涉及到QPLL和CPLL两个选项,所以在使用时,接收和发送的时钟可以通过QPLL获取也可以通过CPLL获取,示意图如下所示。

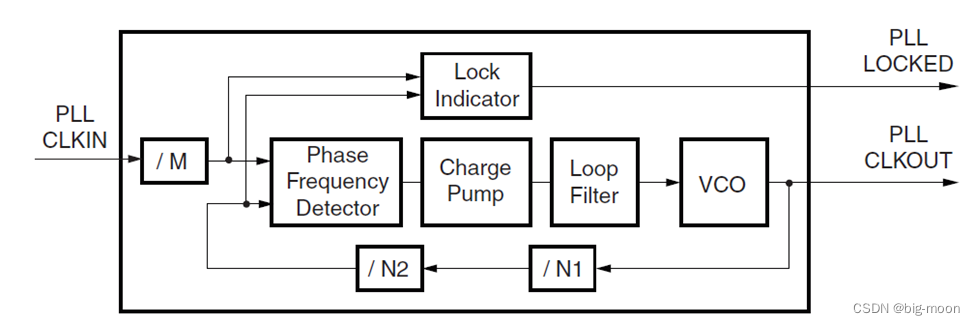

CPLL的内部框图如下所示

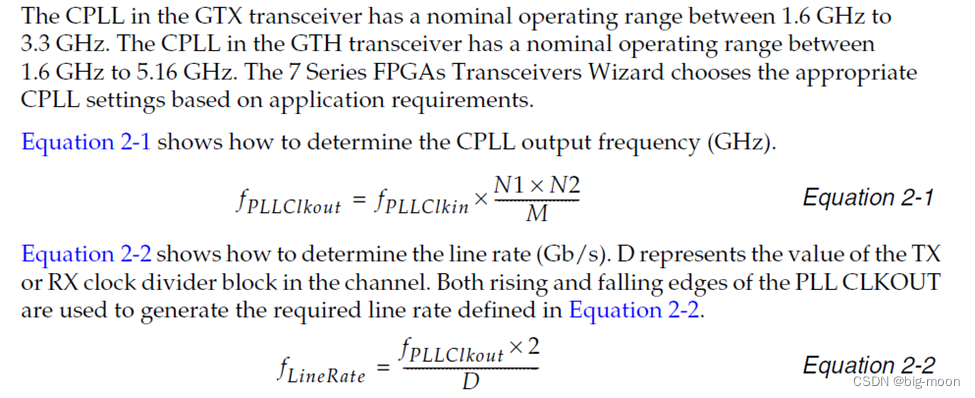

相关的数值计算公式如下,这段就不翻译了,直接截图表示。

相关的数值计算公式如下,这段就不翻译了,直接截图表示。

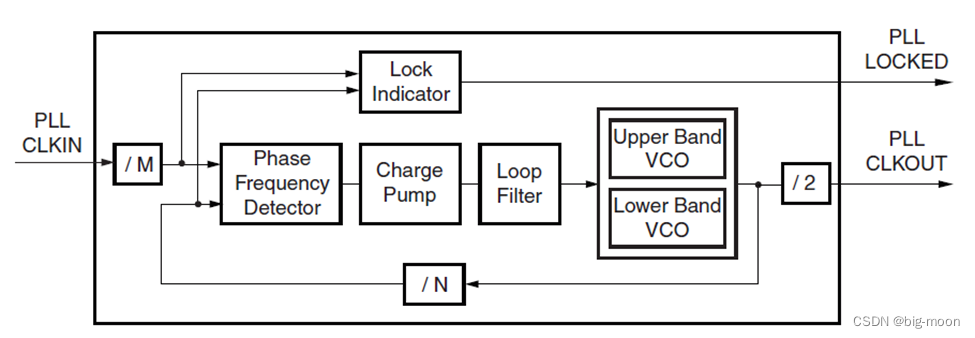

QPLL的内部框图如下所示

QPLL的内部框图如下所示

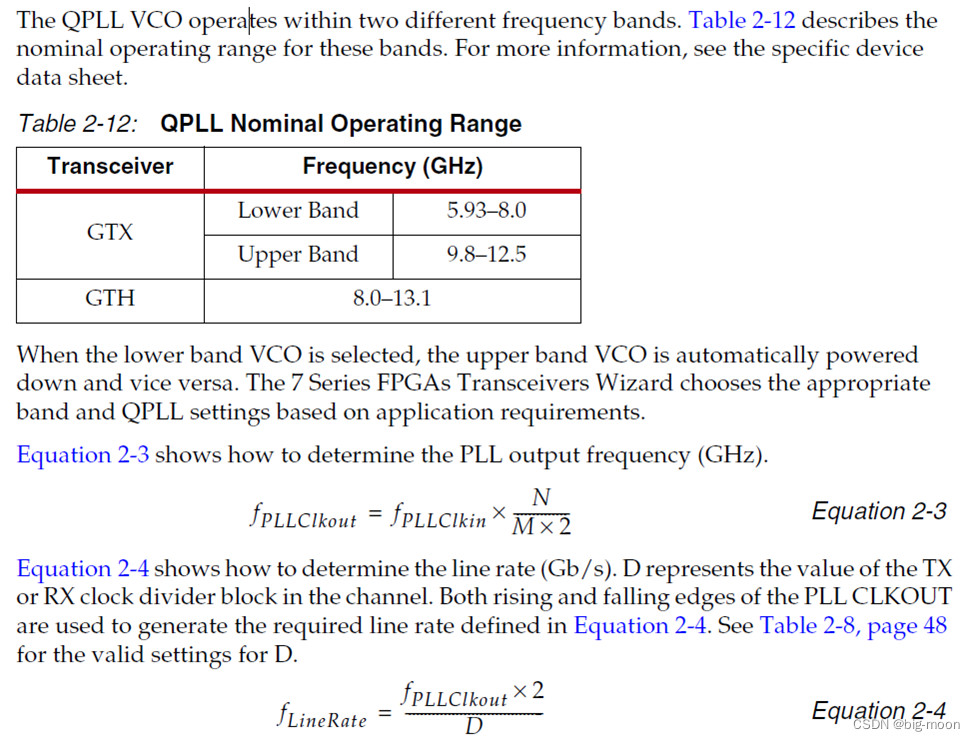

相关的数值计算同样不进行翻译,简单看看公式了解一下就行。

针对这个IP核还存在很多内容,这篇文章先写到这里,后续的内容后面继续补充。如果想要更深刻理解,笔者还是建议自己仔细研读一下文章,毕竟博客只是让读者更快的大概了解文档内容。觉得不错的话点歌收藏和赞把。