逻辑函数及其描述工具

1、根据布尔表达式绘制电路

任务描述

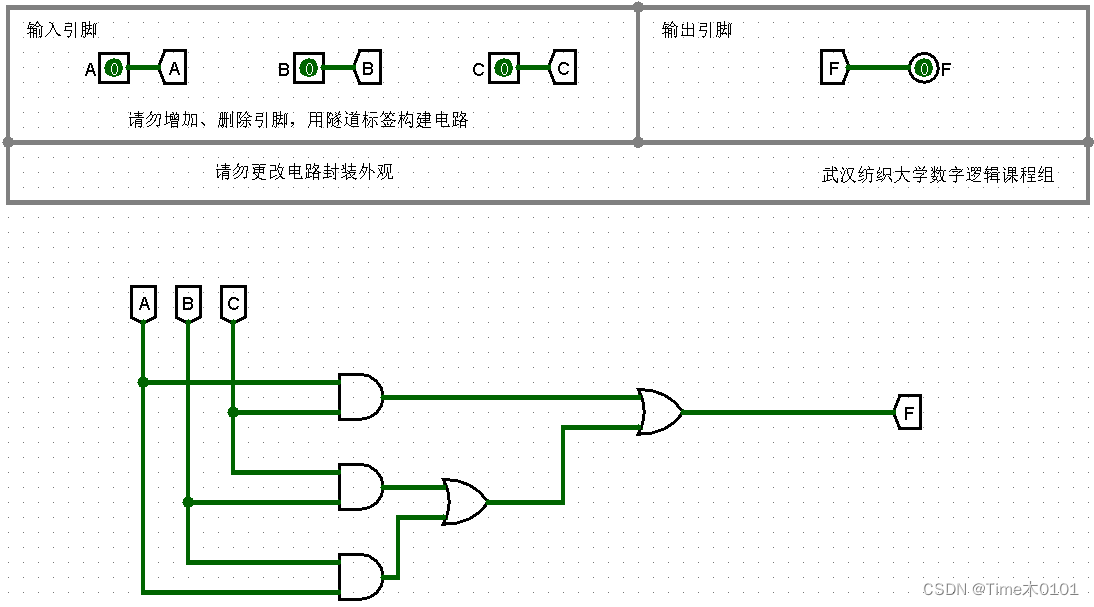

本关任务:在Logisim中根据给定的布尔代数表达式(F=AB+BC+CA)绘制逻辑电路。

案例场景举例

举重比赛裁判电路。在举重比赛中,通常有三位裁判(A、B、C)对运动员的试举是否成功进行裁决,当有两位或三位裁判判定试举成功则该运动员试举成功(F)并获得此次试举的重量记录。

相关知识

为了完成本关任务,你需要掌握:

1.基本逻辑门的使用:与、或、非;

2.Logisim的基本操作。

2、根据真值表绘制电路

任务描述

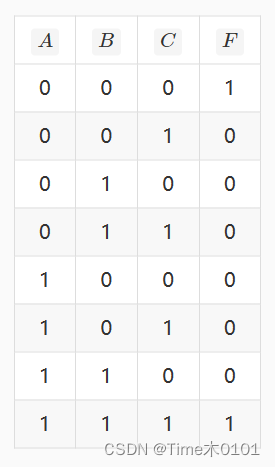

本关任务:根据如下给定的真值表绘制逻辑电路,其中A、B、C是输入变量,F是输出变量。

案例场景举例

一致性电路。当多人(以3人A、B、C为例)进行表决,当大家意见完全一致时通过决议,此时F=1。

相关知识

为了完成本关任务,你需要掌握:

1.逻辑代数中真值表的概念;

2.根据真值表写出逻辑函数的正则积之和表达式(标准与或表达式)或者正则和之积(标准或与表达式)。

实验内容

实验电路框架与第一关相同!子电路:真值表

在Logisim中打开实验电路框架LogicFuncTools.circ,在“真值表”子电路中,根据给定的真值表绘制电路,并进行测试。

解题过程:

直接画卡诺图化简:F=(A+B+C)'+ABC

3、根据简化真值表绘制电路

任务描述

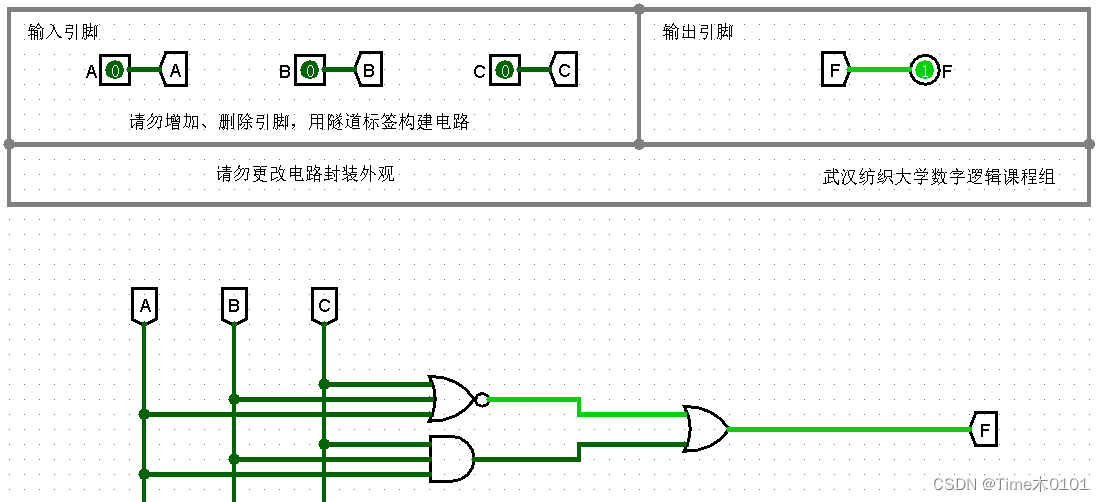

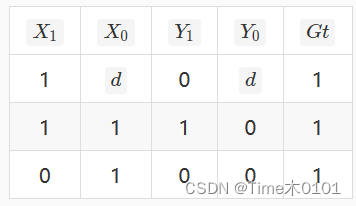

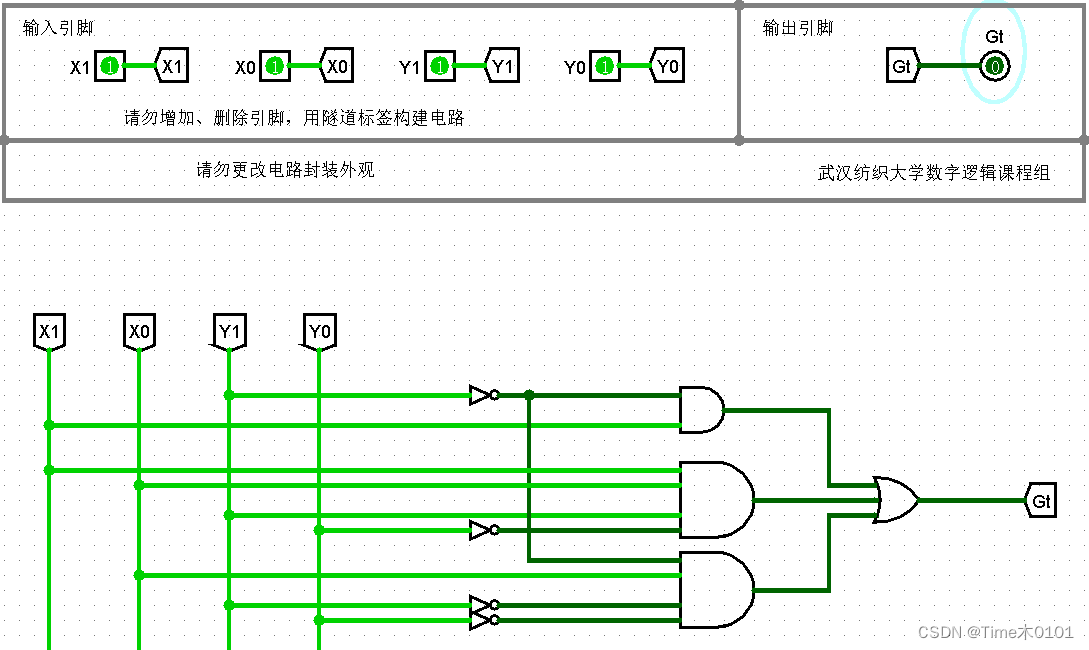

本关任务:根据如下简化真值表,写出Gt的表达式并绘制电路。

案例场景举例

已知X和Y是两个2位的二进制整数,写出判别X>Y的逻辑表达式并绘制逻辑电路。

相关知识

为了完成本关任务,你需要掌握:

1.简化真值表的概念;

2.根据简化真值表写出逻辑函数的与或表达式;

3.普通代数变量与逻辑变量的差异;

4.关系表达式与逻辑表达式的区别。

实验内容

实验电路框架与第一关相同!子电路:简化真值表

在Logisim中打开实验电路框架LogicFuncTools.circ,在“简化真值表”子电路中,根据给定的简化真值表绘制电路,并进行测试。

解题过程:逻辑表达式:Gt=X1Y1’+X1X0Y1Y0+X1’X0Y1’Y0’

4、根据波形图绘制电路

任务描述

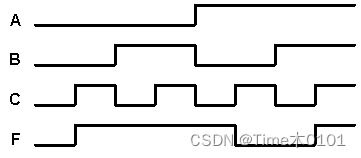

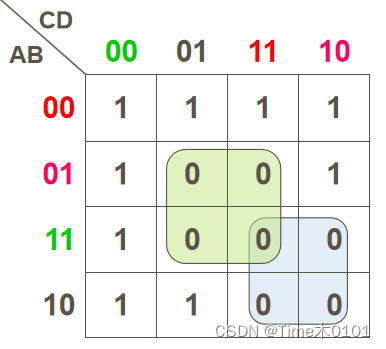

本关任务:根据如下波形图设计并绘制逻辑电路,其中A、B、C为输入信号,F为输出信号。

相关知识

为了完成本关任务,你需要掌握:

1.波形图的概念;

2.根据波形图整理出真值表,然后写出表达式并绘制电路。

实验内容

实验电路框架与第一关相同!子电路:波形图

在Logisim中打开实验电路框架LogicFuncTools.circ,在“波形图”子电路中,根据给定的波形图设计并绘制电路,并进行测试。

解题过程:直接画出卡诺图写出逻辑表达式:F=A’C+A’B+BC+AB’C’

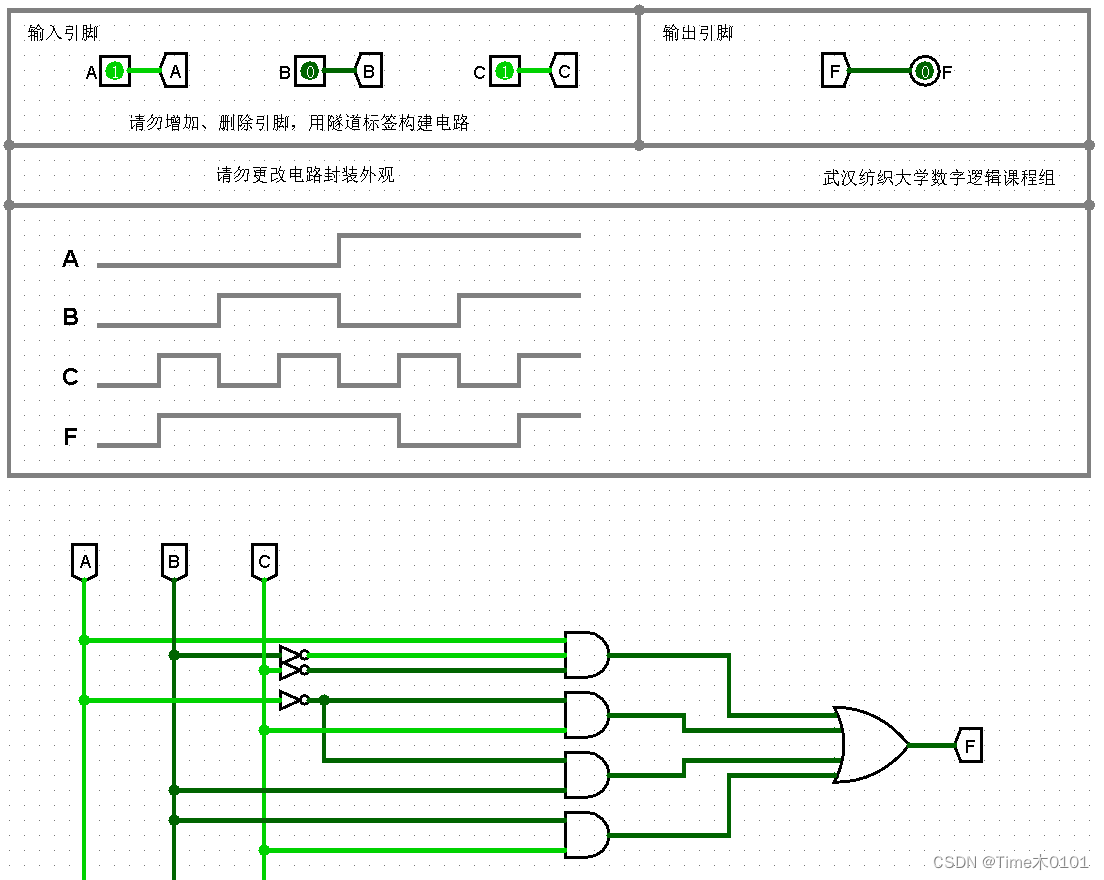

5、根据卡诺图绘制电路

任务描述

本关任务:根据如下卡诺图化简逻辑函数并绘制逻辑电路。

案例场景举例

人类的ABO血型系统有四种基本血型:O、A、B和AB型。O型血可以输给任意血型的人,却只能接受O型; AB型可以接受任意血型,但只能输给AB型;A型能输给A型或AB型,可接受A型或O型; B型能输给B型或AB型,可接受B型或O型。设定:

输入AB表示输送血型,CD表示接受血型;输出为F。

AB的取值是:00表示O型、01表示A型、10表示B型、11表示AB型;

CD的取值为:00表示AB型、01表示B型、10表示A型、11表示O型;

F=1表示可以输血。

相关知识

为了完成本关任务,你需要掌握:

1.卡诺图的概念;

2.根据卡诺图化简逻辑函数,写出函数的最简与或表达式或者最简或与表达式。

实验内容

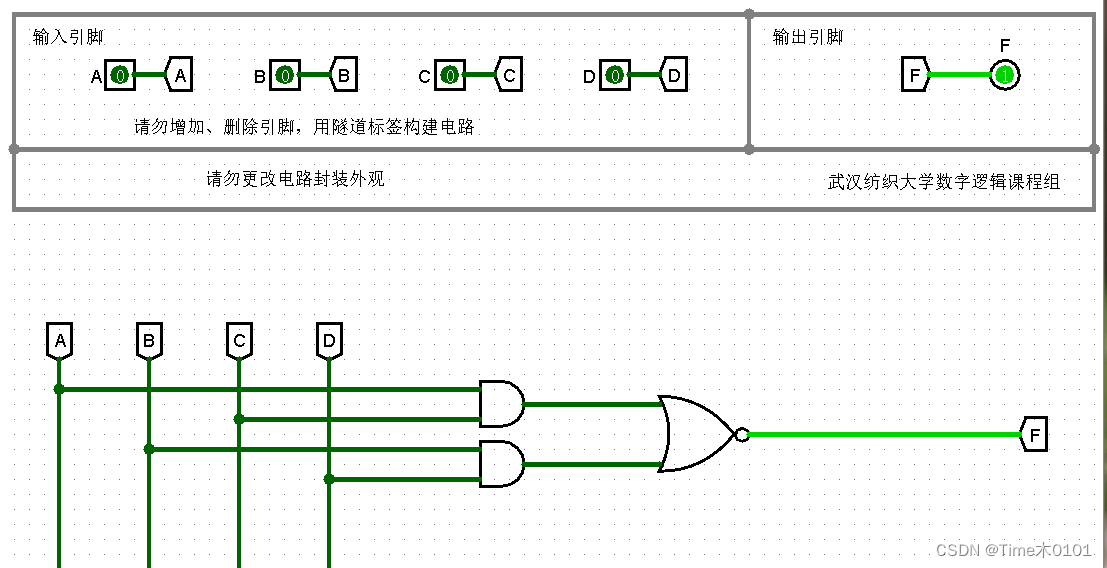

实验电路框架与第一关相同!子电路:卡诺图

在Logisim中打开实验电路框架LogicFuncTools.circ,在“卡诺图”子电路中,根据给定的卡诺图化简逻辑函数并绘制电路,然后进行测试。

测试说明

请用记事本或者纯文本编辑器打开本地设计完成的电路文件(LogicFuncTools.circ),全选(Ctrl+A)、复制(Ctrl+C),然后在本页面代码区中全选(Ctrl+A)、粘贴(Ctrl+V),点击右下方的“评测”按钮,平台会对你的电路代码进行测试。

实验过程:

1、首先根据卡诺图化简最简表达式:

图中圈0所以表达式为:F‘=(AC)+(B+D)

这里先不用取反变为F,直接画电路图。

组合逻辑设计

3-1加法器设计

1、半加器设计

任务描述

本关任务:利用在Logisim中的“组合逻辑分析”工具自动生成半加器电路。

相关知识

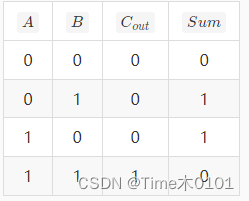

半加器电路是指对两个输入的二进制数据位A、B相加(没有进位输入),输出和Sum与进位Cout ,是实现两个一位二进制数的加法运算电路。真值表如下:

逻辑表达式如下:

S u m = A ⊕ B ; C o u t = A B Sum = A \oplus B;Cout = AB Sum=A⊕B;Cout=AB

实验内容

实验电路框架Adder.circ下载:

方法一:鼠标右击右侧代码区,Download File,

方法二:点我

在Logisim中打开实验电路框架,在工程中的“半加器自动生成”子电路中,启动“组合逻辑分析”工具,操作如下图

鼠标点击填写真值表,如下图

完成真值表后,点击“生成电路”按钮即可!

注:logisim的使用练习,根据真值表自动生成的电路,相关电路逻辑的熟悉,没有作详细记录

2、全加器设计

任务描述

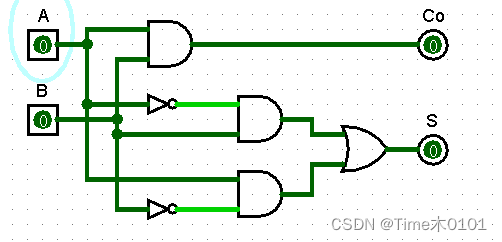

本关任务:请根据教材中的全加器原理图在Logisim中手工绘制全加器电路。

相关知识

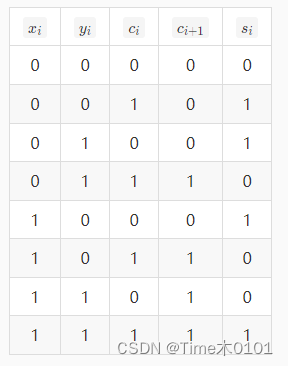

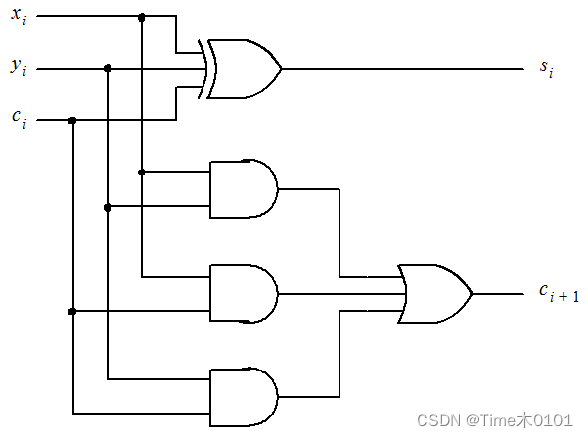

全加器FA(Full Adder)是实现两个1位二进制数(x i 、y i )和来自低位进位(c i)相加,产生和(s

i )与进位输出(c i+1 )的组合逻辑电路。真值表如下:

全加器的逻辑表达式如下:

s = ∑ m ( 1 , 2 , 4 , 7 ) = x i ⊕ y i ⊕ c i s = \sum m(1,2,4,7) = x_i \oplus y_i \oplus c_i s=∑m(1,2,4,7)=xi⊕yi⊕ci

c i + 1 = ∑ m ( 3 , 5 , 6 , 7 ) = x i y i + x i c i + y i c i = x i y i + ( x i ⊕ y i ) c i c_{i+1} = \sum m(3,5,6,7) = x_iy_i + x_ic_i + y_ic_i = x_iy_i + (x_i \oplus y_i)c_i ci+1=∑m(3,5,6,7)=xiyi+xici+yici=xiyi+(xi⊕yi)ci

电路原理图如下:

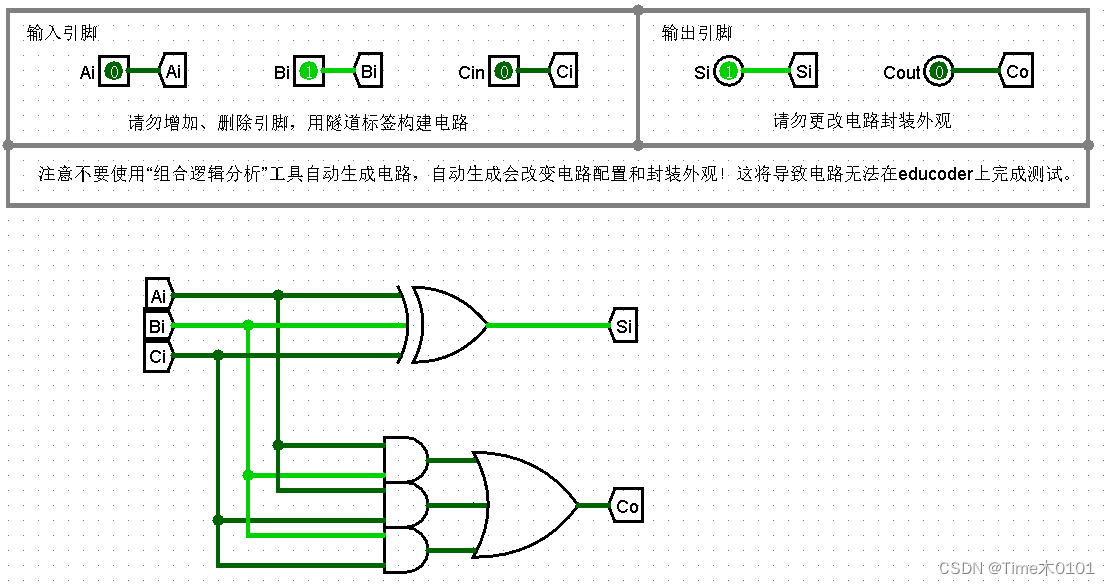

实验内容

实验电路框架与第一关相同。

在Logisim中打开实验电路框架,在工程中的“手绘全加器”子电路中绘制全加器电路。

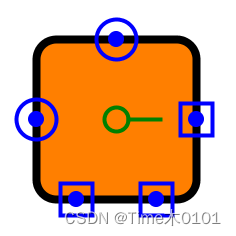

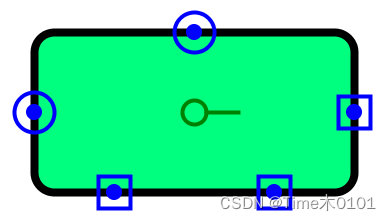

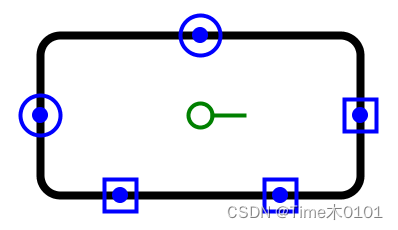

子电路封装外观

子电路封装外观如下图所示,请不要改变引脚位置,否则无法完成测试!

测试说明

请用记事本或者其他纯文本编辑器打开电路文件(Adder.circ),全选、复制,然后粘贴到代码窗口中,点击右下方的“评测”按钮,平台会对你的代码进行测试。

根据表达式直接绘制电路

根据要求改变封装引脚位置

3、行波进位加法器设计

任务描述

本关任务:在Logisim中,利用上一关设计的全加器FA级联设计一个4位的行波进位加法器。

相关知识

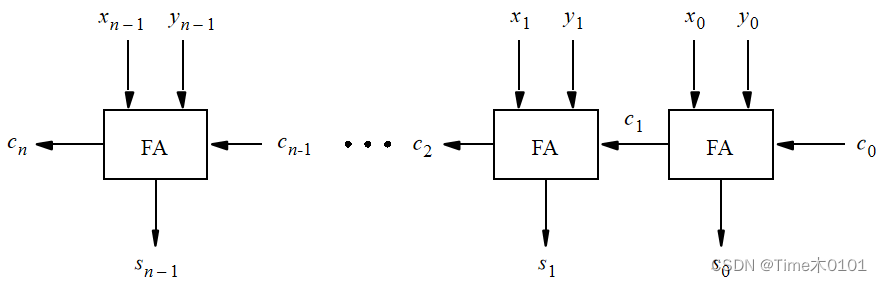

行波进位是指进位信号从低位逐位向高位传递,特点是结构简单,但速度比较慢。原理示意图如下:

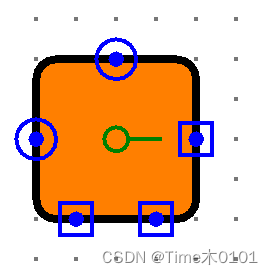

子电路封装外观

请勿移动引脚位置,否则无法完成测试!

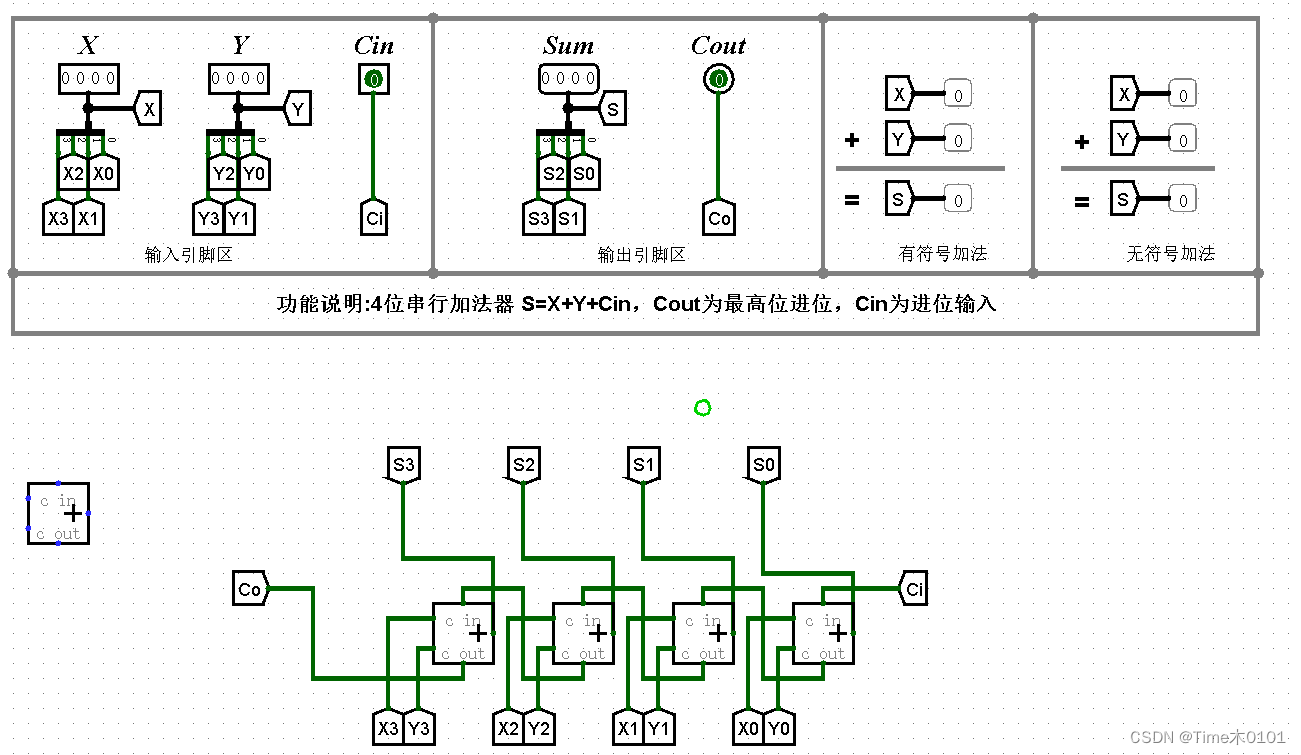

实验内容

实验电路框架与第一关相同。

在Logisim中打开实验电路框架,在工程中的“4位行波进位加法器”子电路中,利用全加器模块级联设计一个4位的加法器。

测试说明

请用记事本或者其他纯文本编辑器打开电路文件(Adder.circ),全选、复制,然后粘贴到代码窗口中,点击右下方的“评测”按钮,平台会对你的代码进行测试。

4、1位十进制加法器设计

任务描述

本关任务:在Logisim中,利用上一关的4位加法器来设计一个1位十进制数(8421BCD)加法器电路。

相关知识

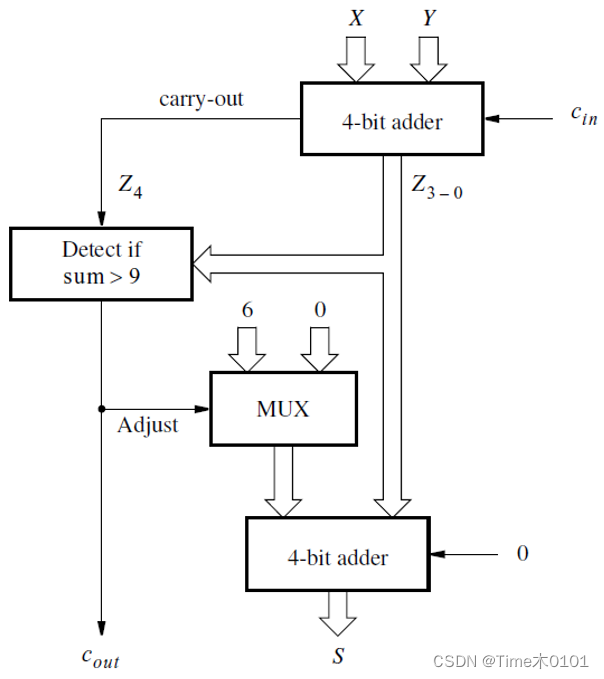

BCD码加法原理

1位十进制数(8421BCD码)加法原理图如下:

修正逻辑设计

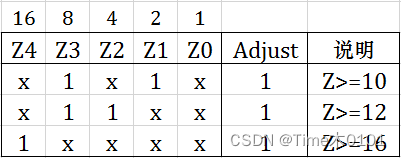

第一次相加的结果Z大于9的判断:

简化真值表如下:

表达式: A d j u s t = Z 4 + Z 3 Z 2 + Z 3 Z 1 表达式:Adjust = Z_4+Z_3Z_2+Z_3Z_1 表达式:Adjust=Z4+Z3Z2+Z3Z1

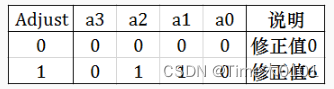

修正值0或6的生成逻辑

真值表如下:

表达式: a 3 = a 0 = 0 ; a 2 = a 1 = A d j u s t 表达式:a_3 = a_0 = 0;a_2 = a_1 = Adjust 表达式:a3=a0=0;a2=a1=Adjust

子电路封装外观

请勿移动引脚位置,否则无法完成电路测试!

实验内容

实验电路框架与第一关相同。

在Logisim中打开实验电路框架,在工程中的“1位十进制加法器”子电路中,利用4位加法器和适当的门电路来设计完成1位BCD码加法器电路。

本实验要用到线路库(Wiring)中的“分线器(Splitter)”!

本实验禁止使用比较器和多路选择器MUX!

拓展设计建议

完成上述实验后,可以在本地尝试多位十进制加法器设计、8421码到余3码的转换电路设计等。

测试说明

请用记事本或者其他纯文本编辑器打开电路文件(Adder.circ),全选、复制,然后粘贴到代码窗口中,点击右下方的“评测”按钮,平台会对你的代码进行测试。