跟着Xilinx学习FPGA——Power Management Techniques电源管理技术

目标:01描述你的设计的功耗是如何依赖于你使用的控制信号;02解释一些常见的设计技术和HDL编码技术如何提高设计的功耗;03使用架构特性来改善设计的功耗

文章目录

前言

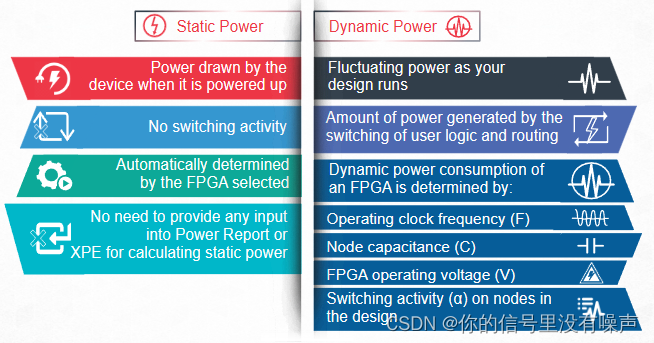

在讨论活动率之前,让我们先了解一下静态功率和动态功率。

设备的静态功率,也称为静态功率,是设备上电时所消耗的功率。另一方面,动态功率是设计运行时的波动功率。在静态功率中,没有交换活动,而动态功率表示用户逻辑和路由交换产生的功率量。静态功率由所选FPGA自动确定。您不必为Power Report或XPE提供任何输入来计算静态功耗。相比之下,FPGA的动态功耗由设计中各个节点的工作时钟频率(f)、节点电容©、FPGA工作电压(√)和开关活动(a)决定。这种转换活动是根据活动速率来测量的。

一、降低功耗

功耗可以通过减小设计尺寸和开关活动来降低。您可以减小设计尺寸:

- 通过减少设计使用的逻辑和路由资源

- 通过管理使用哪些逻辑资源

- 通过实例化和正确推断从选定的FPGA架构的最佳设计资源

- 通过管理您的设计使用的控制信号通过使用最好的HDL编码技术

- 不要盲目相信你的合成结果

- 通过分析和管理这些结果

二、使用硬核降低功耗

我们建议尽可能多地使用硬IP块。这些硬IP块经过了良好的测试,与LUT和触发器实现相比,它们节省了大量资源。它们通过使用最小晶体管数来减少静电。它们还通过使用金属互连而不是金属和可编程互连以及减少走线长度来降低动态功率。此外,这些硬IP块使您能够移动到更小的设备上,从而节省大量电力。但是,作为用户,您必须充分了解在您的设计中要使用哪个硬IP以及如何使用它,否则,它可能不会节省电力。例如:如果您正在使用DSP片执行算术运算,那么使用硬IP还是软IP是否更节能将取决于您将在DSP片中实现的算术运算有多大。

您将需要执行至少两个12位数字的加法,以节省使用硬IP的任何电源。在使用硬IP时,您可以考虑的另一件事是移动到更小的设备上以节省电力。

如果你想减少逻辑,你可以使用更小的设备:

- 通过对逻辑函数进行时间切片,从而使频率加倍,

- 将逻辑减少一半通过将功能转移到专用硬件资源,

状态机→块ram

计数器→DSP48

寄存器 →SRL

CEs→BUFGCEs etc .

三、功率约束

与其他类型的约束一样,功率约束为合成和放置-布线工具提供了方向。基于这些限制,工具将尝试找到同时满足位置、定时和功率引导的最佳解决方案。

功率约束是描述物理操作环境和目标条件的一类或一组约束。这一组包括描述器件将运行的环境温度的约束条件——“theta JA”(热量在硅和环境之间移动的速率)、最大结温、硅工艺类型和其他术语。并非所有术语都是必需的,但设计师越具体,设计就越有可能成功。最关键的术语之一是总设计功率预算。这些工具包含一个功率估计器,在通用ACAP电源和电路板设计课程中有更全面的描述。下面是一些权力限制的例子。第一个例子告诉工具操作环境是50摄氏度。操作环境越冷,更多的热量可以更快地倾倒到它。下一个例子描述了连接到环境值的θ。该值描述了heab可以从硅中移出并进入环境的速率。此值通常是使用Power Estimator电子表格工具确定的,用于您正在使用的部件系列。该工具考虑了散热器,强制空气冷却和其他因素,以提供准确的值。

最后,设计功率预算是设备允许消耗的最大功率。如果工具的估计值超过这个值,那么运行将失败。

四、降低功耗的tips

这里有一些你可以用来减少能量的策略:

- 减少设计中使用的lut和触发器的数量。这有助于提高设计速度。

- 不要在合成或实现期间过度约束设计。谨慎使用合成选项并促进逻辑复制。

- 尽可能使用6输入LUT,以便将更多的逻辑打包到LUT中。然而,合成工具将添加更多无法删除的管道寄存器。

五、处理控制信号

为了减少路由、路由拥塞和功耗,我们建议在设计中共享尽可能多的控制信号。当您在设计中实例化IP时,这是最适用的。

1、在实例化IP目录中的IP和执行合成优化时,请注意以下事项:

- IP原语的门级连接决定了控制信号的使用。IP目录中可用的一些IP不一定遵循这些指导原则。

- 确保您可以在设计、核心和其他组件之间共享控制信号,特别是时钟启用和复位。

- 合成优化影响控制信号的使用。它可以选择建立一个控制信号进行逻辑优化

- 如果控制信号有高扇出,请注意问题。

- 如果需要,手动实例化BUFGCE或其他原语,以控制哪些资源路由信号。

2、一旦您尽可能多地共享控制信号,请在设计中谨慎使用它们。

这是因为低激活控制信号可能产生次优结果,因为寄存器上的控制端口通常是高激活的

- 使用active-low控制信号会导致:

- 使用了过多的lut和路由

- 在所有较低的叶片水平增加逆变器

- 糟糕的时许和功耗

- 不良设计实践在分层设计和设计重用中的传播

物理综合、设计层次和增量设计实践可以改变原始规范的控制集。全局或逻辑优化合成设置可以选择建立一个额外的控制信号进行逻辑优化。

六、减少时钟和块活动

正如您已经看到的,减少信号上的开关活动可以降低功耗。

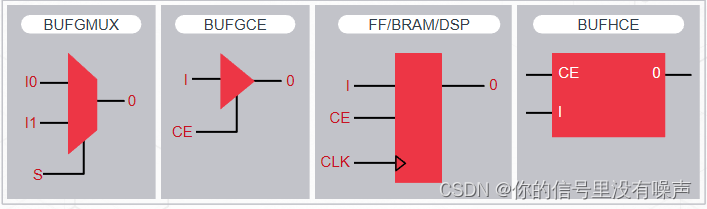

时钟启用缓冲资源可以节省您在一般互连上分配高扇出CE信号的时间。

您必须记住,您的合成工具可能不会推断出这些原语,因此如果您需要它们,您应该使用原理图查看器验证它们的推断,并准备实例化它们以节省电力。为了减少时钟和阻塞切换活动,请在可能的情况下使用BUFGCTRL或BUFGCE关闭时钟。这减少了电路的开关,从而减少了动态功率。使用BUFGCE对时钟进行动态门控,可以节省路由资源使用本地时钟使能消除额外的触发器或阻塞RAM或DSP切换。在不需要时关闭资源,从而节省动态电源。

七、Block_RAM 功率优化

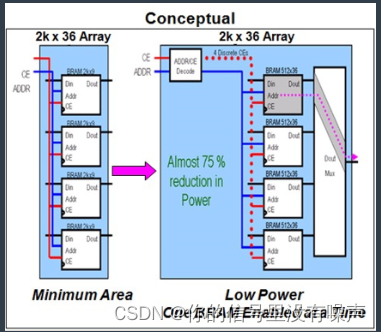

如果使用不当,块RAM会导致大量的功耗。使能率是块RAM功耗的主要因素,而切换活动是次要的。您应该只在活动读或写周期中启用块RAM;否则,它会消耗更多的能量。为“多块RAM”块使用智能架构。如果您需要小内存或乒乓缓冲区,请使用LUTRAM(分布式RAM)。这也可以节省电力。Vivado®Design Suite允许根据您的要求在高性能块RAM结构和低功耗块RAM结构之间进行选择。您可以根据所需内存的尺寸构建块RAM。不要建立一个总是被激活的记忆。

例如,在本例中,确保只有一个块ram被激活。这可以使该内存的动态功耗降低75%。

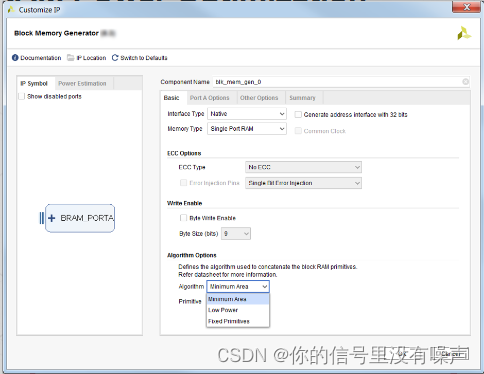

使用IP目录中的块RAM内存生成器。这个块内存生成器可以很容易地选择低功耗选项。

总结

- 减少设计中用于控制功耗的逻辑和路由资源

- 将功能移动到专用硬件资源

- 计划共享尽可能多的控制信号

- 使用BUFGCE对时钟进行动态门控

- 使用本地时钟使能消除额外的触发器、块RAM或DSP切换