and,or,xor,add,sub

sll,srl

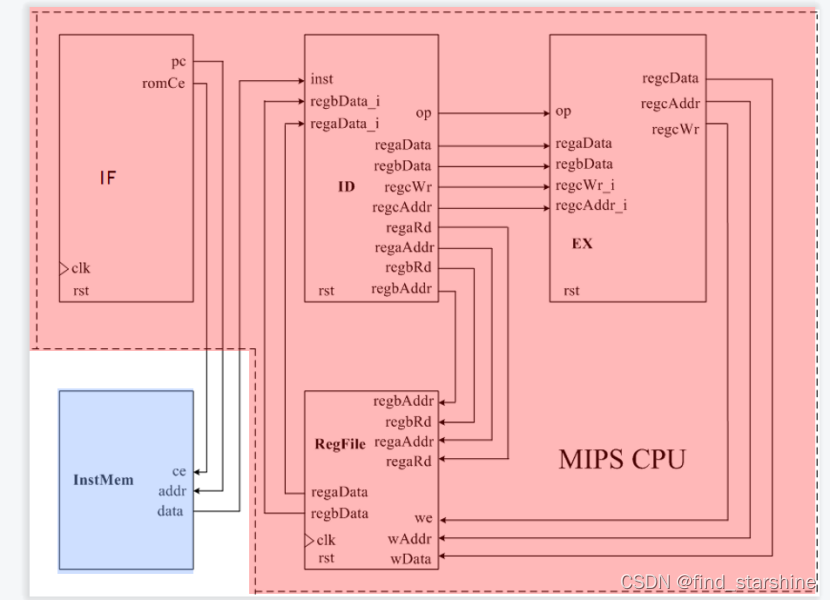

1、各个模块的作用

- IF是取指模块(instruction Fetch)

- ID是译码模块

- InstMem是指存模块(指令存储器)模块,是一个ROM芯片

- Regfile是寄存器堆

- EX模块是执行指令,包括写指令(用来做运算,可以认为是ALU)。

2、整体流程结构

① IF模块将指令地址pc和片选信号romce送入指存模块InstMem,从InstMem模块中取出指令数据由data脚送入ID模块的inst脚。

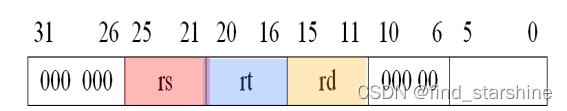

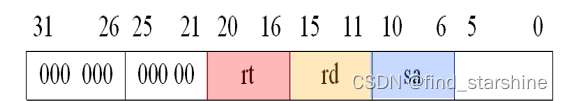

② ID模块将送入的inst进行译码,ID将源寄存器rs的地址给regAaddr,将源寄存器rt的地址给regBaddr,将目的寄存器地址给regCaddr,将ID模块中的regAaddr和regAread(读信号)送给Regfile模块,以及将ID模块中的regBaddr和regBread(读信号)送给Regfile模块,然后读取Regfile模块中的regAdata和regBdata,将regAdata和regBdata送给ID模块中的regadata_i和regbdata_i,作为ID模块中的regAdata和regBdata送给EX模块。

③ ID模块读取数据完成后,将数据regAdata,regBdata,regCaddr,regCwr(写信号),op(操作码,用来决定将进行何种操作) 送给EX模块。EX模块获得数据和操作码后进行运算,运算后的结果保存到regCdata中,EX模块将regCdata,regCaddr和regCwr写入Regfile模块,将数据写入寄存器堆保存起来。

3、各个模块对应代码

1、InstMem模块

// R rs rt rd

instmem [0] = 32'h00214020; //r1+r1->r8 add 000000_00001_00001_01000_00000_100000

instmem [1] = 32'h00832022; //r4-r3->r4 sub 000000_00100_00011_00100_00000_100010

instmem [2] = 32'h00431024; //r2&r3->r2 and 000000_00010_00011_00010_00000_100100

instmem [3] = 32'h00214025; //r1|r1->r8 or 000000_00001_00001_01000_00000_100101

instmem [4] = 32'h00431026; //r2^r3->r2 xor 000000_00010_00011_00010_00000_100110

instmem [5] = 32'h00011040; //r2<-r1<<1 sll 000000_00000_00001_00010_00001_000000

instmem [6] = 32'h00043842; //r7<-r4>>1 srl 000000_00000_00100_00111_00001_000010

2、EX模块

`Add:

regcData = regaData + regbData;

`Sub:

regcData = regaData - regbData;

`And:

regcData = regaData & regbData;

`Or:

regcData = regaData | regbData;

`Xor:

regcData = regaData ^ regbData;

`Sll:

regcData = regaData << instruction[10:6];

`Srl:

regcData = regaData >> instruction[10:6];

3、ID模块

wire [5:0] inst_op = inst[31:26];

wire [5:0] func = inst[5:0];

`Inst_r:

case(func)

`Add:

begin

op = `Add;

regaRead = `Valid;

regbRead = `Valid;

regcWrite = `Valid;

regaAddr = inst[25:21];

regbAddr = inst[20:16];

regcAddr = inst[15:11];

imm = `Zero;

end

`Sub:

begin

op = `Sub;

regaRead = `Valid;

regbRead = `Valid;

regcWrite = `Valid;

regaAddr = inst[25:21];

regbAddr = inst[20:16];

regcAddr = inst[15:11];

imm = `Zero;

end

`And:

begin

op = `And;

regaRead = `Valid;

regbRead = `Valid;

regcWrite = `Valid;

regaAddr = inst[25:21];

regbAddr = inst[20:16];

regcAddr = inst[15:11];

imm = `Zero;

end

`Or:

begin

op = `Or;

regaRead = `Valid;

regbRead = `Valid;

regcWrite = `Valid;

regaAddr = inst[25:21];

regbAddr = inst[20:16];

regcAddr = inst[15:11];

imm = `Zero;

end

`Xor:

begin

op = `Xor;

regaRead = `Valid;

regbRead = `Valid;

regcWrite = `Valid;

regaAddr = inst[25:21];

regbAddr = inst[20:16];

regcAddr = inst[15:11];

imm = `Zero;

end

`Sll:

begin

op = `Sll;

regaRead = `Valid;

regbRead = `Invalid;

regcWrite = `Valid;

reg

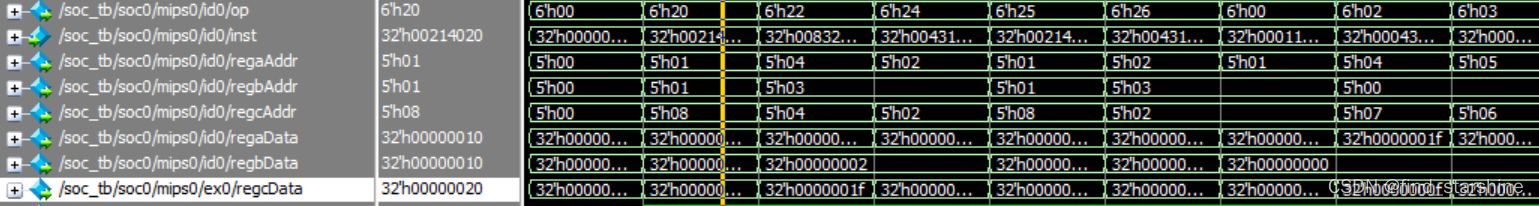

4、仿真结果