上一篇文章讲了RTC,里面其实已经包含了时钟系统的介绍了。这篇文章将再详细的讲一下。

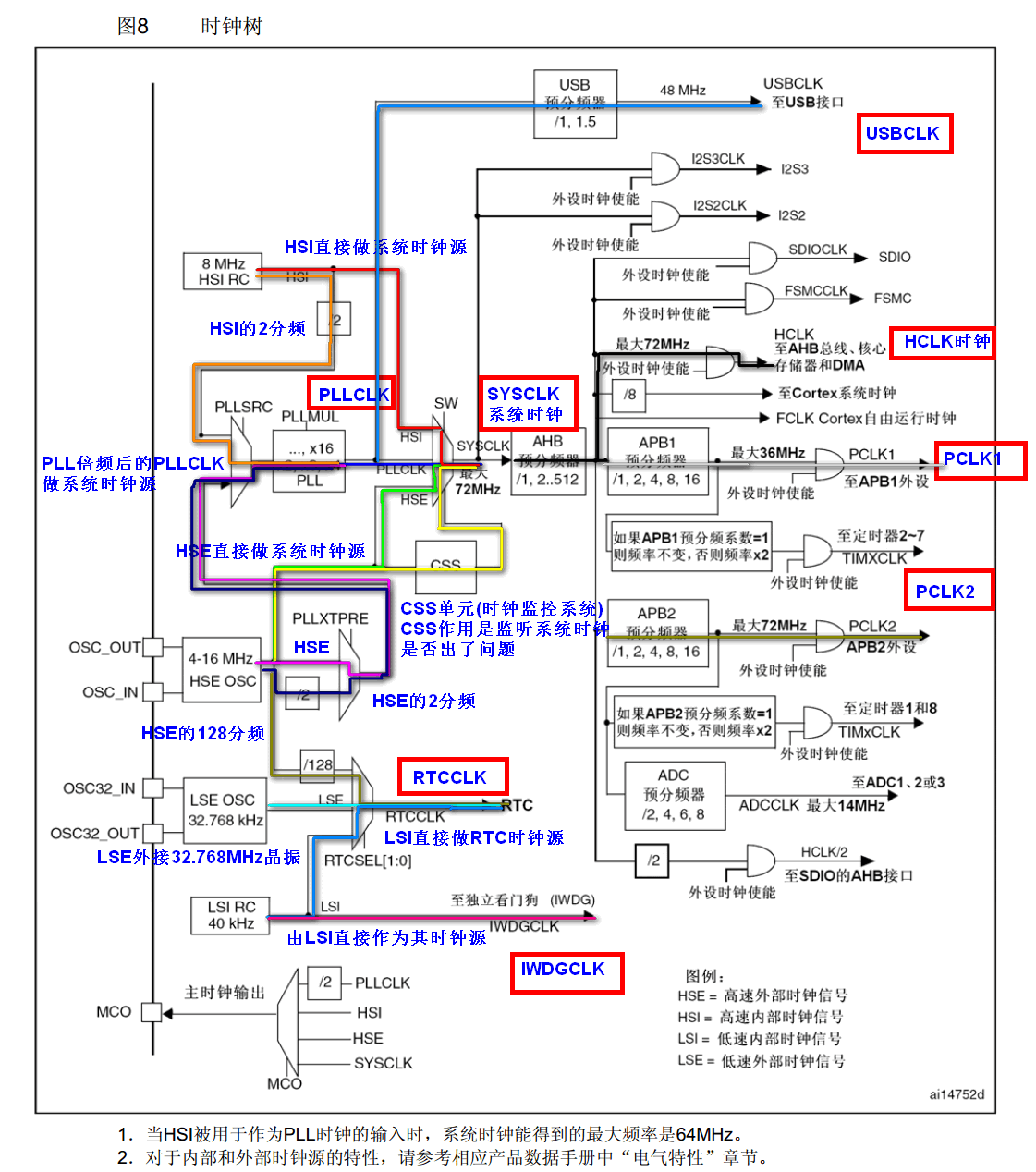

一、时钟系统框图

二、时钟系统

- STM32 有5个时钟源:HSI、HSE、LSI、LSE、PLL。

①、HSI是高速内部时钟,RC振荡器,频率为8MHz,精度不高。

②、HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

③、LSI是低速内部时钟,RC振荡器,频率为40kHz,提供低功耗时钟。

④、LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

⑤、PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。 - 系统时钟SYSCLK可来源于三个时钟源:

①、HSI振荡器时钟

②、HSE振荡器时钟

③、PLL时钟 - STM32可以选择一个时钟信号输出到MCO脚(PA8)上,可以选择为PLL输出的2分频、HSI、HSE、或者系统时钟。

- 任何一个外设在使用之前,必须首先使能其相应的时钟。

三、RCC相关配置寄存器

/**

* @brief Reset and Clock Control

*/

typedef struct

{

__IO uint32_t CR;

__IO uint32_t CFGR;

__IO uint32_t CIR;

__IO uint32_t APB2RSTR;

__IO uint32_t APB1RSTR;

__IO uint32_t AHBENR;

__IO uint32_t APB2ENR;

__IO uint32_t APB1ENR;

__IO uint32_t BDCR;

__IO uint32_t CSR;

#ifdef STM32F10X_CL

__IO uint32_t AHBRSTR;

__IO uint32_t CFGR2;

#endif /* STM32F10X_CL */

#if defined (STM32F10X_LD_VL) || defined (STM32F10X_MD_VL) || defined (STM32F10X_HD_VL)

uint32_t RESERVED0;

__IO uint32_t CFGR2;

#endif /* STM32F10X_LD_VL || STM32F10X_MD_VL || STM32F10X_HD_VL */

} RCC_TypeDef;

四、RCC相关头文件和固件库源文件

所在文件:stm32f10x_rcc.c

时钟使能配置:

RCC_LSEConfig() 、RCC_HSEConfig()、

RCC_HSICmd() 、 RCC_LSICmd() 、 RCC_PLLCmd() ……时钟源相关配置:

RCC_PLLConfig ()、 RCC_SYSCLKConfig() 、

RCC_RTCCLKConfig() …分频系数选择配置:

RCC_HCLKConfig() 、 RCC_PCLK1Config() 、 RCC_PCLK2Config()…外设时钟使能:

RCC_APB1PeriphClockCmd(): //APB1线上外设时钟使能

RCC_APB2PeriphClockCmd(); //APB2线上外设时钟使能

RCC_AHBPeriphClockCmd(); //AHB线上外设时钟使能其他外设时钟配置:

RCC_ADCCLKConfig (); RCC_RTCCLKConfig();状态参数获取参数:

RCC_GetClocksFreq();

RCC_GetSYSCLKSource();

RCC_GetFlagStatus()RCC中断相关函数 :

RCC_ITConfig() 、 RCC_GetITStatus() 、 RCC_ClearITPendingBit()…五、系统时钟初始化函数

系统时钟初始化函数:SystemInit();

我们在 STM32开发 – 启动流程 中讲过:

使用V3.5版本的库函数,该函数在系统启动之后会自动调用:

; Reset handler

Reset_Handler PROC

EXPORT Reset_Handler [WEAK]

IMPORT SystemInit

IMPORT __main

LDR R0, =SystemInit

BLX R0

LDR R0, =__main

BX R0

ENDP在system_stm32f10x.c文件中找到SystemInit(void)源码:

/**

* @brief Setup the microcontroller system

* Initialize the Embedded Flash Interface, the PLL and update the

* SystemCoreClock variable.

* @note This function should be used only after reset.

* @param None

* @retval None

*/

void SystemInit (void)

{

/* Reset the RCC clock configuration to the default reset state(for debug purpose) */

/* Set HSION bit */

RCC->CR |= (uint32_t)0x00000001; //RCC_CR寄存器最低位置1:打开HSI(内部高速时钟8M)

/* Reset SW, HPRE, PPRE1, PPRE2, ADCPRE and MCO bits */

#ifndef STM32F10X_CL

RCC->CFGR &= (uint32_t)0xF8FF0000;

#else //stm32f103ZET6为大容量芯片HD

RCC->CFGR &= (uint32_t)0xF0FF0000; //RCC_CFGR寄存器初始化

#endif /* STM32F10X_CL */

/* Reset HSEON, CSSON and PLLON bits */

RCC->CR &= (uint32_t)0xFEF6FFFF; //将RCC_CR寄存器HSEON,CSSON,PLLON位置0

/* Reset HSEBYP bit */

RCC->CR &= (uint32_t)0xFFFBFFFF; //将RCC_CR寄存器HSEBYP位置0

/* Reset PLLSRC, PLLXTPRE, PLLMUL and USBPRE/OTGFSPRE bits */

RCC->CFGR &= (uint32_t)0xFF80FFFF; //将RCC_CFGR寄存器PLLSRC, PLLXTPRE, //PLLMUL,USBPRE/OTGFSPRE位置0

#ifdef STM32F10X_CL

/* Reset PLL2ON and PLL3ON bits */

RCC->CR &= (uint32_t)0xEBFFFFFF;

/* Disable all interrupts and clear pending bits */

RCC->CIR = 0x00FF0000;

/* Reset CFGR2 register */

RCC->CFGR2 = 0x00000000;

#elif defined (STM32F10X_LD_VL) || defined (STM32F10X_MD_VL) || (defined STM32F10X_HD_VL)

/* Disable all interrupts and clear pending bits */

RCC->CIR = 0x009F0000;

/* Reset CFGR2 register */

RCC->CFGR2 = 0x00000000;

#else //stm32f103ZET6为大容量芯片HD

/* Disable all interrupts and clear pending bits */

RCC->CIR = 0x009F0000; //关闭所有的中断和对应的位(初始化中断)

#endif /* STM32F10X_CL */

#if defined (STM32F10X_HD) || (defined STM32F10X_XL) || (defined STM32F10X_HD_VL)

#ifdef DATA_IN_ExtSRAM

SystemInit_ExtMemCtl();

#endif /* DATA_IN_ExtSRAM */

#endif

/* Configure the System clock frequency, HCLK, PCLK2 and PCLK1 prescalers */

/* Configure the Flash Latency cycles and enable prefetch buffer */

SetSysClock();

#ifdef VECT_TAB_SRAM

SCB->VTOR = SRAM_BASE | VECT_TAB_OFFSET; /* Vector Table Relocation in Internal SRAM. */

#else

SCB->VTOR = FLASH_BASE | VECT_TAB_OFFSET; /* Vector Table Relocation in Internal FLASH. */

#endif

}