1

本实验将实现 FPGA 芯片和 PC 之间进行千兆以太网数据通信, 通信协议采用 Ethernet UDP 通信协议。 FPGA 通过 GMII 总线和开发板上的 Gigabit PHY 芯片通信, Gigabit PHY芯片把数据通过网线发给 PC。在上次的实验中,我们详细讲解了网络传输的过程中如何对数据进行传输,以及数据传输的格式,这次实验中,我们详细讲解如何使用Verilog语言来实现将UDP数据的发送。

以太网数据通信的示意图如下:

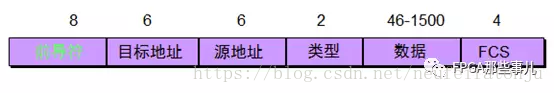

这里我再展示数据传输的格式图片。

其中数据包括三个方面的内容:IPv4数据包头,UDP包头,和用户数据。

IPv4数据包头:

UDP数据包头。

2

在AX515/AX530开发板我们采用了Realtek千兆GPHY芯片RTL8211E 来实现千兆以太网数据通信。当网口 Link 到千兆以太网时, FPGA 通过 GMII 总线和 PHY 芯片进行数据通信,当网口 Link 到百兆以太网时, PGA 通过 MII 总线和 PHY 芯片进行数据通信。 另外 FPGA 可以通过 MDI/MDIO 管理接口来配置或读取 PHY 芯片内部的寄存器。

本实验以千兆以太网 GMII 通信为例来设计 verilog 程序。整个Ethernet_test测试是一个顶层模块,UDP发送模块。我们要发送的数据为Hello World。

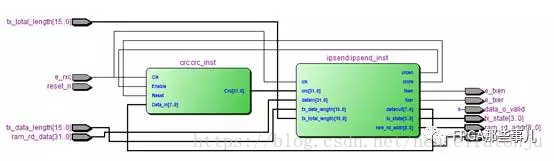

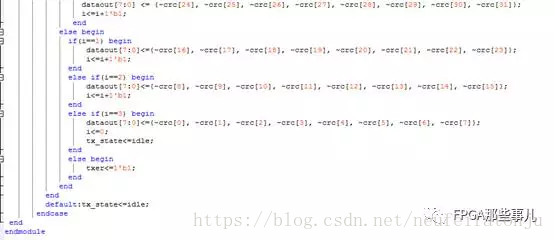

首先我们先实现UDP模块。 UDP模块包括UDP发送模块和CRC校验模块。RTL电路示意图:

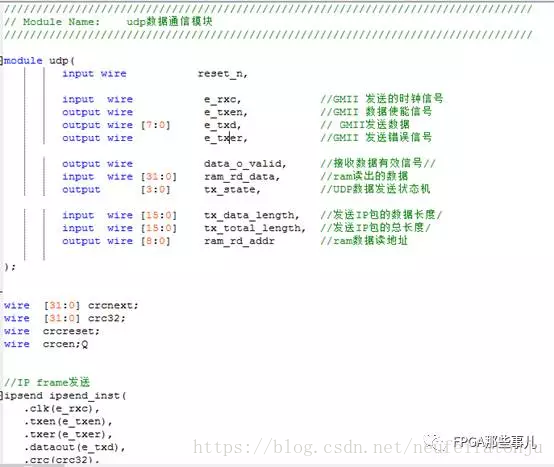

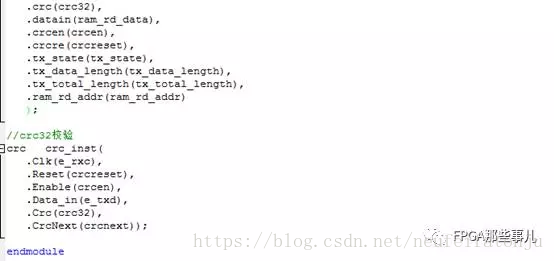

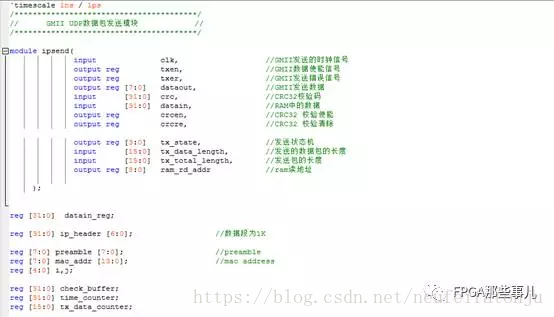

Ipsend模块是UDP发送模块。各个引脚的解释请看各个模块的Verilog代码。代码在下面。UDP发送顶层模块。

UDP发送数据模块。

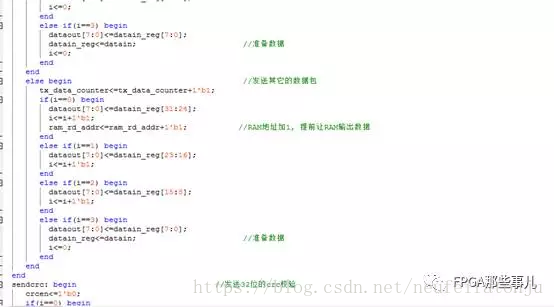

UDP 发送模块实现把 RAM 里的数据组成 UDP IP 包格式通过 GMII 总线发给 PHY 芯片,PHY 芯片再把数据发送到开发板的网口。

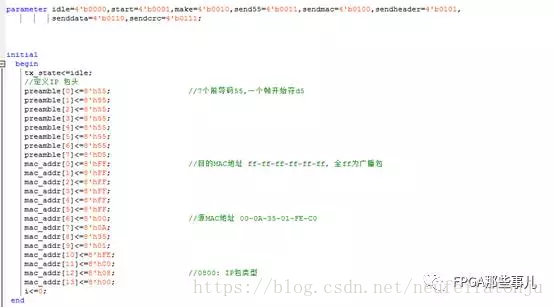

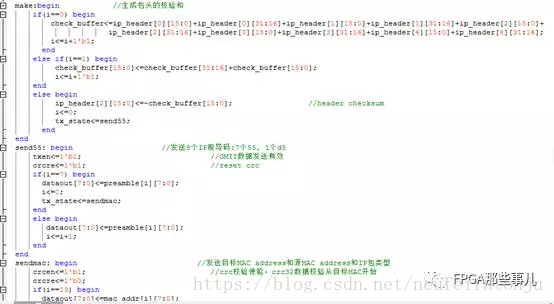

IP 数据包发送之前需要先发送 IP 数据包的包头,IP 包头由 8 个字节的前导码, 目标 MAC Address,源 MAC 地址和两个字节的 IP 包类型组成。前导码是由 7 个 0x55, 1个 0xD5 字节组成, 表示一个IP数据包传输的开始; 目标MAC Address为数据要发送对象的MAC地址,如果开发板的网口是和您的 PC 机相连, 那目标 MAC Address的值为你 PC 机的 MAC 地址。源 MAC Address 是指开发板本地的 MAC 地址。IP 包类型值为 0x0800。

发完 IP 包头之后开始发送 IP 数据报首部,IP 数据报首部的格式我们在前面已经讲过,接着发送 ram中的数据,最后发送 4 个字节的 CRC32 的值。

CRC模块我们不把代码贴出来了,请到最后我提供的链接进行下载。

Ethernet顶层测试模块。

Ethernet顶层设计模块是首先将发送的数据写进ram中,此时ram作为一个缓存,每次发送数据的时候首先需要去读取ram中的数据,将读取ram中的数据读入UDP模块中,然后进行按照数据发送的格式进行发送,每次发送的一帧数据即为Hello World。即为12字节。

3

实验结果:

通过wireshark软件我们抓取Ethernet网络的数据,在wireshark抓包窗口我们可以看到开发板(192.168.0.2)向PC网口(192.168.0.2)发来的数据包,这里会显示数据包的目标MAC, 源MAC,IP包头和UDP包等信息。

千兆以太网的数据传输速度非常快,而且是全双工传输,通过环路测试,UDP 通信的数据速度可以达到 900Mbps 以上,非常适合高速数据传输的场合,比如视频图像传输,高速数据采集等等。

注意:以太网的数据帧的传输有包长的要求, 一般在46~1500字节。所以在发送以太网数据包的时候,数据帧的长度不能太短, 不然会导致PC数据包发送而FPGA收不到数据包的情况。

工程链接地址:链接:http://pan.baidu.com/s/1geWb771 密码:64wf