版权声明:本文为博主原创文章,未经博主允许不得转载。 https://blog.csdn.net/haoxingheng/article/details/41920707

作者:Hello,Panda

1.3 互连接口

PS 对外的互联接口包括: 四个 64bit 高速 AXI_HP Slave 接口,最高时钟为 150MHz;

两个 32bit 低速 AXI_GP Slave 接口和两个 32bit AXI_GP Master 接口;

一个 64bit 低延时 AXI_ACP Slave 接口。

详细的接口介绍及使用见 ZYNQ 内部互联章节。

1.4 PL 资源

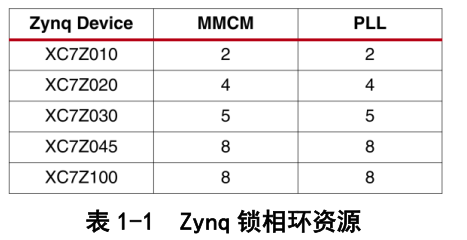

PS 有四个可编程时钟资源提供给 PL,PL 本身还具有锁相环电路及其管理单元(MMCM),下表1-1 是PL锁相环资源情况。

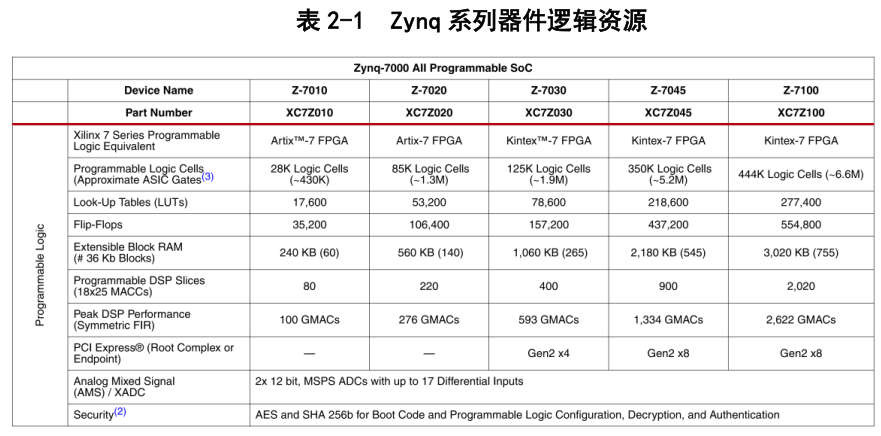

Zynq 系列的 PL 核有 Artix 系列和 Kintex 系列两种,表 2-1 列出了 Zynq 系列器件的逻辑资源情况。

2 ZYNQ 启动加载

Zynq 器件支持加密安全启动和非加密启动,安全启动方式有多级秘钥匹配的过程,相对比较复杂,这里不深究加密启动的方法。启动加载及调试模式等由MIO[8:2]确定,因此,这些 MIO 应该使用 20 kΩ左右的电阻上拉或下拉,使保持确定的低电平或高电平。2.1 上电

Zynq 系列器件对上电时序无严格的要求,只是简单的说明 PS 应先上 VCCPINT、VCCPAUX 和 VCCPLL,再上 VCCO,下电顺序反之。PL 和 PS 类似,也是先上内核和RAM,再上外设,简单的上电顺序控制可通过 DC 模块的 ByMODE 充电容限来设置延迟。表2-1Zynq器件的电源域。

备注:现xilinx已经推出低功耗版本器件-L系列,FL内核和BRAM电压将为0.95V。

好的电源设计有助于提高电源效率,降低功耗、减少发热;降低 CPU启动失败,部分外设发生“莫名”等工作异常的概率,有助于提高电路工作的稳定性;数字电路也应考虑辐射和串扰对模拟域带来的干扰。Zynq器件详细的 AC/DC 参数见DS187 或DS191,PCB设计细节指导见 UG933。

2.2 启动器件选择

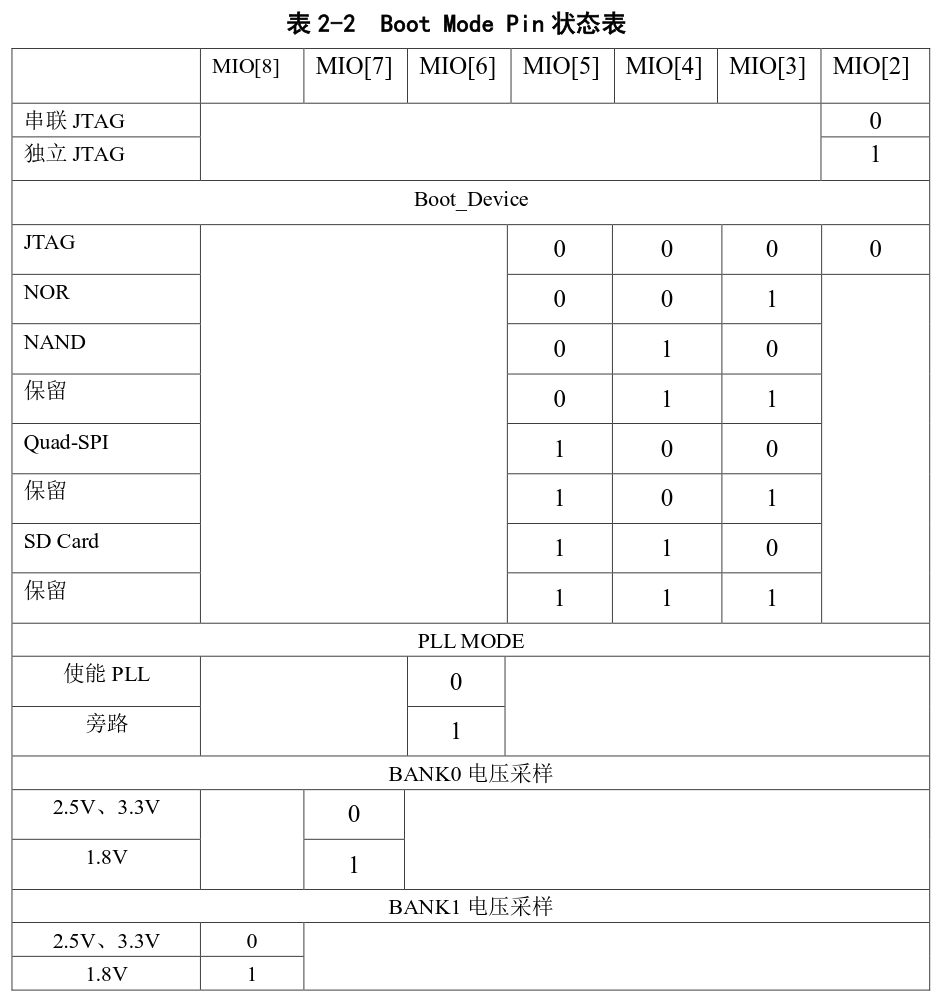

MIO[5:3]的电平状态决定处理器的启动设备,处理器在上电复位引脚PS_POR_B 的上升后的连续 50 个 clk 采样这些引脚的状态。同时,处理器还会对JTAG 模式、MIO BANK 的电压及锁相环工作模式进行配置。表2-2 是Boot Mode Pin 的状态表。

从表 2-1 可以看到,ZYNQ 可从 NOR(32MB Max)、NAND(ONFI1.0接口,1GB Max)、Quad-SPI(256MB Max)、SD (16GB Max)卡启动,NAND FLASH 和 SD 卡不可避免的会有坏块的问题,SD 卡若用来存储其他数据还可能导致误操作擦除启动区数据,因此许多要求可靠性比较高的系统大多选择使用NOR FLASH和Quad-SPI用作启动设备。但从表1-2 可以看出,NOR FLASH几乎占用了 MIO的所有引脚,特别是和高速设备进行了复用;若从 Quad-SPI启动,ARM只给BootRom线性地址模式读取Quad-SPI分配了128Mbit的空间,其它内容由FSBL负责搬运,同时大容量器件的价格较高。因此在选择启动设备时,会遭遇一个兼顾考虑的问题。另外,Xilinx 对启动器件有一定的要求,经过Xilinx验证的启动器件详见AR# 50991。

2.3 启动流程

Zynq 系列器件采用三级启动方式,每级的要求及过程如下。(1) 第0 级:启动 BootROM。

要求:安全启动时,PS 和 PL 均需上电且稳定;普通方式启动时 PS 需上电,PL不需上电,JTAG 配置启动时PS 和PL均需启动。 流程:在上电复位、系统复位或软件复位后,BootROM 根据 BootROM Header 定义的信息执行加载 FSBL 并将控制权交给 FSBL(若选择在内部OCM执行,FSBL不能大于192KB,在 FLASH 直接执行无限制)。

(2)第1 级:FSBL(或用户控制代码)

要求:因为此阶段 PS 要配置 PL,因此 PS 和 PL 均需上电。 流程:FSBL 取得控制权后,根据 VIVADO(或 XPS)的配置对 PS 进行初始化,使用比特流(Bitstream)文件对PL进行配置。然后加载裸机程序或 SSBL并交付控制权。

(3)第2 级:执行裸机程序或 SSBL。

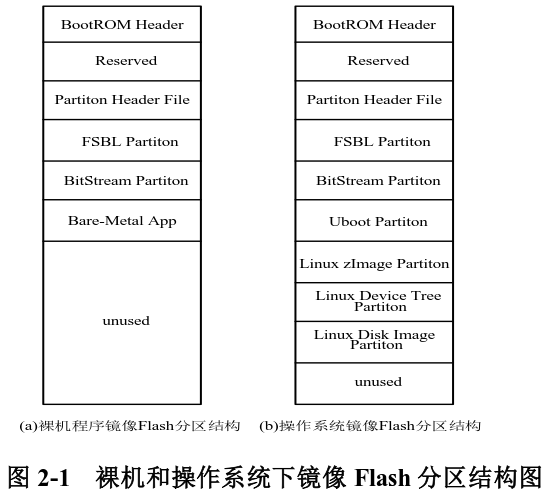

流程:裸机程序直接执行或执行 SSBL(通常是 UBoot),在 UBoot 执行后的加载工作交付 UBoot 完成。 裸机状态下和操作系统状态下的 Flash 镜像文件分区如图2-1 所示,这个镜像文件可通过 Xilinx SDK 里的相关工具制作。