- 列表内容

- 列表内容

- 列表内容

- 列表内容

- 列表内容

- 列表内容

- 列表内容

- 列表内容

- 列表内容

- 列表内容

- 列表内容

- 列表内容

- 列表内容

- 列表内容

- 列表内容

- 列表内容

8086的总线:

1.片总线,芯片内部引出的总线,它是用微处理器构成一个部件(如CPU)或是一个很小的系统时信息传输的通路。各类微处理器的引脚信号即片总线,如8086/8088CPU的地址线、数据线、控制线等即构成该芯片的片总线

2.内总线(I-BUS)又称系统总线,也就是常指的微机总线,它是用于微机系统中各插件之间信息传输的通路。内总线常用的有STD总线、PC总线

3.外总线(E-BUS)又称通信总线,他是微机系统之间,或微机与其他系统之间的信息传输的通路。外总线常用的有RS-232C,RS-4498086的总线周期:至少由4个时钟周期组成,T1,T2,T3,T4。可以在T3和T4之间插入数个Tw等待周期。

- 8086的寄存器:

1. 8个通用寄存器:AX-累加器,BX-基址寄存器,CX-计数寄存器,DX-数据寄存器,SP-堆栈指针寄存器,BP-基址指针寄存器,SI-源变址寄存器,DI-目的变址寄存器

2. IP-指令指针:十六位专用寄存器

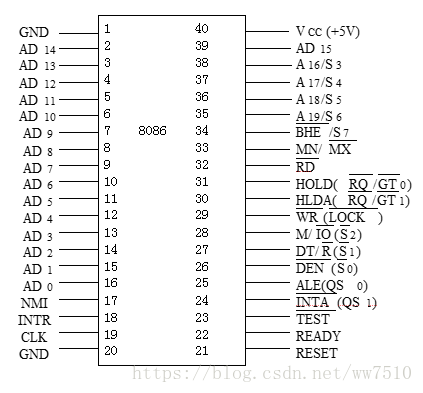

3. FR-标志寄存器:十六位 8086的引脚

1) AD15~AD0为地址/数据总线,T1时用作地址总线的低16位,其他时间用作数据总

2) A19~A16/S6~S3为地址状态总线,T1时用作地址总线高4位,其他时间指示CPU状态信息

3) 34号引脚 #BHE/S7-总线高允许/状态信号,T1时作为高允许信号,#BHE低电平时把读写的8位数据与AD15~AD8联通,与A0结合以决定是高字节工作还是低字节工作。AD0除了传输数据或地址信息还作为低8位数据的选通信号

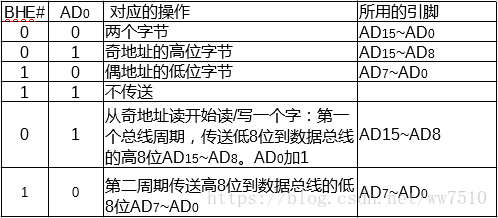

奇地址:最低存储单元地址为奇数——即地址最低位A0=1

偶地址:最低存储单元地址为偶数——即地址最低位A0=0

8086每个周期可以访问16位信息,变量地址为偶地址时,只需一个总线周期。如果变量为奇地址时,则要两个连续总线周期。

8086的存储空间时分成两个512K的存储体,偶存储体和奇存储体。

低8位D7~D0数据总线联接偶存储体,高8位D15~D8联接奇存储体。

偶地址存储时:一个16位字数据,高8位存储在奇存储体,低8位存储在偶存储体。

奇地址存储时相反。

这样在读或写数据时,偶地址存储方式可以在一个总线周期完成读写。

奇地址存储方式读写时则有一个字节交换过程,也就是要用总线的高8位去读写字数据的低8位,再用总线的低8位读写字数据的高8位,需要两个总线周期才能完成一个字数据的读写。74LS138译码器

3个选择输入端:C,B,A

3个使能输入端:G1,G2A#,G2B#

8个输出端:Y0#~Y7#

CBA的组合:000-111分别对应于Y0#~Y7# 8个输出

CPU输出 20位地址A19~A0

CPU与其他部件的信息交换

CPU和内存之间通过数据总线交换数据

CPU和外设之间通过I/O接口交换数据

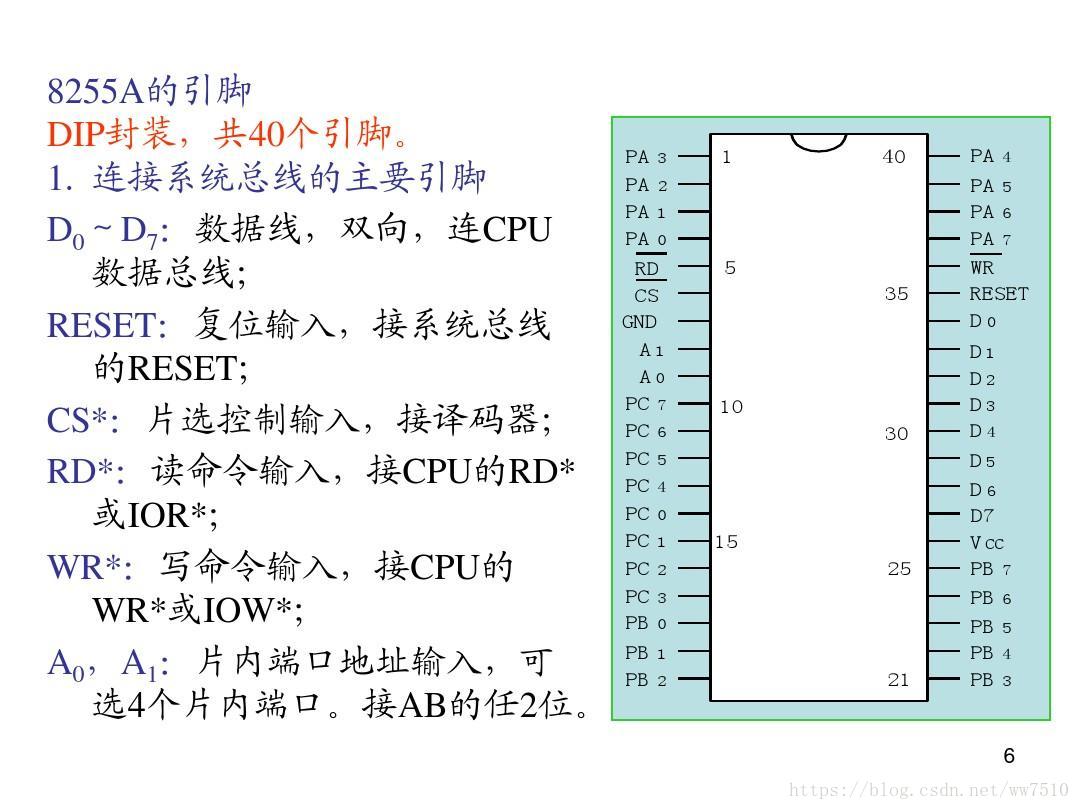

内存和外设之间交换数据的单位???????8255A可编程并行接口芯片

由4部分构成:

(1)数据总线缓冲器

(2)3个8位端口PA,PB和PC

通常PA口和PB口用作输入/输出的数据端口,PC口用作控制和状态信息端口,分为两个4位端口

(3)A组和B组的控制电路

(4)读/写控制逻辑

74LS138的工作方式:3种

(1)方式0:

24.

25. 8259A可编程中断控制器

8259A的主要功能

1. 每片8259A可管理8级优先权中断源,通过8259A的级联,最多可管理64级优先权的中断源。

2. 对任何一级中断源都可单独进行

3. 能向CPU提供可编程的标识码,对于8086/8088 CPU来说就是中断类型码

4. 具有多种中断优先权管理方式,有完全嵌套方式、自动循环方式、特殊循环方式、特殊屏蔽方式和**查询方式**5种

8259A的8个基本组成部分:

(1). 8位中断请求寄存器,用来存放从外设来的中断请求信号IR0~IR7

(2). 8位中断屏蔽寄存器,用来存放CPU送来的屏蔽信号

(3). 8位中断服务寄存器,用来记忆正在处理的中断级别

(4). 优先权判别器,用来管理和识别各个中断源的优先级别