Register寄存器

寄存器是中央处理器的组成部份,可用来暂存指令、数据和位址。通常有通用寄存器,如指令寄存器IR、程序计数器(PC)、累加器(ACC)、堆栈指针寄存器(SP)等,另外还有状态寄存器(标记状态Z、N、V、C)。寄存器最靠近CPU,随取随用,速度最快。

Cache

即高速缓冲存储器,位于CPU与内存之间,容量小但速度快。由于CPU快而内存慢,CPU不存在直接读/写内存的情况,每次读/写内存都要访问Cache。Cache Line是cache与内存同步的最小单位,典型的虚拟内存页面大小为4K,Cache line为32或64字节。Cache中一般保存着CPU刚用过或循环使用的部分数据,当CPU再次使用该部分数据时可从Cache中直接调用,这样就抹平了CPU与内存的速度差。Cache又分为L1、L2、L3(L1、L2一般集成在CPU上)。

理论上L1有着跟寄存器相同的速度,但L1工作在写通过(write-through)模式下时,需要加锁用来同步cache和内存的内容,这段期间L1不能被访问,所以L1就没寄存器快。L2、L3同样需要加锁,并且L2比L1慢,L3比L2慢。

cache下还有一个TLB,TLB是一个内存管理单元用于改进虚拟地址到物理地址转换速度的缓存。

RAM(主要针对DRAM)

即内存,其作用是用于暂存CPU的运算数据,以及与硬盘等外部存储器交换的数据。内存的一个存储周期是从存储器收到有效地址(EA)开始,经过地址译码、驱动,直到被访问的存储单元被读出/写入为止。

简单介绍下CPU访问内存的流程:

1. 找到数据(一般为操作数)地址(或地址的地址)。(地址一般放在通用寄存器内)

2. 将地址送往内存管理单元(MMU),由MMU将虚拟的内存地址翻译成实际的物理地址。

3. 将物理地址送往内存控制器,由控制器进行译码找到对应的存储体。

4. 从对应的存储体读取数据送回给控制器,最后再送回CPU。可以看出内存的工作流程比cache多出许多,每一步都会产生延迟。并且当外围设备(比如磁盘)通过DMA控制器与内存进行数据传输时(走数据总线),会与上面的CPU访问内存发生冲突,此时CPU和DMA就会轮流挪用内存周期,这样CPU访问内存的速度就更慢了。

HardDisk

又称硬盘驱动器,常见的有磁性旋转机械盘和基于闪存的固态硬盘SSD,这里主要讲机械盘,当进行数据存取时,主要的速度影响来自于磁头的寻道时间和盘片的旋转时间,通常需要花费数毫秒的时间。如果是顺序I/O还好,如果是随机I/O,速度将很慢。虽然磁盘内部、操作系统及应用程序都对磁盘进行了缓存优化,但速度还是远远不及内存。

下面是一张磁盘调用栈图(引用Brendan Gregg)

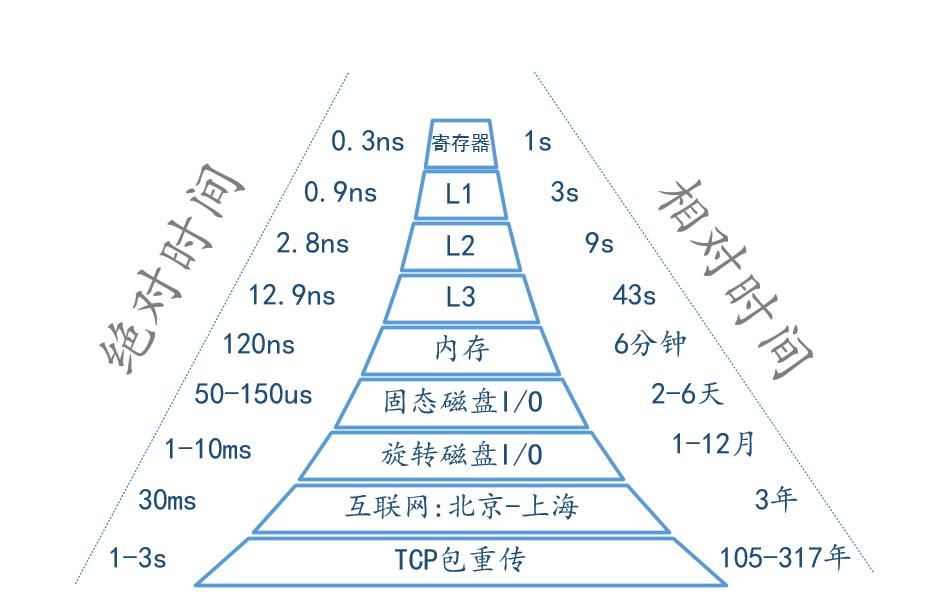

最后以一张图量化系统的各种延时时间(部分数据引用Brendan Gregg)